Page 2

INTRO UCTION

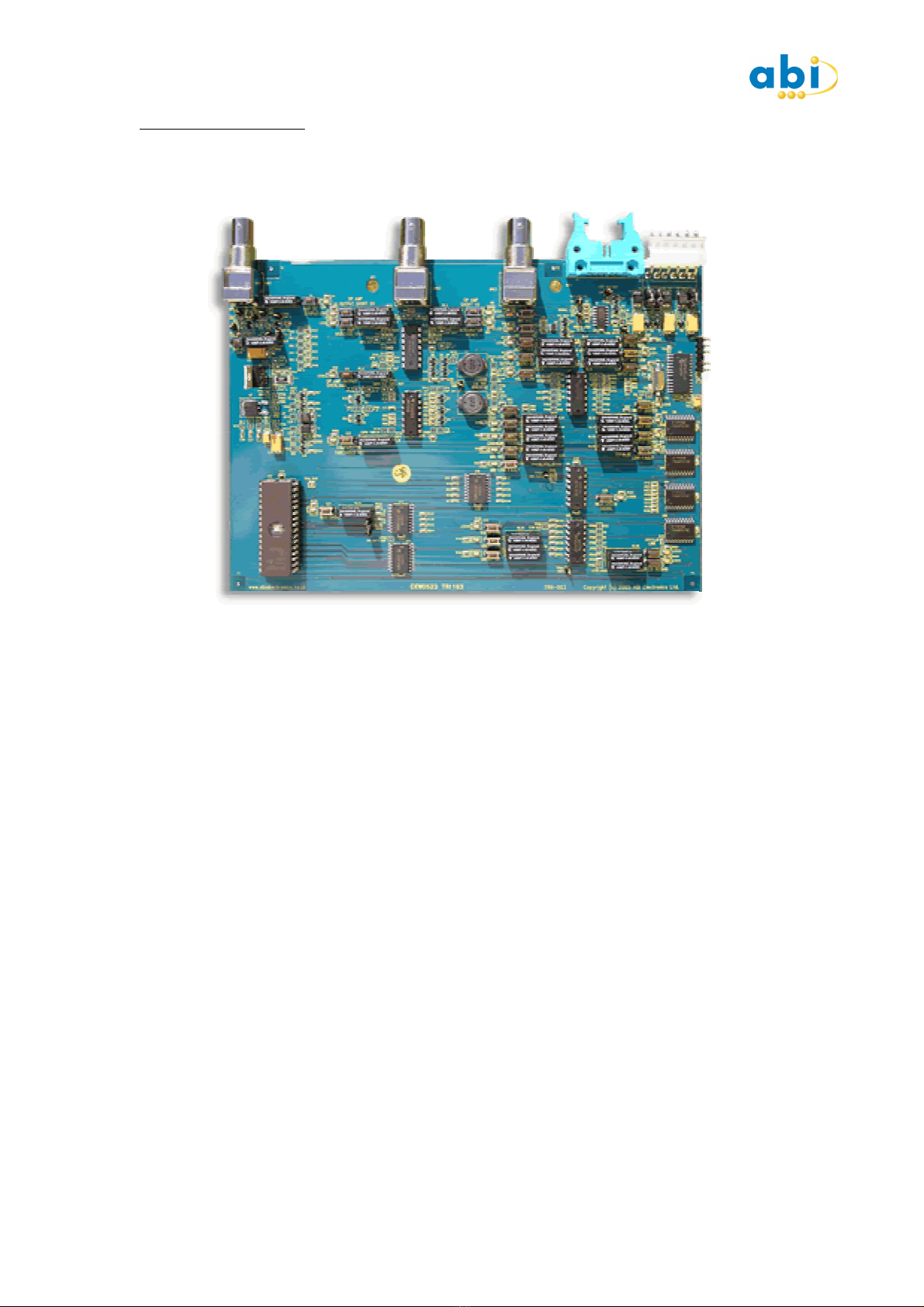

The training board has two uses. It is intended for use as a training aid for both customers

and ABI distributors, and as a sales tool to demonstrate the many features of the

BoardMaster and SYSTEM 8 ranges. We have tried to highlight as many common PCB faults

as possible as well as the common uses of instruments.

Using the training board

As the training board has been designed to serve a dual purpose, it was necessary to

simulate the wide range of situations encountered when diagnosing board faults, as well as

demonstrating the applications and ease of use of ABI products. The training board therefore

contains a wide range of different types of components, with switchable fault conditions,

which can be used with most of the ABI test and fault-finding instruments.

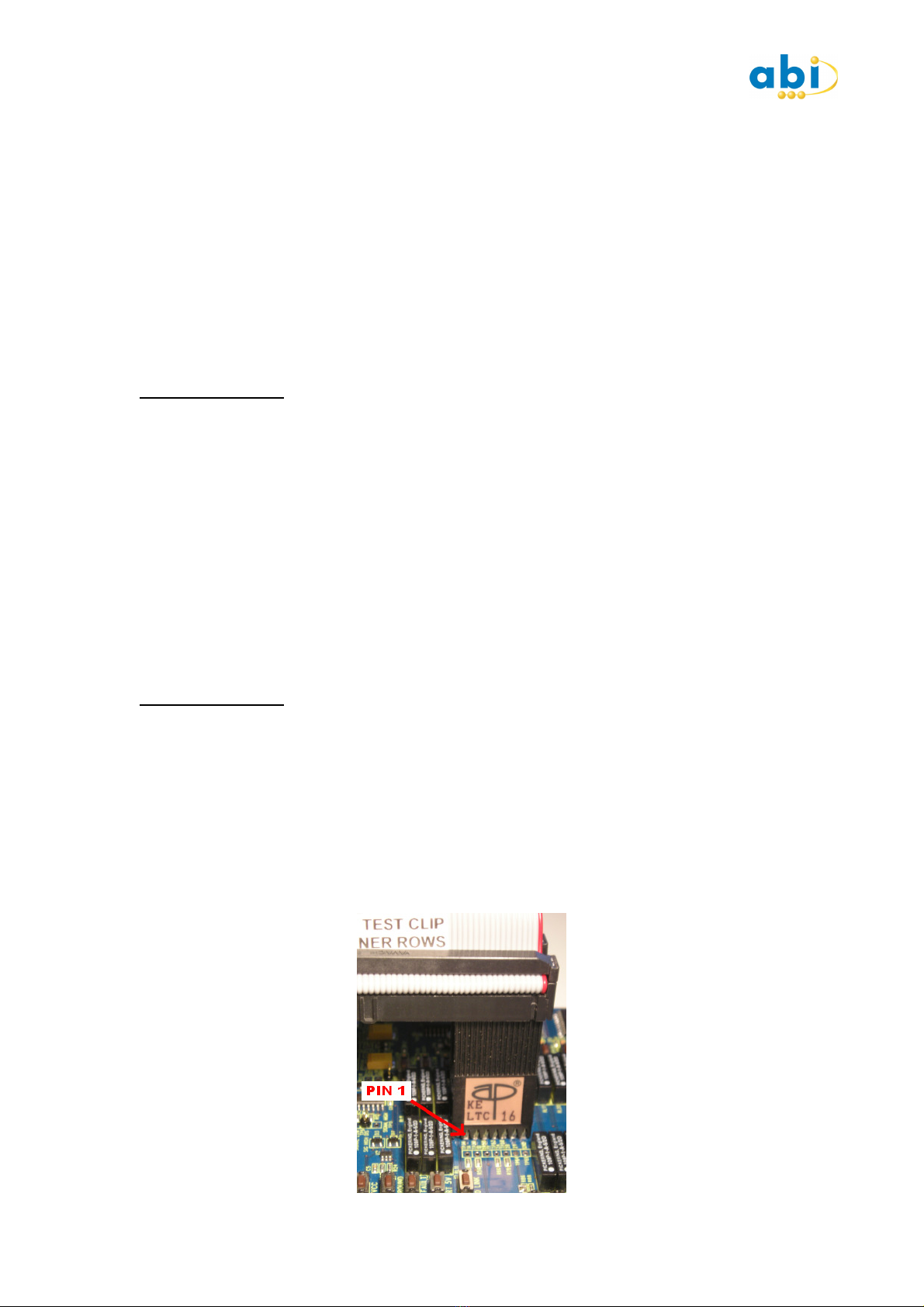

The board is divided into three distinct sections. A digital section with various digital ICs

including a microprocessor, memory and EPROM) is included to demonstrate the capabilities

of our IC Test Solution instruments. An analogue section contains analogue components to

demonstrate the functions of our Analogue V-I and Analogue IC Test Solutions. Finally, a

discrete section contains uncommitted discrete components to allow a more detailed analysis

of V-I and analogue testing. Products that combine different test techniques, such as the

Diagnostic Solution and the BoardMaster 8000 PLUS, can be used on the entire board.

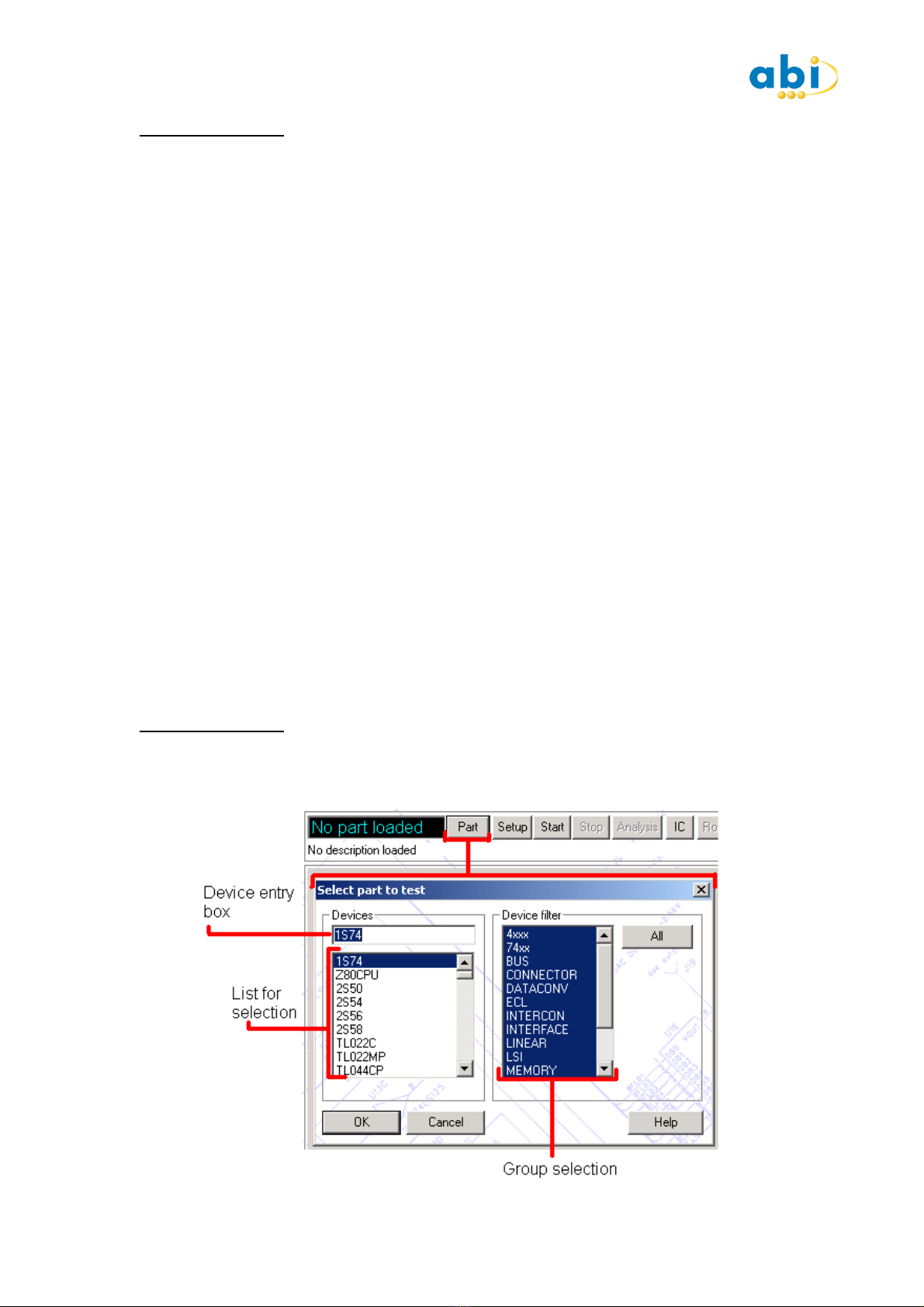

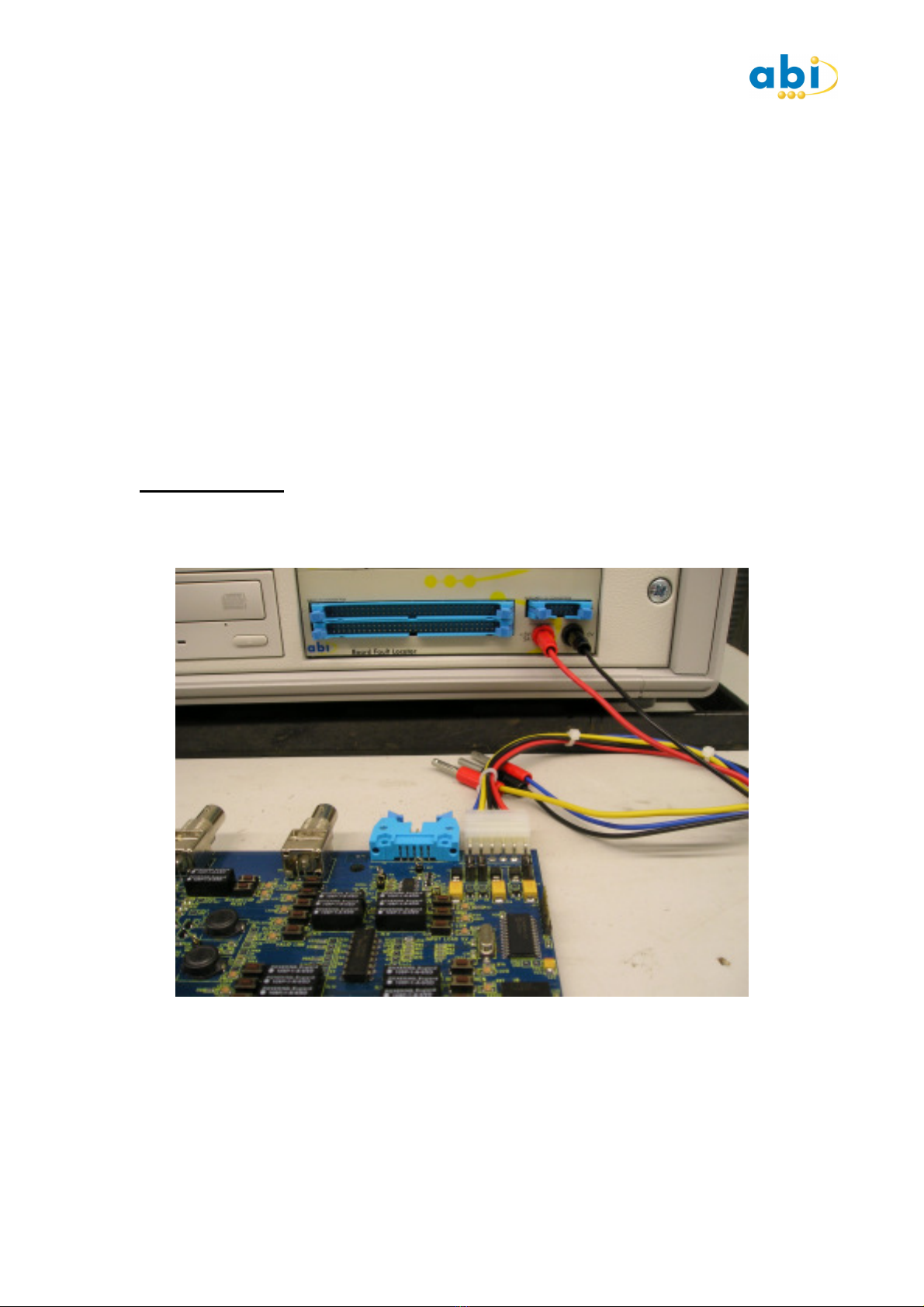

The board can be used in two ways. The relevant SYSTEM 8 instrument e.g. the IC Tester)

can be opened manually and configured to test a particular component on the training board.

The switches for the component can be used to simulate a fault condition, by reference to the

circuit diagram and/or this manual. The results can then be analysed to gain an

understanding of the operation of the system. Alternatively, the training board package

contains a CD-ROM with a test sequence file TestFlow), which can be used to guide the

operator through a sequence of tests on the board. All instruments are opened and

configured automatically, leaving the operator free to concentrate on analysing the results.

Brief instructions and explanations are also shown on screen. The disk also contains all

necessary data files e.g. digital pattern files, V-I data files etc.) which are required by some

of the test steps. We suggest that you work through this sequence file in order to gain a

thorough understanding of the system. You can also select individual steps in the sequence,

if you wish to repeat a test.

Using TestFlow

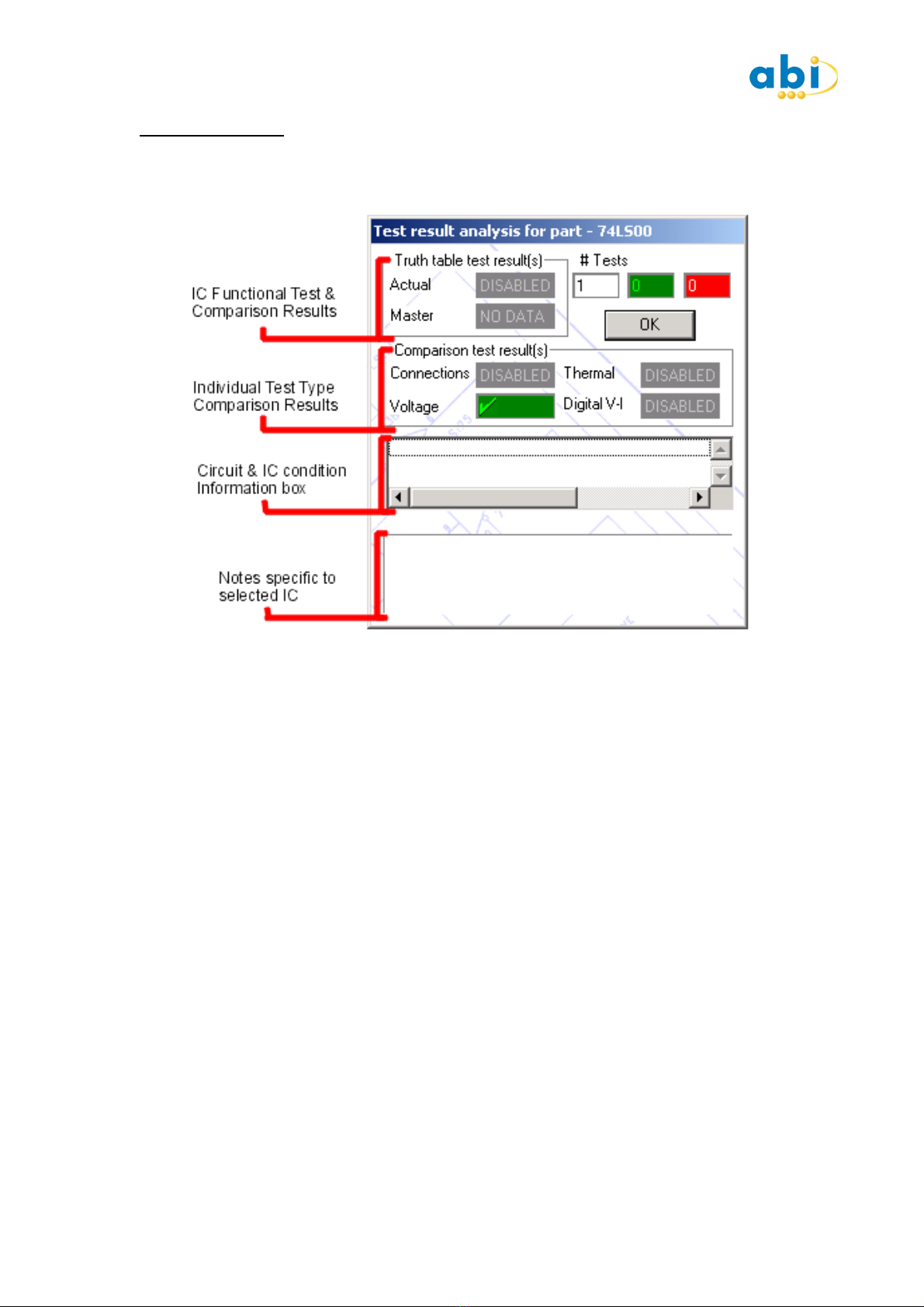

ACTION

On each step in the Test Instruction it will tell you what you need to do to carry out each test

step. Instructions will include component location, switch settings and instrument operations.

Most steps are independent of each other so you can jump to a specific test if you wish.

In normal operation click NEXT button to continue.

ESCRIPTION

The Test Instruction describes the operation being carried out by the equipment and you.

Each step in the TestFlow is setup to allow information to be easily acccessed without

cluttering the screen. Each step in the TestFlow can show valid circuit and device conditions

and also fault conditions.

The TestFlow system) is originally intended to highlight fault conditions with a failure or bad

indication. For the purposes of training the TestFlow for the Training board will indicate a

pass or good comparison if the correct action has been carried out by the operator, indicating

that the particular point being covered in the TestFlow step has been correctly completed.