ACXx429-32 Hardware Manual

1 INTRODUCTION

1.1 General

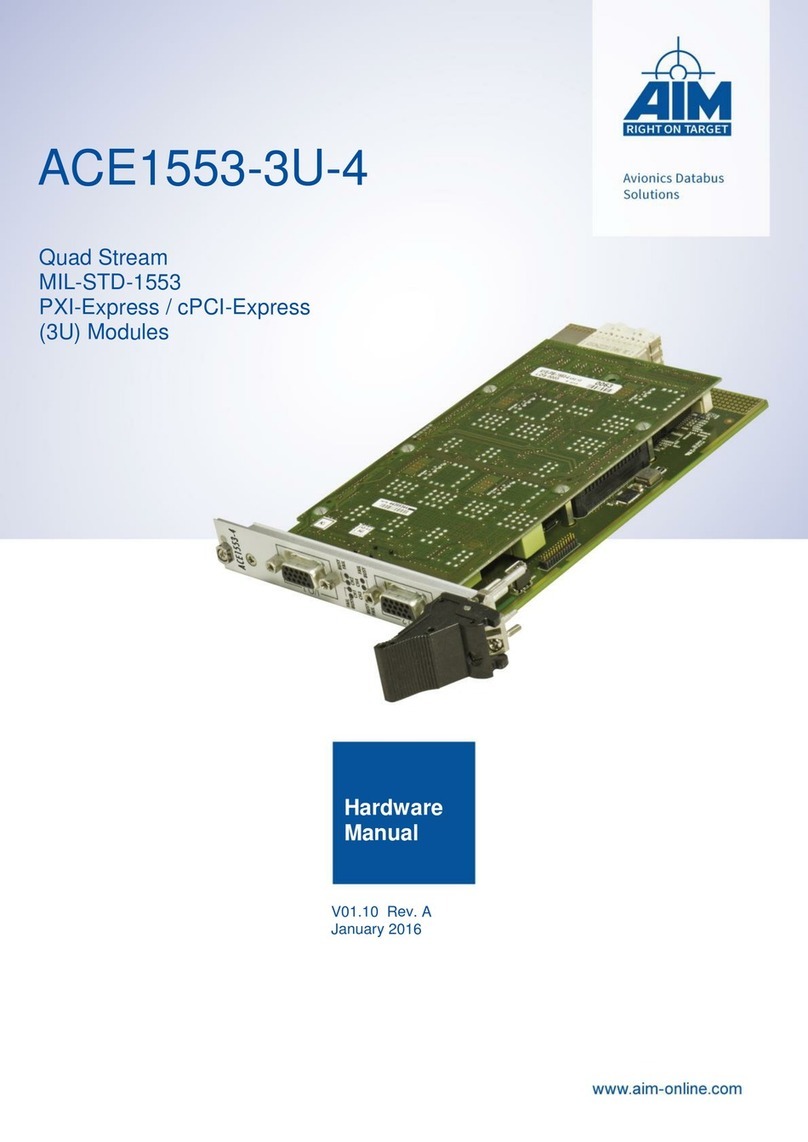

This document comprises the Hardware User’s Manual for the PXI ACXx429-3U-32

which implements 32 transmit and receive ARINC-429 channels, based on the PCI-

Express communication standard. The document covers the hardware installation,

board connections, technical data and a general description of the hardware

architecture. For programming information please refer to the documents listed in the

'Applicable Documents' section.

The ACXx429-3U-32 is a member of AIM’s new family of CompactPCI /PXI (3U)

modules for analysis, simulation, monitoring and testing of ARINC429 channels

providing 32 channels on a 3U module form factor.

Each channel is software configurable in runtime as a fixed amplitude Transmitter or

Receiver.

On the transmit channels, the ACXx429 acts as an autonomously operating bus traffic

simulator, supporting multiple modes of transmission sequencing. Full error injection

capabilities are available, whereby the error injection is programmable individually for

each channel and label. For special transmission operating modes the parity bit can be

used alternatively as an additional data bit. The rise and fall time of the bus signals are

individually programmable by software for each transmit channel.

For the receive channels, the ACXx429 provides an advanced monitor and analyser

function with unique on-board error detection, triggering and filtering capabilities.

Monitor and analyser functions are available concurrently and independent from each

other. The hardware architecture provides resources to guarantee that the performance

of one function is not affected by the current load of the other function. The rise and fall

times of the bus signals are individually programmable for each receive channel. To

adapt to different transmit speeds, the transmission rate can be varied in discrete steps

between approximately 90 and 120Kbits on the high speed bus and between 11.5 and

16.0 on the low speed lines.

The hardware architecture provides ample resources (i.e. processing capability and

memory) to guarantee, that all specified interface functions are available concurrently

and to full performance specifications.

The advanced architecture uses a special processor for the ARINC-429 stream. A

powerful Memory Arbiter is implemented in a Field Programmable Gate Array (FPGA).

This FPGA supports both, the interface to the application and driver software tasks

running on the host computer and assists the communication for data transfer. This

feature expands the capability of the ACXx429 module to that of a high level instrument.

To fulfill the real-time requirements of a typical avionic type databus system, a high

performance 32bit RISC processor (BIP) is implemented.