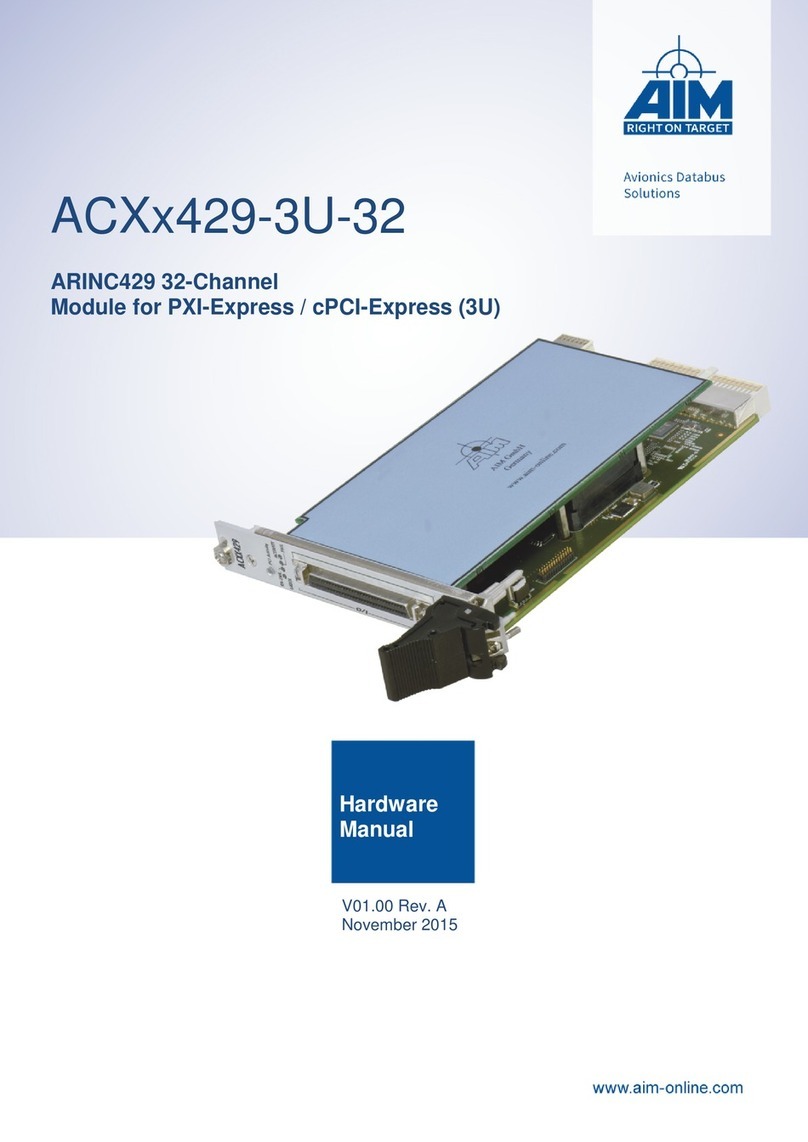

ACE1553-3U-4 Hardware Manual

TABLE OF CONTENTS

Section Title Page

1INTRODUCTION .....................................................................................................1

General ...............................................................................................................11.1 How This Manual is Organized............................................................................21.2

Applicable Documents.........................................................................................21.3

1.3.1 Industry Documents ........................................................................................2

1.3.2 Product Specific AIM Documents....................................................................2

2INSTALLATION.......................................................................................................3

Preparation and Precaution for Installation..........................................................3

2.1

Installation Instructions........................................................................................32.2 Connecting to other Devices................................................................................42.3

2.3.1 MIL-STD-1553-A/B Dual Channel Interface Connector ...................................5

2.3.2 General Purpose I/O Connections...................................................................5

Front Panel LEDs................................................................................................62.4

3STRUCTURE OF THE ACE1553-3U-4....................................................................7

PCI-Express Interface and BIU-I/O FPGA ...........................................................83.1

3.1.1 Global RAM Interface and Arbitration..............................................................8

3.1.2 Boot Function..................................................................................................8

3.1.3 Controller for SPI-Flash update programming .................................................8

3.1.4 MIL-STD-1553 Encoder ..................................................................................8

3.1.5 MIL-STD-1553 Decoder ..................................................................................8

3.1.6 IRIG-B Encoder/Decoder and Timecode Processor (TCP)..............................9

3.1.7 System & Maintenance Controller / RS232 Maintenance Interface..................9

3.1.8 External Trigger Inputs and Outputs................................................................9

3.1.9 User programmable Discrete I/O (GPIO).......................................................10

Global RAM.......................................................................................................113.2

BIU Section .......................................................................................................113.3 Physical Bus Interface with four Dual Redundant MIL-STD-1553B Channels....123.4 IRIG- and Time Code Section............................................................................143.5

3.5.1 Time Code Encoder/Decoder........................................................................14

3.5.2 Time Tag Methods ........................................................................................14

General Purpose Discrete Inputs/Outputs (GPIO) .............................................153.6 PXIe / cPCIe - Connector Pin Assignment.........................................................153.7

4PXI-EXPRESS INSTRUMENTATION BUS ...........................................................17

About the PXIe Standard...................................................................................17

4.1

4.1.1 Backplane Trigger Lines................................................................................18

4.1.2 System Reference Clock (10MHz) ................................................................20

4.1.3 Star Trigger...................................................................................................21

5TECHNICAL DATA ...............................................................................................23

6NOTES ..................................................................................................................27

Acronyms ..........................................................................................................276.1