Altera Stratix III Instruction Manual

Other Altera Microcontroller manuals

Altera

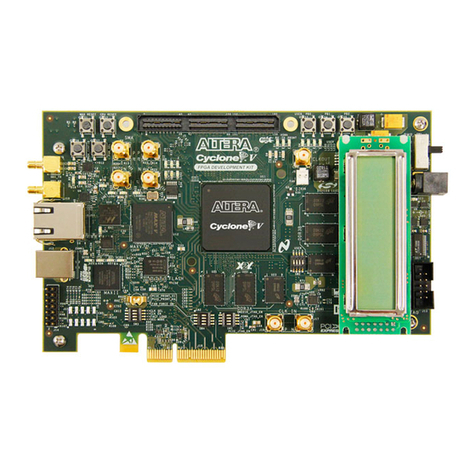

Altera Cyclone V GX Starter Kit User manual

Altera

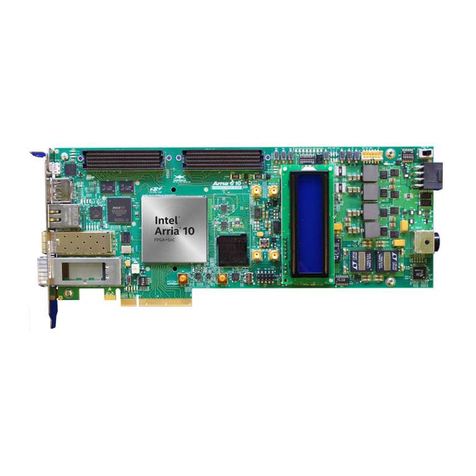

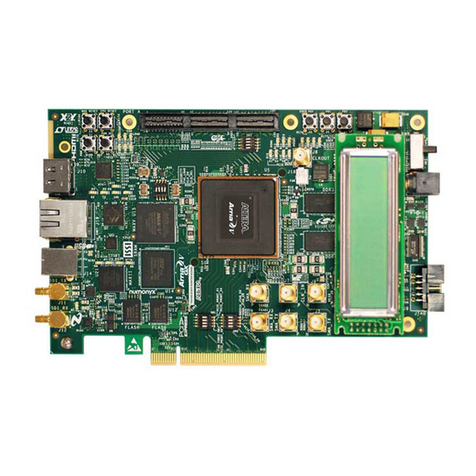

Altera Arria 10 SoC User manual

Altera

Altera Stratix 10 GX FPGA User manual

Altera

Altera Cyclone V SoC User manual

Altera

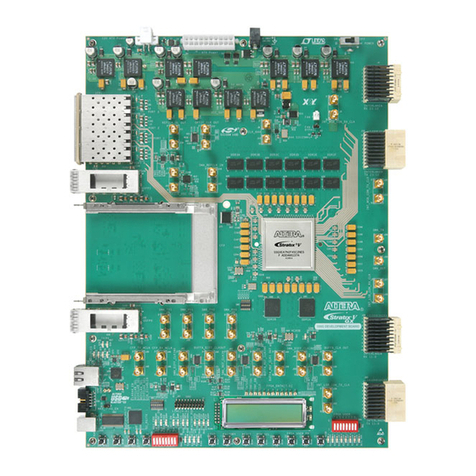

Altera Stratix III User manual

Altera

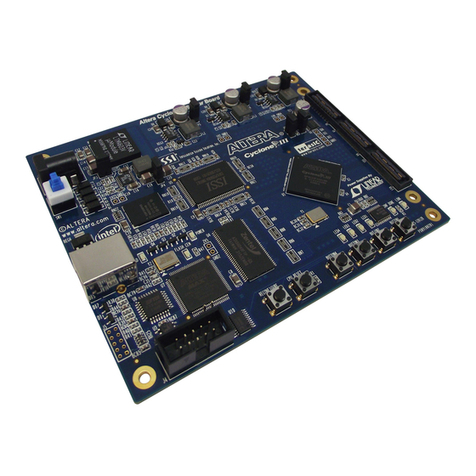

Altera Cyclone III User manual

Altera

Altera Excalibur APEX 20K200E User manual

Altera

Altera Cyclone III User manual

Altera

Altera Arria II GX FPGA User manual

Altera

Altera DE5-NET User manual

Altera

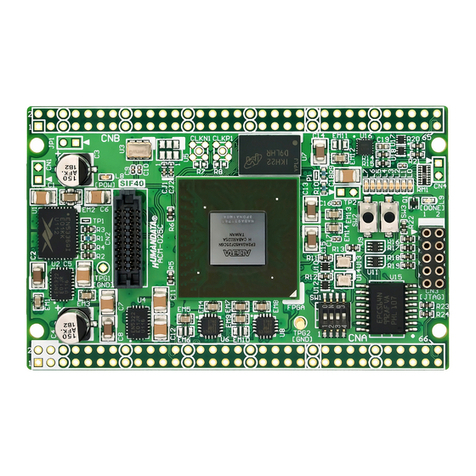

Altera MAX 10 series User manual

Altera

Altera CPLD User manual

Altera

Altera Cyclone V GX FPGA User manual

Altera

Altera Arria 10 FPGA User manual

Altera

Altera DSP Development Kit User manual

Altera

Altera Stratix V GX 100G User manual

Altera

Altera Cyclone V User manual

Altera

Altera Stratix III Application guide

Altera

Altera DE1-SoC User manual

Altera

Altera Arria V GX FPGA User manual

Popular Microcontroller manuals by other brands

AMS

AMS AS7261 Demo Kit user guide

Novatek

Novatek NT6861 manual

Espressif Systems

Espressif Systems ESP8266 SDK AT Instruction Set

Nuvoton

Nuvoton ISD61S00 ChipCorder Design guide

STMicrolectronics

STMicrolectronics ST7 Assembler Linker user manual

Texas Instruments

Texas Instruments Chipcon CC2420DK user manual

Texas Instruments

Texas Instruments TMS320F2837 D Series Workshop Guide and Lab Manual

CYPRES

CYPRES CY14NVSRAMKIT-001 user guide

Texas Instruments

Texas Instruments INA-DUAL-2AMP-EVM user guide

Espressif Systems

Espressif Systems ESP8266EX Programming guide

Abov

Abov AC33M8128L user manual

Laird

Laird BL654PA user guide