© 2011 Advanced Micro Devices, Inc. AMD RX881 Databook 1.40

Proprietary Table of Contents-1

Table of Contents

Chapter 1: Overview

1.1 Introducing the RX881........................................................................................................................................................1-1

1.2 RX881 Features...................................................................................................................................................................1-1

1.2.1 CPU HyperTransport™ Interface.........................................................................................................................1-1

1.2.2 PCI Express® Interface........................................................................................................................................1-1

1.2.3 A-Link Express II Interface..................................................................................................................................1-2

1.2.4 System Clocks ......................................................................................................................................................1-2

1.2.5 Power Management Features ...............................................................................................................................1-2

1.2.6 PC Design Guide Compliance..............................................................................................................................1-2

1.2.7 Test Capability Features.......................................................................................................................................1-2

1.2.8 Packaging .............................................................................................................................................................1-3

1.3 Software Features................................................................................................................................................................1-3

1.4 Branding Diagram...............................................................................................................................................................1-3

1.5 Conventions and Notations.................................................................................................................................................1-4

1.5.1 Pin Names.............................................................................................................................................................1-4

1.5.2 Pin Types..............................................................................................................................................................1-4

1.5.3 Numeric Representation.......................................................................................................................................1-4

1.5.4 Register Field........................................................................................................................................................1-4

1.5.5 Hyperlinks ............................................................................................................................................................1-4

1.5.6 Acronyms and Abbreviations...............................................................................................................................1-4

Chapter 2: Functional Descriptions

2.1 Host Interface......................................................................................................................................................................2-1

2.2 Clock Generation ................................................................................................................................................................2-3

Chapter 3: Pin Descriptions and Strap Options

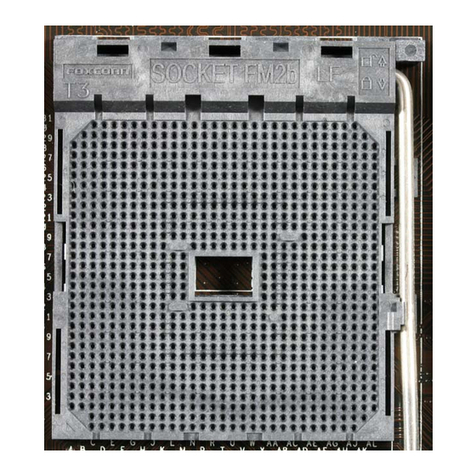

3.1 RX881 Pin Assignment Top View......................................................................................................................................3-2

3.2 Interface Block Diagram.....................................................................................................................................................3-4

3.3 CPU HyperTransport™ Interface .......................................................................................................................................3-5

3.4 PCI Express® Interfaces.....................................................................................................................................................3-5

3.4.1 1 x 16 Lane Interface for External Graphics........................................................................................................3-5

3.4.2 A-Link Express II Interface for Southbridge........................................................................................................3-5

3.4.3 6 x 1 Lane Interface for General Purpose External Devices...............................................................................3-6

3.4.4 Miscellaneous PCI Express® Signals ..................................................................................................................3-6

3.5 Clock Interface....................................................................................................................................................................3-6

3.6 Power Management Pins....................................................................................................................................................3-7

3.7 Miscellaneous Pins..............................................................................................................................................................3-7

3.8 Power Pins...........................................................................................................................................................................3-8

3.9 Ground Pins.........................................................................................................................................................................3-9

3.10 Strapping Options .............................................................................................................................................................3-9

Chapter 4: Timing Specifications

4.1 HyperTransport™ Bus Timing ...........................................................................................................................................4-1

4.2 HyperTransport™ Reference Clock Timing Parameters....................................................................................................4-1

4.3 PCI Express® Differential Clock AC Specifications .........................................................................................................4-2

4.4 Power Rail Power-up Sequence..........................................................................................................................................4-2