CAES NOEL-PF-EX User manual

RISC-V Processor

NOEL-PF-EX

NOEL-PF-EX-UM

Jul 2022, Version 2.0

Cobham Gaisler AB

Kungsgatan | SE-411 19 | Goteborg | Sweden

+46 31 7758650 | www.caes.com/gaisler

USER MANUAL JUL 2022

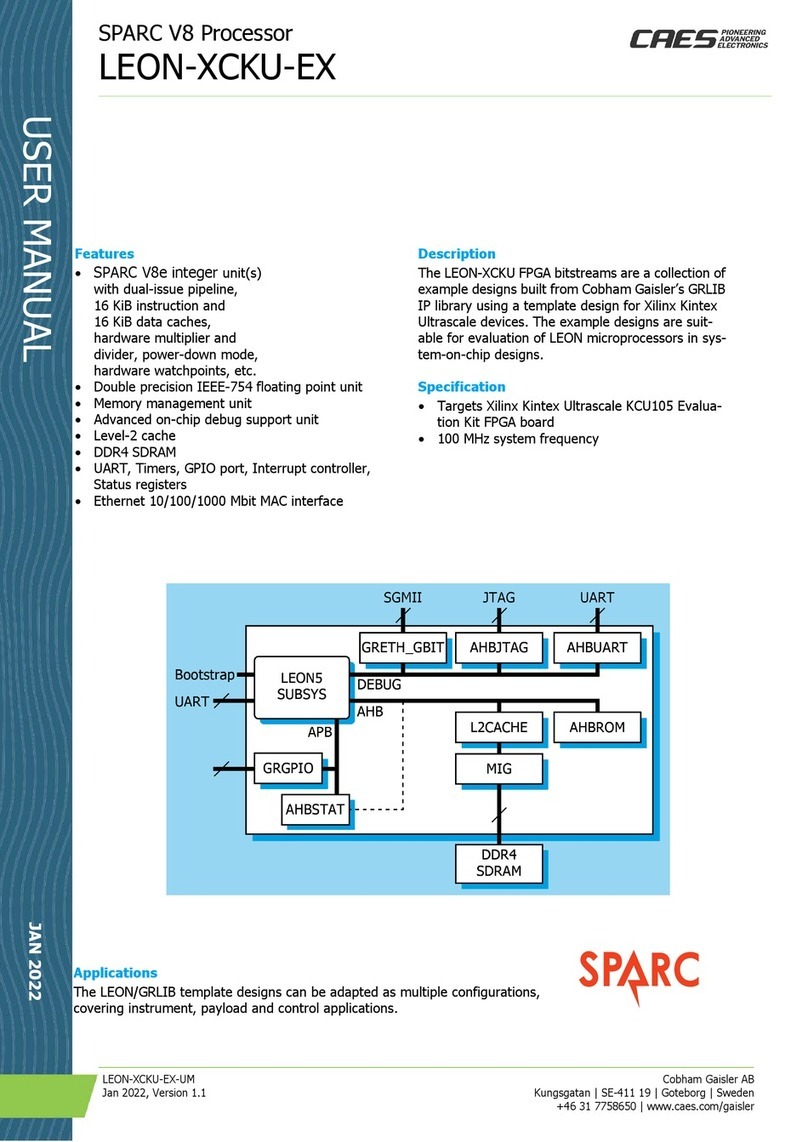

Features

•RISC-V NOEL-V processor with 64-bit architec-

ture 16 KiB instruction and 16 KiB data caches,

memory management unit, hardware multiplier

and divider, in single and multi-core configura-

tions

• RISC-V standard Platform-Level Interrupt Con-

troller

• RISC-V standard PMP

• RISC-V standard debug support

• Level-2 cache

• DDR4 SDRAM

• UART, Timers, GPIO port, Status registers

• Ethernet 10/100/1000 Mbit MAC interface

Description

The NOEL-PF FPGA bitstreams are a collection of

example designs built from Cobham Gaisler’s GRLIB

IP library using a template design for Microsemi

PolarFire devices. The example designs are suitable

for evaluation of NOEL microprocessors in system-

on-chip designs.

Specification

• Targets Microsemi MPF300-SPLASH-KIT FPGA-

board

Applications

The NOEL/GRLIB template designs can be adapted as multiple configurations,

covering instrument, payload and control applications.

NOEL-PF-EX-UM

Jul 2022, Version 2.0 2

NOEL-PF-EX

Cobham Gaisler AB

Kungsgatan | SE-411 19 | Goteborg | Sweden

+46 31 7758650 | www.caes.com/gaisler

Table of contents

1 Introduction.............................................................................................................................. 3

1.1 Scope ....................................................................................................................................................... 3

1.2 Document revision history ...................................................................................................................... 3

1.3 Reference documents .............................................................................................................................. 3

2 Example designs ...................................................................................................................... 4

2.1 Overview ................................................................................................................................................. 4

2.2 Configurations ......................................................................................................................................... 5

3 Architecture.............................................................................................................................. 6

3.1 Cores........................................................................................................................................................ 6

3.2 Interrupts ................................................................................................................................................. 6

3.3 Memory map ........................................................................................................................................... 6

3.4 IP core documentation............................................................................................................................. 8

3.5 Signals ..................................................................................................................................................... 9

3.6 Resource utilization................................................................................................................................. 9

4 Working with the board.......................................................................................................... 10

4.1 Prerequisites .......................................................................................................................................... 10

4.2 Programming the FPGA device and connecting with GRMON3 ......................................................... 10

4.3 Support .................................................................................................................................................. 10

5 Ordering information ............................................................................................................. 11

NOEL-PF-EX-UM

Jul 2022, Version 2.0 3

NOEL-PF-EX

Cobham Gaisler AB

Kungsgatan | SE-411 19 | Goteborg | Sweden

+46 31 7758650 | www.caes.com/gaisler

1 Introduction

1.1 Scope

The NOEL line of processors and the GRLIB IP library has support for Microsemi PolarFire devices.

This support consists of a techmap layer that wraps specific technology elements such as memory

macros and pads. GRLIB also contains a template designs for developments boards such as the

Microsemi MPF300-SPLASH-KIT and infrastructure that automatically builds project files for

Microsemi Libero and Synopsys Synplify Premier.

This document describes ready-made FPGA configurations (bitstreams) that have been built from a

GRLIB template design.

More information about the NOEL-V processor is available at www.gaisler.com/NOEL-V

1.2 Document revision history

1.3 Reference documents

[AMBA] AMBATM Specification, Rev 2.0, ARM IHI 0011A, 13 May 1999, Issue A, first release,

ARM Limited

[GRLIB] GRLIB IP Library User's Manual, Cobham Gaisler, www.Cobham.com/gaisler

[GRIP] GRLIB IP Core User's Manual, Cobham Gaisler, www.Cobham.com/gaisler

[QSG] NOEL-PF-EX Quick Start Guide, NOEL-PF-EX-QSG, www.gaisler.com/NOEL-PF

Table 1. Change record

Version Date Note

1.0 2020 December First issue

1.1 2022 January Added H extension to EX1.Added EX4.

2.0 2022 July Updated example configurations

NOEL-PF-EX-UM

Jul 2022, Version 2.0 4

Cobham Gaisler AB

Kungsgatan | SE-411 19 | Goteborg | Sweden

+46 31 7758650 | www.caes.com/gaisler

NOEL-PF-EX

2 Example designs

2.1 Overview

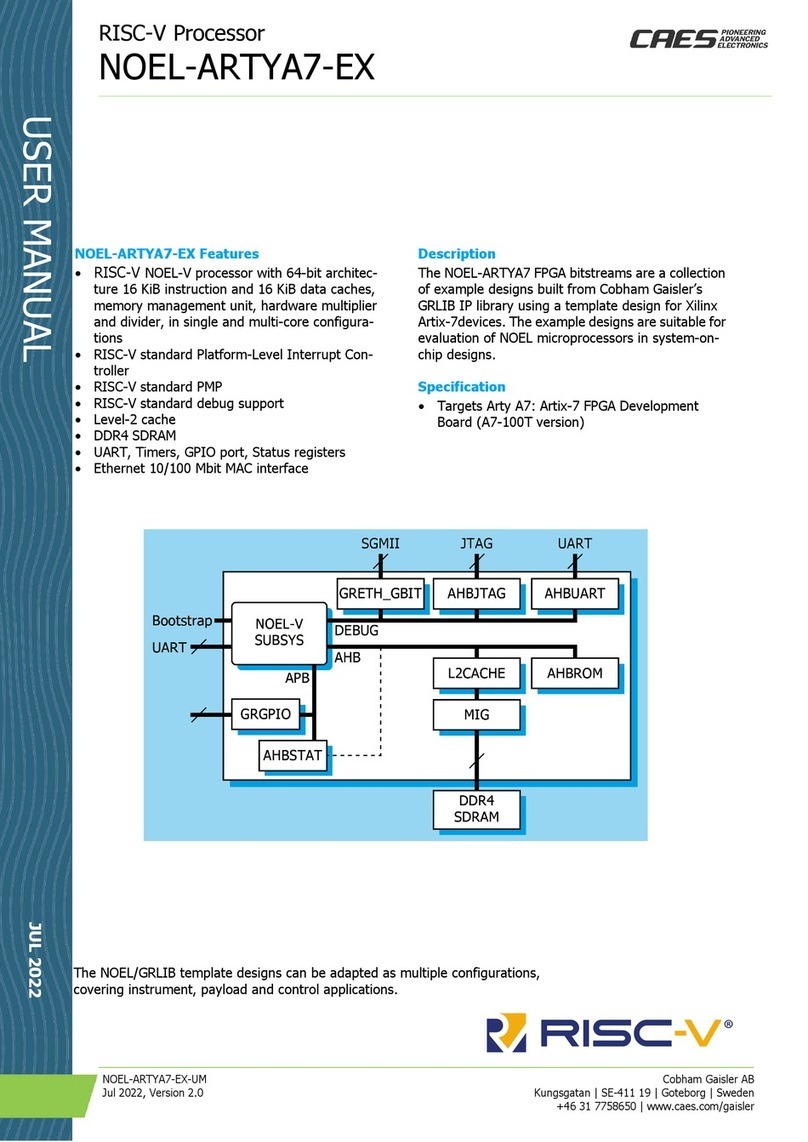

The NOEL-PF-EX example designs are based on a common architecture. The architecture is centered

around the AMBA [AMBA] Advanced High-speed Bus (AHB), to which the processor(s) and other

high-bandwidth units are connected. Low-bandwidth units are connected to the AMBA Advanced

Peripheral Bus (APB) which is accessed through an AHB to APB bridge. The architecture for the

basic design is shown in figure 1. Multi-core configurations are also available.

The full NOEL-PF architecture includes the following modules:

• NOEL-V RV32 with 16 KiB instruction cache and 16 KiB data cache.

• Debug Support Unit with UART and JTAG Debug Links

• Level-2 cache controller

• Microsemi FDDR4 SDRAM controller

• Timer unit with two 32-bit timers

• Platform-Level Interrupt Controller

• UART with FIFO and separate baud rate generator

• General purpose I/O port (GPIO).

• AMBA AHB status register

The GRLIB IP library contains a template design that has been used as the base for NOEL-PF-EX

designs. The template design can easily be extended to add additional GRLIB IP library IP cores such

as:

• Memory controllers with EDAC

• SpaceWire links with CRC support and hardware RMAP target

• SpaceFibre links

• Mil-Std-1553 BC/BM/RT

A full list of GRLIB IP library components can be found in [GRIP]. The GRLIB user’s manual is

available on-line [GRLIB].

Figure 1. Architectural block diagram of NOEL-PF-EX

NOEL-PF-EX-UM

Jul 2022, Version 2.0 5

NOEL-PF-EX

Cobham Gaisler AB

Kungsgatan | SE-411 19 | Goteborg | Sweden

+46 31 7758650 | www.caes.com/gaisler

2.2 Configurations

Table 2 below lists the NOEL-PF-EX example configurations. The bitstreams with example designs

are intended to cover a wide range of application scenarios. The bitstreams are available for download

from https://gaisler.com/NOEL-PF

Note: The configurations above are examples on how to use the GRLIB IP cores on PolarFire. All IP

cores have several configuration parameters and are individually configurable.

Note: The NOEL-V processor can be configured in several different standard configurations, includ-

ing more RV64 variants, the configurations are listed at https://www.gaisler.com/NOEL-V

Note: While software may report that fault-tolerance is enabled for the example designs, the bit-

streams are not suitable for use in harsh environments.

Table 2. Example configurations

Configuration name MC32L-SC MC32-SC GP32-SC GP32F-SC GP64F-SC

PolarFire Device MPF300T MPF300T MPF300T MPF300T MPF300T

Processor NOEL-V NOEL-V NOEL-V NOEL-V NOEL-V

RISC-V extensions* RV32-IMA RV32-

IMACFD

RV32-

IMACHFD

RV32-

IMCAHFD

RV64-

IMCAHFD

Memory Management Unit

(MMU)

No No yes Yes Yes

Number of processor cores 1 1 1 1 1

Frequency 50 MHz 50 MHz 50 MHz 50 MHz 50 MHz

Level-1 cache 8+8 KiB 8+8 KiB 16+16 KiB 16+16 KiB 16+16 KiB

Hardware multiply÷ Yes Yes Yes Yes Yes

Floating Point Unit No nanoFPU nanoFPU GRFPUnv GRFPUnv

Physical Memory Protec-

tion (PMP)

Yes Yes No Yes Yes

Level-2 cache Yes Yes Yes Yes Yes

UART Debug Link Yes Yes Yes Yes Yes

JTAG Debug Link Yes Yes Yes Yes Yes

Memory Controller Microsemi

FDDR4

Microsemi

FDDR4

Microsemi

FDDR4

Microsemi

FDDR4

Microsemi

FDDR4

Standard peripherals Yes Yes Yes Yes Yes

**Parts of the Bit manipulation and Encryption RISC-V extensions are also

included. See NOEL-V section in GRLIB IP Core User's Manual for more

details

NOEL-PF-EX-UM

Jul 2022, Version 2.0 6

Cobham Gaisler AB

Kungsgatan | SE-411 19 | Goteborg | Sweden

+46 31 7758650 | www.caes.com/gaisler

NOEL-PF-EX

3 Architecture

3.1 Cores

The architecture is based on cores from the GRLIB IP library. The vendor and device identifiers for

each core can be extracted from the plug & play information. The used IP cores are listed in table 3.

3.2 Interrupts

The NOEL-PF-EX example designs use the same interrupt assignment for all configurations. See the

description of the individual cores for how and when the interrupts are raised. All interrupts are han-

dled by the interrupt controller and forwarded to the processor.

3.3 Memory map

The example designs use the same memory map for all standard configurations. The memory map

shown in table 5 is based on the AMBA AHB address space. An access to addresses outside the

Table 3. Used IP cores

Core Function Vendor Device

AHBCTRL AHB Arbiter & Decoder 0x01 -

APBCTRL AHB/APB Bridge 0x01 0x006

NOEL-V NOEL-V RISC-V 32-bit processor 0x01 0xBD

RVDM RISC-V Debug Module 0x01 0xBE

AHBUART Serial/AHB debug interface 0x01 0x007

AHBJTAG JTAG/AHB debug interface 0x01 0x01C

AHBSTAT AHB failing address register 0x01 0x052

APBUART 8-bit UART 0x01 0x00C

GPTIMER Modular timer unit with watchdog 0x01 0x011

GRGPIO General purpose I/O port 0x01 0x01A

L2CACHE Level-2 Cache Controller 0x01 0x04B

PolarFire FDDR4 PolarFire FDDR4 controller - with GRLIB wrapper 0xAC 0x00C

Table 4. Interrupt assignment

Core Interrupt Comment

AHBSTAT 4

APBUART 1

GPTIMER 2, 3

NOEL-PF-EX-UM

Jul 2022, Version 2.0 7

NOEL-PF-EX

Cobham Gaisler AB

Kungsgatan | SE-411 19 | Goteborg | Sweden

+46 31 7758650 | www.caes.com/gaisler

ranges will receive an AHB error response. The detailed register layout is defined in the description of

each individual core.

Table 5. AMBA AHB address range

Core Address range Area

L2CACHE

/ PFDDR4

0x00000000 - 0x3FFFFFFF DDR4 SDRAM area

AHBROM 0xC0000000 - 0xC001FFFF Registers

CLINT 0xE0000000 - 0xE000FFFF Registers

PLIC 0xF8000000 - 0xFBFFFFFF Registers

GPTIMER 0xFC000000 - 0xFC0000FF Registers

APBUART0 0xFC001000 - 0xFC0010FF Registers

GRVERSION 0xFC080000 - 0xFC0800FF Registers

AHBSTAT 0xFC080200 - 0xFC0830FF Registers

GRGPIO 0xFC083000 - 0xFC0830FF Registers

AHBUART 0xFC086000 - 0xFC0860FF Registers

Debug Module 0xFE000000 - 0xFEFFFFFF Registers

L2CACHE IOAREA 0xFFF00000 - 0xFF3FFFFF Registers

AHB plug&play 0xFFFFF000 - 0xFFFFFFFF ROM area

NOEL-PF-EX-UM

Jul 2022, Version 2.0 8

Cobham Gaisler AB

Kungsgatan | SE-411 19 | Goteborg | Sweden

+46 31 7758650 | www.caes.com/gaisler

NOEL-PF-EX

3.4 IP core documentation

This user manual does not contain IP core documentation. Please refer to the GRLIB IP Core User’s

Manual [GRIP] available at http://gaisler.com/products/grlib/grip.pdf.

The GRMON debug monitor also provides information about the system-on-chip’s configuration via

the command info sys.

NOEL-PF-EX-UM

Jul 2022, Version 2.0 9

NOEL-PF-EX

Cobham Gaisler AB

Kungsgatan | SE-411 19 | Goteborg | Sweden

+46 31 7758650 | www.caes.com/gaisler

3.5 Signals

Please see the NOEL-PF-EX Quick Start Guide [QSG] for information on FPGA pinout.

3.6 Resource utilization

Resource utilization is described in the GRLIB area spreadsheet, available at:

https://www.gaisler.com/products/grlib/grlib_area.xls

NOEL-PF-EX-UM

Jul 2022, Version 2.0 10

NOEL-PF-EX

Cobham Gaisler AB

Kungsgatan | SE-411 19 | Goteborg | Sweden

+46 31 7758650 | www.caes.com/gaisler

4 Working with the board

4.1 Prerequisites

The following items are required to use NOEL-PF-EX designs:

• Workstation with Windows or Linux

• Microsemi MPF300-SPLASH-KIT

• NOEL-PF bitstream

• GRMON3 debug monitor

The two last items can be downloaded via http://gaisler.com/NOEL-PF.

Cobham Gaislers standard offer of toolchains can be used to build and run software on the NOEL-PF-

EX designs. Toolchains and run-time environments are available for download via http://gaisler.com.

4.2 Programming the FPGA device and connecting with GRMON3

Please see the NOEL-PF-EX Quick Start Guide [QSG] for information on FPGA programming and

using the SoC design.

4.3 Support

In case of technical issues please contact support@gaisler.com. The support line is normally available

only to companies and institutions with active support contracts. Limited support for the NOEL-PF-

EX example designs is provided. When contacting support please provide a clear description of which

design that is used and your affiliation.

Sales and licensing questions should be directed to sales@gaisler.com.

This manual suits for next models

1

Table of contents

Other CAES Computer Hardware manuals

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual