CMOSTEK CMT2281F2 User manual

AN200

Page 1/86

www.cmostek.com

Summary

CMT2281F2 is a low power, high performance OOK RF receiver chip.It covers a 300 MHz - 960MHz wireless

communication band with a RISC Flash type MCU embedded in it. It belongs to the CMOSTEK

NextGenRFTM series product.The product series include short range wireless communication chips, such as

transmitter, receiver, transceiver,SoC and so on.

The part numbers covered by this document are as shown below.

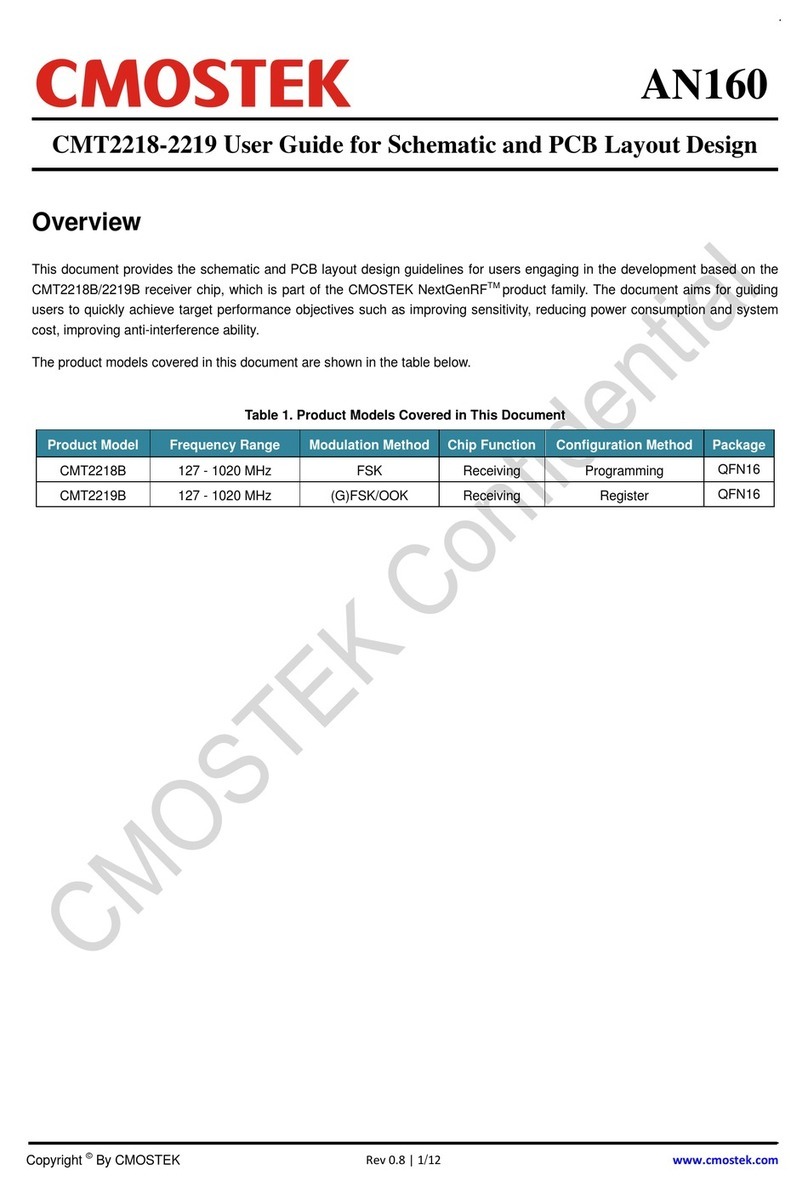

Table1. Part Numbers Covered by This Document

Part No.

Frequency

Modem

Sensitivity

Rx

Current

Configuration

Package

CMT22181F2

300 MHz -

960MHz

OOK

-109dBm

4.5mA

Embedded

MCU

SOP16

Note:The test conditions for sensitivity and Rx current are at 433.92MHz, 1kbps, 0.1% BER

AN200

CMT2281F2 User Guide

Copyright © By CMOSTEK

AN200

Page 2/86

www.cmostek.com

Table of Contents

1Chip Architecture Introduction............................................................................................................... 6

1.1 Overall Operation Principle......................................................................................................... 6

1.2IO Pin Description....................................................................................................................... 7

2RF Configuration and Control Mechanism............................................................................................ 9

2.1 Working Mode and Status........................................................................................................... 9

2.2 Simple Work Mode...................................................................................................................... 9

2.2.1 Power-Up Initialization......................................................................................................... 9

2.2.2Simple Mode Status Switching............................................................................................ 9

2.2.3 Auto Cycle Reset Function................................................................................................ 10

2.2.4 Low Power Processing.......................................................................................................11

2.3 Advanced Configuration Mode ..................................................................................................11

2.3.1 Work Status........................................................................................................................11

2.3.2 Initialization of configuration parameters and configuration process................................ 12

2.3.3 Control Register ................................................................................................................ 16

2.3.4 Detailed Description of the Operation Status.................................................................... 19

2.3.5 Soft Reset(Softrst)........................................................................................................ 20

2.3.6 Low Power Consumption Processing ............................................................................... 20

2.3.7 RF Control Interface Timing .............................................................................................. 22

2.3.8 OOK Demodulation and Clock Recovery.......................................................................... 22

2.3.9 RSSI Detection and Reading ............................................................................................ 23

2.3.10 Battery Voltage Detection.................................................................................................. 24

3Program Memory ................................................................................................................................... 25

4Special Function Register(SFR)........................................................................................................... 26

4.1 Address Mapping...................................................................................................................... 26

4.1.1 Bank0 SFR........................................................................................................................ 26

4.1.2 Bank1 SFR........................................................................................................................ 27

4.1.3 TMR0(Addr:0x01)......................................................................................................... 28

4.1.4 STATUS(Addr:0x03)..................................................................................................... 28

4.1.5 PORTA(Addr:0x05)....................................................................................................... 29

4.1.6 PORTC(Addr:0x07)...................................................................................................... 30

4.1.7 INTCON(Addr:0x0B)..................................................................................................... 30

4.1.8 PIR1(Addr:0x0C).......................................................................................................... 31

4.1.9 TMR2(Addr:0x11)......................................................................................................... 32

4.1.10 T2CON(Addr:0x12)....................................................................................................... 32

AN200

Page 3/86

www.cmostek.com

4.1.11 WDTCON(Addr:0x18).................................................................................................. 33

4.1.12 CMCON0(Addr:0x19)................................................................................................... 34

4.1.13 PR0(Addr:0x1A)........................................................................................................... 35

4.1.14 MSCKCON(Addr:0x1B)................................................................................................ 35

4.1.15 SOSCPR(Addr:0x1C/0x1D)......................................................................................... 36

4.1.16 OPTION(Addr:0x81)..................................................................................................... 36

4.1.17 TRISA(Addr:0x85)........................................................................................................ 37

4.1.18 TRISC(Addr:0x87)........................................................................................................ 39

4.1.19 PIE1(Addr:0x8C).......................................................................................................... 39

4.1.20 PCON(Addr:0x8E)........................................................................................................ 40

4.1.21 OSCCON(Addr:0x8F)................................................................................................... 40

4.1.22 PR2(Addr:0x92)............................................................................................................ 41

4.1.23 WPUA(Addr:0x95)........................................................................................................ 41

4.1.24 IOCA(Addr:0x96).......................................................................................................... 42

4.1.25 VRCON(Addr:0x99)...................................................................................................... 42

4.1.26 EEDAT(Addr:0x9A)....................................................................................................... 43

4.1.27 EEADR(Addr:0x9B)...................................................................................................... 43

4.1.28 EECON1(Addr:0x9C)................................................................................................... 43

4.1.29 EECON2(Addr:0x9D)................................................................................................... 44

4.1.30 Configuration Register UCFGx ......................................................................................... 44

4.1.31 PCL and PCLATH.............................................................................................................. 46

4.1.32 INDF and FSR Register .................................................................................................... 47

5MCU System Clock Source................................................................................................................... 48

5.1 Clock Source Mode................................................................................................................... 49

5.2 External Clock Mode................................................................................................................. 49

5.2.1 Oscillator Start-up Timer(OST)..................................................................................... 49

5.2.2 EC Mode ........................................................................................................................... 49

5.2.3 LP Mode and XT Mode ..................................................................................................... 49

5.3 Internal Clock Mode.................................................................................................................. 50

5.3.1 Clock Frequency Select(IRCF)Bit ................................................................................ 50

5.3.2 Clock Switching Timing of HFINTOSC and LFINTOSC.................................................... 50

5.4 Clock Switching......................................................................................................................... 51

5.4.1 System Clock Select Bit (SCS) ......................................................................................... 51

5.4.2 Oscillator Start-up Timeout Status(OSTS) Bit................................................................... 52

5.5 Two-Speed Clock Start-up Mode.............................................................................................. 52

5.5.1 Two-Speed Start-up Mode Configuration.......................................................................... 52

AN200

Page 4/86

www.cmostek.com

5.5.2 Two-Speed Start-up Sequence......................................................................................... 53

5.6 Fail-Safe Clock Monitor............................................................................................................. 53

5.6.1Fail-Safe Detection............................................................................................................ 54

5.6.2 Fail-Safe Operation........................................................................................................... 54

5.6.3 Fail-Safe Condition Being Cleared.................................................................................... 54

5.6.4 Reset or Wake-up from Sleep........................................................................................... 54

6Reset Timing........................................................................................................................................... 55

6.1 Power-on Reset (POR)............................................................................................................. 56

6.2 External Reset (MCLR)............................................................................................................. 56

6.3 Power-up Timer (PWRT)........................................................................................................... 56

6.4 Brown-out Reset (BOR(LVR)).............................................................................................. 57

6.5 Error Instruction Reset.............................................................................................................. 57

6.6 Timeout Action .......................................................................................................................... 57

7BOOT....................................................................................................................................................... 60

8Watchdog Timer..................................................................................................................................... 61

9Timer0 ..................................................................................................................................................... 62

9.1 Timer0 Introduction................................................................................................................... 62

9.2 Timer0 Timer Mode................................................................................................................... 62

9.3 Timer0 Counter Mode............................................................................................................... 63

9.3.1 Software Configuring Prescaler Circuit ............................................................................. 63

9.3.2 Timer0 Interrupt................................................................................................................. 64

9.3.3 Drive Timer0 with the External Clock ................................................................................ 64

10 Timer2 ..................................................................................................................................................... 65

11 Comparator............................................................................................................................................. 67

12 Data EEPROM......................................................................................................................................... 68

13 Clock Measurement............................................................................................................................... 69

14 Interrupt Mode........................................................................................................................................ 70

14.1 INT Interrupt.............................................................................................................................. 70

14.2 PORTA Level Change Interrupt ................................................................................................ 71

14.3 Interrupt Response ................................................................................................................... 71

14.4 Context Saving During Interrupts.............................................................................................. 72

15 MCU Sleep Mode.................................................................................................................................... 73

15.1 Wake-up Mode.......................................................................................................................... 73

15.2 Watchdog Wake-up................................................................................................................... 73

16 I/O Port .................................................................................................................................................... 74

16.1 PORTA Port and TRISA Register.............................................................................................. 74

AN200

Page 5/86

www.cmostek.com

16.2 Other Functions of the Port....................................................................................................... 74

16.2.1 Weak Pull-Up .................................................................................................................... 74

16.2.2 Interrupt-On-Change......................................................................................................... 74

16.3 Port Description ........................................................................................................................ 75

16.3.1 PORTA<2:0>..................................................................................................................... 75

16.3.2 PORTA3 ............................................................................................................................ 77

16.3.3 PORTA4 ............................................................................................................................ 78

16.3.4 PORTA5 ............................................................................................................................ 79

16.3.5 PORTA6 ............................................................................................................................ 80

16.3.6 PORTA7 ............................................................................................................................ 81

16.3.7 PORTC<7:0>..................................................................................................................... 82

17 Instruction Set List ................................................................................................................................ 83

18 Document Modification Record............................................................................................................ 85

19 Contact Information............................................................................................................................... 86

AN200

Page 6/86

www.cmostek.com

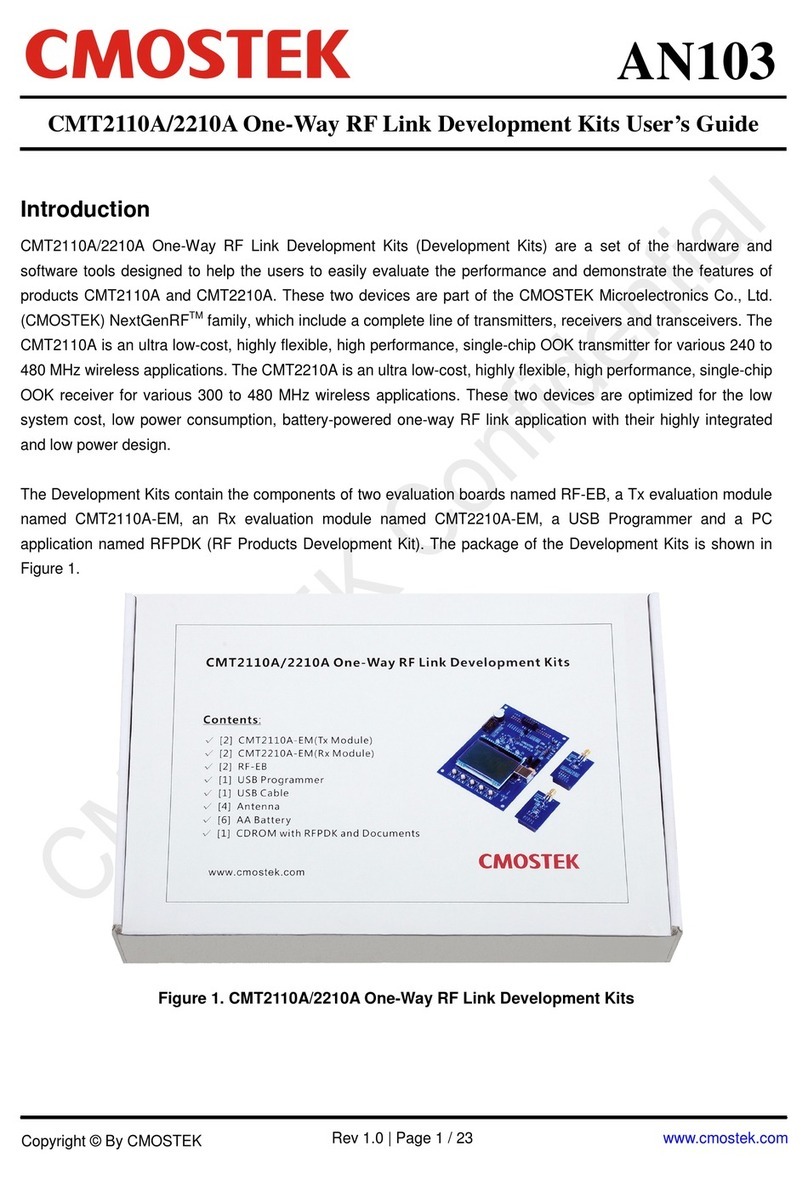

1 Chip Architecture Introduction

1.1 Overall Operation Principle

CMT2281F2 is a digital analog integrated receiver MCU. It uses the crystal oscillator to provide the reference

frequency and digital clock for PLL, and supports the OOK demodulation output from 1Kbps to 40Kbps, and

supports the Duty-Cycle mode based on MCU program control. It is suitable for all kinds of low power

consumption applications.

Digital

Demodulator

AFC LOOP

AGC LOOP

LNA

I LMT

Q LMT

RSSI ADC

SPI

EEPROM

D-DIV

LOOP

FILTER CP PFD

M-DIV

Radio

Controller

LDOs POR Band-

gap

LFOSC

26 Mhz

XO

VCO

SCL

CSB

VDDLGND

RFIN

XOSC AVDD

CPU

Program ROM

2K * 14Bit

Data EEPROM

256 * 8Bit

TMR/WDT

IO

CMP

RSTC/OST/

PWRT/BOOT CLKC

SFR

XTCK

EXTCK

IRCCK

SRAM

128 * 8Bit

CFG

DVDD

RFDATA PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7

DOUT

MUX

SDA

DOUT

3-SPI

PC[4:2] PC0

Figure 1-1. CMT2281F2 System Architecture

The chip uses LNA+MIXER+IFFILTER+LIMITTER+PLL low-IFarchitecture to achieve the Sub-GHz wireless

receive function. The analog circuit mixes the RF signal to IF and converts the signal from analog to digital

through the Limiter module, then outputs I/Q two single bit signals to the digital circuit for (G)FSK

demodulation. At the same time, SARADC will convert the real-time RSSI signal to 8-bit digital signal, and

send them to the digital part for OOK demodulation and other processing.The digital circuit is responsible for

mixing the intermediate frequency to zero frequency (Baseband) and performing a series of filtering and

decision processing, while AGC controlling the analog circuit dynamically, finally the 1-bit original signal is

demodulated. After demodulation, the signal will be output to RFDATAdirectly.

The voltage and current sources of each analog module in the chip need to be calibrated through the digital

part to work properly.The SPI communication port is used inside the chip, and the MCU controls the RF part

according to the SPI serial port timing.

AN200

Page 7/86

www.cmostek.com

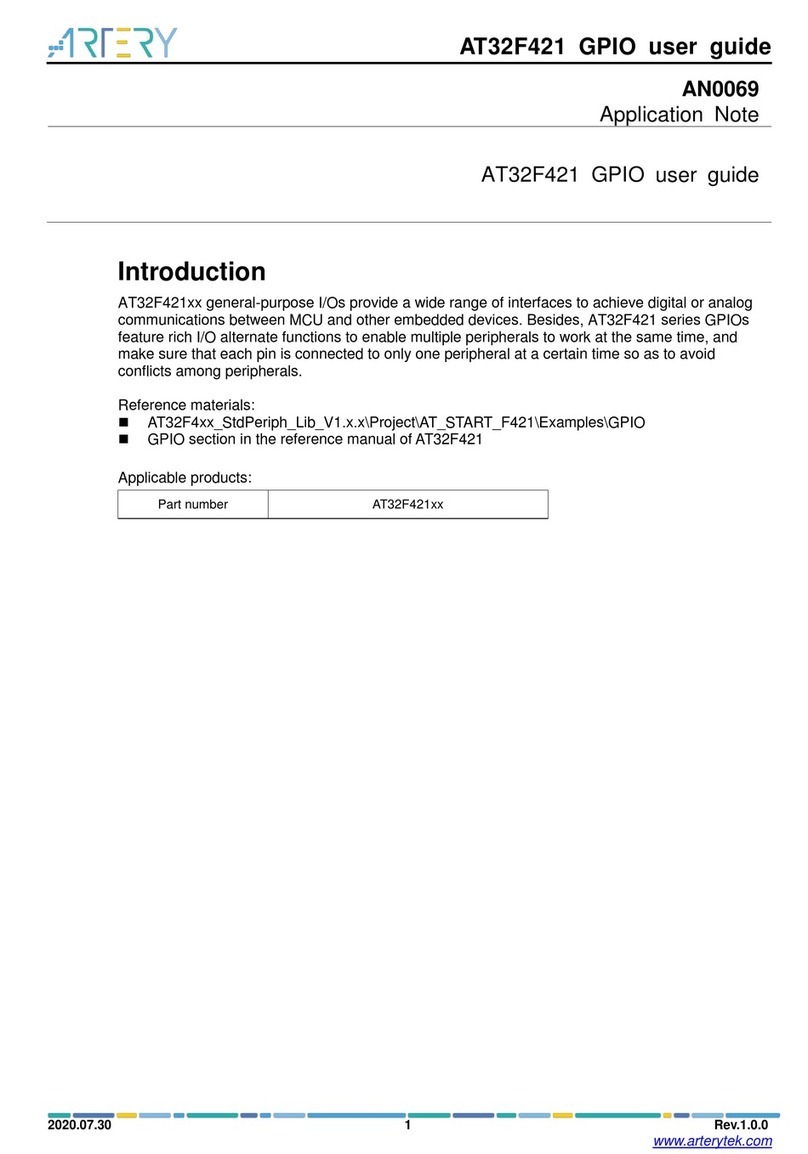

1.2 IO Pin Description

VDDL

RFIN

GND

AVDD/PC0

PA5/MCLRB

PA4

PA3

PA2/T0CKI/INT/C1OUT

XTAL

NC

PC4/SDIO/RFDATA

DVDD

PA6/OSC2/CLKO

PA7/OSC1/CLKI

PA1/C1IN-/ICSPDAT

PA0/C1IN+/ICSPCLK

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

Figure 1-2. CMT2281F2 Pin Top View

Table 1-1.CMT2281F2 SOP16 Pin Description

Pin No.

Name

Type

I/O

Function Description

1

VDDL

Digital

IO

Reference Voltage, needs to connect the external filter

capacitor.

2

RFIN

Digital

I

RF Signal Input, to the internal LNA

3

GND

Digital

--

Chip Power Ground

4

AVDD/PC0[1]

Analog

IO

AVDD

RF part pin, RF Power Positive Pole

PC0

General IO, connects to the RF part inside

the chip

5

PA5/MCLRB

Analog

I

PA5

Only acts as Input, supports IOC[2]

MCLRB

External Reset Input, be configured as

pull-up

6

PA4

Digital

IO

General IO, supports IOC, be configured as pull-up.

7

PA3

Digital

IO

General IO, supports IOC, be configured as pull-up.

8

PA2/T0CKI/INT/C1OUT

Digital

IO

PA2

General IO, supports IOC, be configured as

pull-up.

T0CKI

Timer0 Clock Input(Max=4MHz)

INT

External Interrupt Input

C1OUT

Comparator1 Output

9

PA0/C1IN+/ICSPCLK

Digital

IO

PA0

General IO, supports IOC, be configured as

pull-up.

C1IN+

Comparator Input+

ICSPCLK

Serial Port Clock signal in Debug/ Burning

mode

AN200

Page 8/86

www.cmostek.com

Pin No.

Name

Type

I/O

Function Description

10

PA1/C1IN-/ICSPDAT

Digital

IO

PA1

General IO, supports IOC, be configured as

pull-up.

C1IN-

Comparator Input-

ICSPDAT

Serial Port Data signal in Debug/ Burning

mode

11

PA7/OSC1/CLKI

Digital

IO

PA7

General IO, supports IOC, be configured as

pull-up.

OSC1

MCU Crystal pin

CLKI

External Clock Input pin

12

PA6/OSC2/CLKO

Digital

IO

PA6

General IO, supports IOC, be configured as

pull-up.

OSC2

MCU Crystal pin

CLKO

Test Clock Output

13

DVDD

Digital

I

Chip Power Positive pole

14

PC4/SDIO/RFDATA

Digital

IO

SDIO

3-wire SPI Serial Bus Data SDIO

RFDATA

Output the demodulated data stream in the

Rx status;

Output the low level in the Sleep status.

PC4

General IO, be connected to the RF part

inside the chip.

15

NC

--

--

Unconnected, suspended

16

XTAL

Analog

I

RF Crystal Oscillator Input

Internal

Pin

PC3/CSB[3]

Digital

IO

CSB

3-wire SPI Serial Bus Chip Selection bar

CSB, with the pull-up resistor inside the chip.

PC3

General IO, be connected to the RF part

inside the chip.

Internal

Pin

PC2/SCLK[3]

Digital

IO

SCLK

3-wire SPI Serial Bus Clock SCLK, with the

pull-down resistor inside the chip.

PC2

General IO, be connected to the RF part

inside the chip.

Note:

1. AVDD controls the power supply by PC0 inside the chip, and does not need to connect the pin to 5V.

If needing RF work, set the PC0 output to 1; if needing RF sleep, set the PC0 output to 0. For

different power supply range, it is recommended as follows:

For 2.0V~3.6V power supply application, PC0/AVDD can be reconnected to VDDL;

For 3.0V~5.0V power supply application, PC0/AVDD and VDDL are separately suspended, only

connect the filter capacitor with small capacity;

2. IOC is IO change wake-up, that is,port level edge jumping wake-up function;

3. PC3/CSB and PC2/SCLK are the internal control pins of the chip and have no the package terminals.

When CSB=1, PC4/SDIO/RFDATA is used for RFDATA.

When CSB=0, PC4/SDIO/RFDATA is used for SDIO.

AN200

Page 9/86

www.cmostek.com

2 RF Configuration and Control Mechanism

2.1 Working Mode and Status

There are two working modes for the OOK receiving function of CMT2281F2.

Simple Work mode: Default entry mode on power-up

Advanced Configuration mode: Configure the register and control the operation status through the

SPI Bus

2.2 Simple Work Mode

2.2.1 Power-Up Initialization

After power-up, MCU does not control any RF parts (for the SPI configuration operation). RF automatically

enters a Simple Work mode, which is a default mode. In this mode, only initializing the port of RF allows RF to

work. The steps are as follows:

1. PC3/CSB setting is output, which is high.

2. PC2/SCLK setting is output, which is low.

3. AVDD/PC0 setting is output, which is high (power supply for RF).

4. PC4/SDIO/RFDATAsetting is input (RFData begin to be sent to MCU)

In this mode, the multiply factor is fixed to 15.9875, so the target frequency and the crystal frequency are

calculated according to the following formula:

,300 MHz ≤FRF≤480 MHz

Among them, FXTAL is the crystal frequency,FRF is the target frequency, and the frequency range is from

300MHz to 480MHz.

For example:

Only matching the peripheral crystal of the 27.1412MHz can implement the OOK receiving and

demodulating at 433.92MHz.

If the OOK receiving and demodulating is implemented at 315MHz, the crystal frequency is:

315MHz÷15.9875=19.7029MHz.

2.2.2 Simple Mode Status Switching

The typical application scenario of this mode is that POR (Power On Reset) is released, then TUNE

(configurating the function, calibrating the frequency) is automatically carried out, and it enters the receiving,

and it performs the Auto Cycle Reset in the later operation process (the cycle time is 16.8 seconds [Note]).

AN200

Page 10/86

www.cmostek.com

POR

TUNE

RX

Auto Cycle

Reset

Figure 2-1. CMT2281F2 RF Part Default Mode Status Switching Diagram

2.2.3 Auto Cycle Reset Function

Auto Cycle Reset, as the name implies, periodically and automatically resets the CMT2281F2 RF part to the

POR status, and then re-TUNEs and enters the Rx status.Its role is to prevent the chip from abnormality in

various complex application environments due to unpredictable external factors, including configuration

anomalies, frequency locking anomalies, voltage anomalies, and so on.When an abnormal operation cycle

occurs, Auto Reset allows the chip to work again and restore normal.The timing of Auto CycleReset is shown

as follows:

…

POR Auto Rst Auto Rst Auto Rst Auto Rst

Rx Time 1st

4s

Rx Time 2nd

16.8 s

T Rx T T TRx Rx Rx T

Rx Time 3rd

16.8 s

Rx Time 4th

16.8 s

Table 2-2.CMT2281F2 RF Part Auto Cycle Reset Timing Diagram

After the first power on the chip, the RF internal POR is released; after a fixed 4 second, the RF part will be

automatically reset for the first time (MCU is independent and not involved). Subsequently, the RF part will

periodically reset according to 16.8 seconds operation time.After each reset, the chip will re-execute the

power-up process once, that is, execute the action of TUNE (abbreviated to T) and then enter the Rx.

Because the time of T is very short (relative to the 16.8 seconds operation cycle), it is less than 5ms.

Therefore, during the use of CMT2001, the intuitive feeling is that the chip has been in the Rx status, and the

process of automatic reset is transparent to users.

Note:

AN200

Page 11/86

www.cmostek.com

The 16.8 seconds of the operation cycle is generated by the RF part LFOSC as clock base, and it has the

+/-30% changes with the temperature of the operation environment. Therefore, it is calculated in 16.8

seconds, that is, the range is 11.76 seconds to 21.84 seconds.

2.2.4 Low Power Processing

In the Simple Work mode, the low power consumption for RF is very simple. It only needs to set PC0/AVDD to

0 as an output. But it is important to note that PC3/CSB and PC2/SCLK need to be set to high resistance input

because of internal Pull-up or Pull-down.

When restoring the work, first switch PC3/CSB to output, set it to 1; then switch PC2/SCLK to output, set it to

0, and finally set PC0/AVDD to 1as an output.

2.3 Advanced Configuration Mode

When users need to achieve more functions and higher performance, such as: the target operation frequency

is 868MHz, the target transmission rate need to be up to 20Kbps, and so on, they need to use the advanced

configuration mode. In this mode:

Select more frequency multiplication ratio coefficients to achieve the frequency range coverage of

300MHz ~ 960MHz.

Select the appropriate bandwidth to improve the reception effect.

Support more rate selection and support high rate communication applications.

2.3.1 Work Status

The advanced configuration mode can control the status switching of the RF part through the SPI, as shown

in the following figure:

AN200

Page 12/86

www.cmostek.com

INI

RX

STBY

go_stby go_rx

POR

Soft

Reset

IDLETUNE

Figure 2-3. CMT2281F2 RF Part Manual Work Mode Status Switching Diagram

2.3.2 Initialization of configuration parameters and configuration process

In the advanced configuration mode, the RF part needs the initial operation of the MCU by configuring the

registers through the SPI (INI in Figure 2-3), while the configuration parameters need to be exported for the

equivalent use by CMT2210LH on RFPDK.The specific way is: users fill the needed operation frequency and

the rate in the interface of RFDPK, click Export, the software will automatically convert the user needs into the

configuration register values (table), then configure these parameters to RF part through SPI. Users do not

need to understand the specific meanings of these parameters.

The configuration interface of RFPDK is as follows:

AN200

Page 13/86

www.cmostek.com

Figure 2-4. Configuration Interface of CMT2210LH RFPDK

The user clicks on Export, and RFPDK will export an”.exp”file, as shown below:

;-------------------------------------------------------------------------

; CMT2210LH Configuration File

; Generated by CMOSTEK RFPDK 1.46 Beta

; 2017.11.06 16:04

;-------------------------------------------------------------------------

; Mode = Advanced

; Part Number = CMT2210LH

; Frequency = 433.920 MHz

; Xtal Freq. = 27.1412 MHz

; Demodulation = OOK

; Data Rate = 2.4 kbps

; Tx Freq. Offset = 75 kHz

; RxXtalTol. = 20 ppm

; AGC = On

; Auto Reset Time = 16.8 Sec

; BW Options = Auto-Select

; Demod Method = Middle

; Long-Zero Number = 31

AN200

Page 14/86

www.cmostek.com

; Auto Squelch Enable = Off

; Auto Squelch Options = NA

; Auto Squelch TH = NA

; FILE CRC = 5618

;-------------------------------------------------------------------------

; The following are the EEPROM contents

;-------------------------------------------------------------------------

0x25EC

0x10D0

0x0100

0xA0DD

0x0BA1

0xE150

0x0000

0xDE10

0x54A5

0xA7C4

0x009C

0x0001

0x563E

0x0000

0x0000

0x0080

;-------------------------------------------------------------------------

; The following is the CRC result for

; the above EEPROM contents

;-------------------------------------------------------------------------

0x5618

;-------------------------------------------------------------------------

; The following are for CMOSTEK

; use, customers can ignore them

;-------------------------------------------------------------------------

0x0000

0x0010

In the files exported above, the displayed content that RF needs to be configured (the red font) can be

completed by writing the register.Therefore, the user needs to convert the 16-bit data format into the 8-bit

register content format.The method of conversion is that for each 16-bit Word, the upper 8-bit is an odd

number address, and the lower 8-bit is an even number address.The user only needs to convert the first 13

Words, and the register address range is 0x00 - 0x19, and the last 3 Words can be ignored.In this example,

the contents of the converted register are as follows:

AN200

Page 15/86

www.cmostek.com

Table 2-1. CMT2281F2 Parameter List

16-bitWord

Register

Address

8-bit Register

Content

0x2E5C

0x00

0x5C

0x01

0x2E

0x10D0

0x02

0xD0

0x03

0x10

0x0100

0x04

0x00

0x05

0x01

0xA0DD

0x06

0xDD

0x07

0xA0

0x0BA1

0x08

0xA1

0x09

0x0B

0xE150

0x0A

0x50

0x0B

0xE1

0x0000

0x0C

0x00

0x0D

0x00

0xDE10

0x0E

0x10

0x0F

0xDE

0x54A5

0x10

0xA5

0x11

0x54

0xA7C4

0x12

0xC4

0x13

0xA7

0x009C

0x14

0x9C

0x15

0x00

0x0001

0x16

0x01

0x17

0x00

0x563E

0x18

0x3E

0x19

0x56

The following is the INI (initialization) process:

1. After power on, the chip will automatically enter the RX, and the user can ignore it. Set

AUTO_RESET_DIS (0x21<6>) to 1, and turn off the automatic cycle reset.

2. Send the soft reset command, wait for 5ms, and confirm that the chip reenters the RX status.

3. Send the go_stby command to confirm that the chip enters the STBY status.

4. Convert the 16-bit Word content exported by RFPDK to 8-bit register content, and configure it to

address 0x00 - 0x19.

5. Set CONF_RETAIN (0x21<5>) to 1, turn off the EEPROM copy function, that is, keep the

configuration register to maintain the same function

6. Send the go_rx command and wait for 1ms to confirm that the chip is in the RX status.

7. Since then, the user can freely repeat the step3 and step4, switching between the STBY and the RX

AN200

Page 16/86

www.cmostek.com

status.

8. If the chip stays in the STBY status for a long time in the application process, when users need to

receive, it is suggested that users use soft reset to exit the STBY status and reenter the RX status

each time, so that the chip can be reprocessed a series of calibrations to maintain the best

performance.

9. If the chip is reset during the application process, it is necessary to redo from the step3 to step8 to

complete the chip configuration.

2.3.3 Control Register

The user needs to know and master the control register about the RF status. The following is the overview of

this part of the registers:

Table 2-2. RF Part Registers Overview Table inside CMT2281F2

Table 2-3. CUS_PWR_CTL Register Function Description

Register Name

Bits

R/W

Bit Name

Function Description

CUS_PWR_CTL

(0x20)

6

RW

PD_XO_DLDO_SEL

XO and DLDO manual control selection bit

0:Internal control (default)

1:Manual control

5

RW

PD_XO

XO manual switch:

0:Open (default)

1:Close

The bit takes effect only when

PD_XO_DLDO_SEL = 1

4

RW

PD_DLDO

DLDO manual switch:

0:Open (default)

1:Close

The bit takes effect only when

PD_XO_DLDO_SEL = 1

3

RW

PD_LFOSC_SEL

LFOSC manual control selection bit

0:Internal control (default)

1:Manual control

2

RW

PD_LFOSC

LFOSC manual switch:

0:Open (default)

1:Close

The bit takes effect only when PD_LFOSC_SEL

= 1

Address R/W Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bank

0x20 RW CUS_PWR_CTL RESV PD_XO_DLDO_SEL PD_XO PD_DLDO PD_LFOSC_SEL PD_LFOSC LV_RSTN_SEL LV_RSTN

0x21 RW CUS_FUNC_EN HIGH_SPEED_SPI_EN AUTO_RESET_DIS CONF_RETAIN RESV RESV RESV RESV RESV

0x22 RW CUS_MODE_CTL RESV

0x23 R CUS_RSSI_READ

0x24 R CUS_LBD_RESULT

0x3F W CUS_SOFTRST

软复位

注意:请不要改动RESV位的值,维持默认值即可

HV控制区

(0x20 - 0x24)

SOFTRST

CHIP_MODE_STA <2:0>

CHIP_MODE_SWT <3:0>

RSSI_DBM <7:0>

LBD_RESULT <7:0>

AN200

Page 17/86

www.cmostek.com

Register Name

Bits

R/W

Bit Name

Function Description

1

RW

LV_RSTN_SEL

LV reset manual control selection bit

0:Internal control (default)

1:Manual control

0

RW

LV_RSTN

LV reset manual switch:

0:Open (default)

1:Close

The bit takes effect only when LV_RSTN_SEL =

1

Table 2-4. CUS_FUNC_EN Register Function Description

Register Name

Bits

R/W

Bit Name

Function Description

CUS_FUNC_EN

(0x21)

7

RW

HIGH_SPEED_SPI_EN

SPI bus rate upper limit selection:

0:Upper limit is 500KHz

1:Upper limit is 2MHz

6

RW

AUTO_RESET_DIS

Automatic periodic reset enabled bit:

0:Enable (default)

1:Disable

5

RW

CONF_RETAIN

Disable the copy EEPROM function, that is,

retain the function of the configuration

register unchanged. (Effective for soft reset,

except power on).

0:Disable(default)

1:Enable

Table 2-5. CUS_MODE_CTL Register Function Description

Register Name

Bits

R/W

Bit Name

Function Description

CUS_MODE_CTL

(0x22)

7:5

R

CHIP_MODE_STA<3:0>

Chip status:

000:IDLE, the transient status of power-up,

please ignore it.

010:STBY, standby status

100:RX, receiving status

Others: Transition status or invalid status,

please ignore it.

3:0

RW

CHIP_MODE_SWT<3:0>

Status switching commands:

0010:go_stby

1000:go_rx

Others: not allowed to send.

AN200

Page 18/86

www.cmostek.com

Table 2-6. CUS_RSSI_READ Register Function Description

Register Name

Bits

R/W

Bit Name

Function Description

CUS_RSSI_READ

(0x23)

7:0

R

RSSI_DBM

The current signal intensity value, the range

is 0~255, the higher the value, the stronger

the signal, please see this chapter 2.3.9 in

detail.

Table 2-7. CUS_LBD_RESULT Register Function Description

Register Name

Bits

R/W

Bit Name

Function Description

CUS_LBD_RESULT

(0x24)

7:0

R

LBD_RESULT

The power supply voltage measurement

value, please see the chapter 2.3.10 in

detail.

Table 2-8. CUS_SOFTRST Register Function Description

Register Name

Bit

R/W

Bit Name

Function Description

CUS_SOFTRST

(0x3F)

7:0

W

SOFTRST

The soft reset command of RF part, send

0xFF, and please see the chapter 2.3.5 in

detail.

AN200

Page 19/86

www.cmostek.com

2.3.4 Detailed Description of the Operation Status

POR Status and Power-up Flow

After AVDD/PC0 is set to 1 and powered up, the RF part usually needs to wait for about 1ms, then POR will

release.After the release of the POR, the crystal will start, the start time default is N ms, according to the

characteristics of the crystal itself. After starting, the chip needs to wait for the crystal settled, then the system

start working. The default setting is 2.48ms*(1 +/- 30%).The error is because the chip is counted by LFOSC.

The chip remains in the IDLE status until the crystal is settled.After the settled crystal, the chip will leave the

IDLE status and begin to do the calibration of each module.After the calibration is completed, the chip will

automatically enter the RX status.At any time, as long as the soft reset or the automatic cycle reset, the chip

will go back to the IDLE and re-execute the power-up process once.

POR

VDD

POR Release

<= 1 ms XTAL Stablize

<= about 2.5 ms

EEPROM Copy,

Block Calibrations

<= 1 ms Enters RX state

XTAL Start up

<= N ms

Figure 2-5. CMT2281F2 RF Part Power-up Flow Chart

INI Process

INI is not a status, but it refers to the initialization process mentioned in the previous article, which is switched

from the power-up default work mode to the manual work mode.This process only needs to be done once on

the first power-up of the chip.

TUNE Status

This status is not visible to the user.It is completed automatically by the chip, which includes the work of

EEPROM parameter copy and frequency correction. The EEPROM copy will make all the configuration

parameters effective.

STBYStatus

At STBY, the crystal is opened, and the LDO of the digital circuit will be opened, but the demodulation circuit is

closed, and the STBY stauts current is much less than the Rx status.

RX Status

All modules on the receiver in RX status will be opened. Switching from STBY to RX needs to add the PLL

calibration and settled time of the 250us.

AN200

Page 20/86

www.cmostek.com

2.3.5 Soft Reset(Softrst)

RF part soft reset is achieved by writing 0xFF to the address 0x7F through the SPI. After receiving this

command, the chip will immediately reset and return to the IDLE status, and immediately re-execute the

power-up process. So after the user sends the soft reset command, he could not query the IDLE status

because the status flashes across.Usually, soft reset is more suitable for operation in advanced configuration

mode, because in simple work mode, there will be automatic cycle reset function (see the chapter 2.2.3

automatic cycle reset function).

In the case of advanced configuration mode, the automatic cycle reset function is disabled according to the

initialization process (INI, see the chapter 2.3.2), so the RF is completely controlled by the MCU.In order to

better deal with the complicated operation environment, users need to consider in the design of software

through periodic soft reset (soft_reset) command to RF, so that RF can better adapt to the complex operation

environment. After the soft_reset, the chip will still maintain the configuration as before (because

CONF_RETAIN is enabled),unless the chip powersoff and powers on again (such as setting the PC0/AVDD to

0 as an output, cutting the RF power, and then restoring the PC0/AVDD to 1 as an output). After restoring the

default simple work mode, the automatic cycle reset function can be enabled.

2.3.6 Low Power Consumption Processing

In the advanced configuration mode, there are two ways of RF low power processing.

1. Using PC0/AVDD to control the power of the RF part directly, this way can completely cut the RF power,

and also completely enter the lowest power consumption status.However, it is necessary to pay attention

that it is the process of re power on reset (POR) when power supply is supplied to the RF part again.So if

the user is in the manual mode, it will need another initialization process after power supply (see the

section 2.3.5 in this chapter). In addition, the way of setting up the SPI port is the same as the low power

processing in the simple work mode. See the section 2.2.4 in this chapter.

2. Keep the continuous power supply of the PC0/AVDD and send the go_stby command through the SPI to

enter the low power status.The advantage is that RF does not need to power off or need to do the

initialization process of the power on reset (POR) frequently. But the disadvantage is also obvious,it can

not completely achieve zero power consumption.Because in the STBYstatus, there are several parts of

the circuit in power consumption, such as crystal, LDO of digital circuit (see the Table 2-9 and the Table

2-10), but users can manually turn off part of the circuit in the STBY status to make it enter the

corresponding low power status.The details can be combined with Table 2-9 and Table 2-10, and are

handled according to the "Closing process" and "Opening process" below.

Table 2-9. CMT2281F2RF Status and Module Opening Table

Status

Binary code

Switching

command

Opening module

IDLE

000

soft_rst

5V-PAD, POR

STBY

010

go_stby

5V-PAD, POR, XTAL, DLDO, LFOSC

Table of contents

Other CMOSTEK Microcontroller manuals

Popular Microcontroller manuals by other brands

PIKODER

PIKODER USB2PPM user manual

Silicon Laboratories

Silicon Laboratories C8051F12 Series manual

Bosch

Bosch XDK 110 Getting started

Silicon Laboratories

Silicon Laboratories EFM32 quick start guide

Equinox Systems

Equinox Systems Flash 8051 Getting started

Texas Instruments

Texas Instruments MSP432 user guide