CMOSTEK CMT2380F32 User manual

CMT2380F32

Rev0.9 | 1/65

www.cmostek.com

MCU Features

32 MHz Cortex-M0+ 32-bit CPU platform

32 kB Flash with erasing protection

4 kB RAM with parity to enhance system stability

16 general purpose I/O interfaces available

Flexible power management system

-0.5 uA @ 3 V(deep sleep mode): the power

consumption when all clocks are off, power-on

reset is active, I/O state is maintained, I/O

interrupt is active and all registers, RAM, and

CPU stay in data storage status

-0.8 uA@ 3 V (deep sleep mode): the power

consumption when RTCs work

-150 uA/MHz @3 V @16 MHz: the power

consumption when CPU and peripheral modules

run with program Flash operating internally

-2 us: the chip's wakeup time from ultra-low power

mode, the fast response enables mode switching

more flexible and efficient

RTC and crystal

-External high speed crystal: 4 –32 MHz

-External low speed crystal: 32.768 kHz

-Internal high speed clock: 4/8/16/22 and 24 MHz

-Internal low speed clock: 32.8/38.4 kHz

Timer and counter

-3 general purpose 16-bit timers/counters

-A 16-bit timer/counter available in low power

mode

-3 high performance 16-bit timers/counters

capable for capture/compare and PWM output

-One 20-bit programmable counter/watchdog

circuit with built-in dedicated ultra-low power

RC-OSC to perform WDT counting

Communication interface

-UART 0 and UART 1 standard communication

interface

-One ultra-low power UART(LPUART) supporting

for low speed clock

-Standard I2C and SPI communication interface

One 12-bit 1 Msps SAR ADC

2 voltage comparators

Low voltage detector (LVD), configurable 16-level

comparison level, support for port voltage and supply

voltage monitoring

RF Features

Frequency range: 127 –1020 MHz

Modem: FSK, GFSK, MSK, GMSK and OOK

Data rate:0.5 –300 kbps

Sensitivity: -121 dBm @ 434 MHz, FSK

Receiving current: 8.5 mA @ 434 MHz, FSK

Transmitting current: 72 mA @ 20 dBm, 434 MHz

Configurable up to 64-byte FIFO

System Features

Supply voltage:1.8 –3.6 V

Operating temperature: -40 –85 ℃

QFN40 5x5 packaging

Application

Smart grid and automatic meter reading

Home security and building automation

Wireless sensor networks and industrial monitoring

ISM band data communication

Description

Employed a 32-bit Cortex-M0+ CPU core and an ultra-low

power RF transceiver, the CMT2380F32 is a FSK, GFSK,

MSK, GMSK and OOK wireless MCU with high performance

and ultra-low power applying to 127 to 1020 MHz band

wireless applications. Operating with 1.8 to 3.6 V supply

voltage, the CMT2380F32 consumes only 72 mA current

while delivering up to 20 dBm power. As for the receiver, the

CMT2380F32

Ultra Low Power Sub-1GHz Wireless MCU

SoC

CMT2380F32

Rev0.9 | 2/65

www.cmostek.com

device consumes an ultra-low current of 8.5 mA with the

sensitivity reaching -121 dBm.

The device employs a wide range of peripherals like support

of standard UART, I2C and SPI interfaces, up to 16

general-purpose I/Os, support of internal high-speed,

low-speed, low-power RC oscillators and 32.768 kHz

external crystal oscillators, flexible data handling and packet

handler, up to 64-byte Tx/Rx FIFO, feature-enriched RF

GPIO, multiple low-power modes and fast-start mechanisms,

high-precision RSSI, manual fast frequency hopping,

multi-channel input 12-bit high-speed ADC, etc. Leading the

industry in the aspect of the smallest package size, the

CMT2380F32 is ideal for size constraints due to a small

form-factor, power-efficient IoT applications.

CMT2380F32

Rev0.9 | 3/65

www.cmostek.com

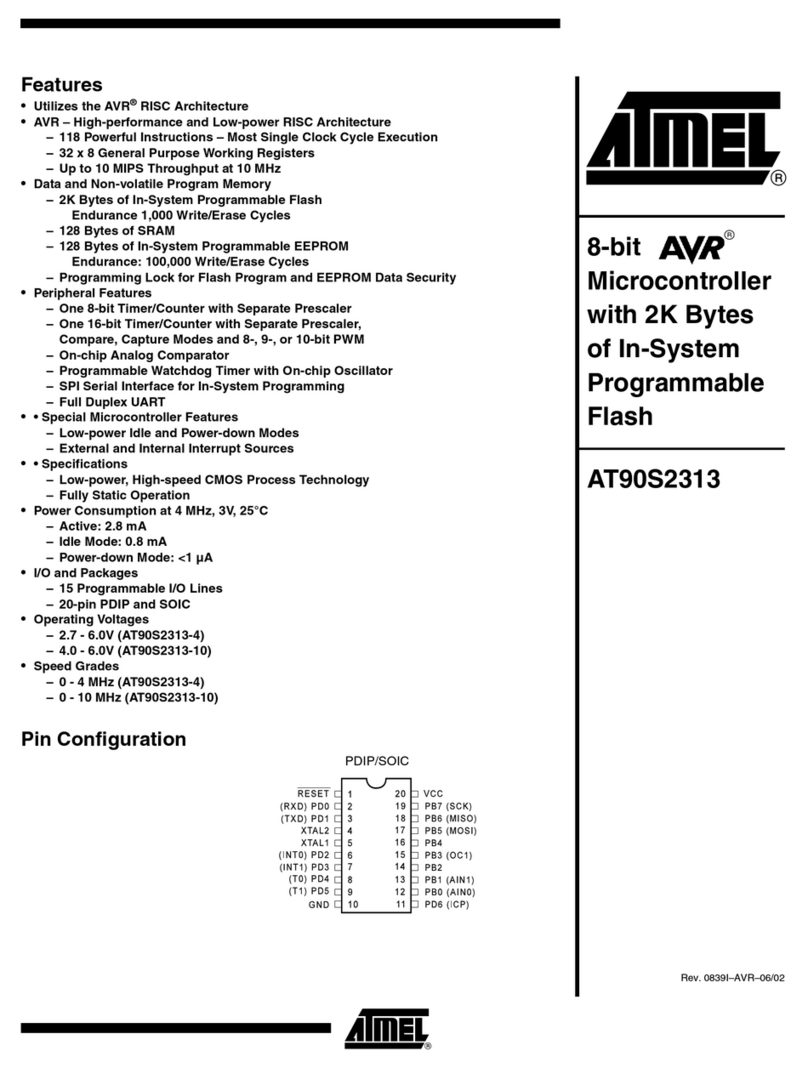

Table 1. The CMT2380F32 Resource List

Figure 1. Typical Application Schematic for the CMT2380F32

(20dBm Output Power with Antenna Switch)

Table 2. Typical Application BOM (20 dBm Output Power with Antenna Switch)

Label

Description

Component Value

Unit

Supplier

434 MHz

868/915 MHz

C1

± 5%, 0402 NP0, 50 V

15

15

pF

-

C2

± 5%, 0402 NP0, 50 V

10

3.9

pF

-

C3

± 5%, 0402 NP0, 50 V

8.2

2.7

pF

-

C4

± 5%, 0402 NP0, 50 V

8.2

2.7

pF

-

C5

± 5%, 0402 NP0, 50 V

220

220

pF

-

C6

± 5%, 0402 NP0, 50 V

4.7

2

pF

-

C7

± 5%, 0402 NP0, 50 V

4.7

2

pF

-

C8

± 5%, 0402 NP0, 50 V

220

220

pF

-

C9

± 5%, 0402 NP0, 50 V

220

220

pF

-

C12

± 5%, 0402 NP0, 50 V

470

pF

-

C13

± 20%, 0402 X7R, 25 V

2.2

nF

-

Memory

Analog Peripherals

Digital Peripherals

Others

ROM

RAM

ADC

VCMP

LVD

RTC

WDT

Timer

CCP

PWM

UART

LPUART

SPI

I2C

PCA

CRC

GPIO

32 k

4 k

12-bit

x9-ch

2

√

√

√

16-bit

x6

16-bit

x6-ch

2

1

1

1

√

√

16+1

CMT2380F32

Rev0.9 | 4/65

www.cmostek.com

Label

Description

Component Value

Unit

Supplier

434 MHz

868/915 MHz

C14

± 20%, 0603 X7R, 25 V

4.7

uF

-

C15

± 5%, 0402 NP0, 50 V

27

pF

-

C16

± 5%, 0402 NP0, 50 V

27

pF

-

C17

± 5%, 0402 NP0, 50 V

10

pF

-

C18

± 5%, 0402 NP0, 50 V

10

pF

-

C19

± 20%, 0402 X7R, 25 V

100

nF

-

C20

± 20%, 0603 X7R, 25 V

4.7

uF

-

C21

± 20%, 0402 X7R, 25 V

100

nF

-

C22

± 5%, 0402 NP0, 50 V

470

pF

-

L1

± 10%, 0603multilayer chip inductor

180

100

nH

Sunlord SDCL

L2

± 10%, 0603 multilayer chip inductor

27

6.8

nH

Sunlord SDCL

L3

± 10%, 0603 multilayer chip inductor

18

12

nH

Sunlord SDCL

L4

± 10%, 0603 multilayer chip inductor

33

22

nH

Sunlord SDCL

L5

± 10%, 0603 multilayer chip inductor

15

10

nH

Sunlord SDCL

L6

± 10%, 0603 multilayer chip inductor

27

12

nH

Sunlord SDCL

L7

± 10%, 0603 multilayer chip inductor

27

12

nH

Sunlord SDCL

L8

± 10%, 0603 multilayer chip inductor

68

18

nH

Sunlord SDCL

Y1

± 10 ppm, SMD32*25 mm

26

MHz

EPSON

U1

CMT2380F32, ultra-low power sub-1GHz

wireless MCU

-

-

CMOSTEK

U2

AS179, PHEMT GaAs IC SPDT Switch

-

-

SKYWORKS

R1

± 5%, 0402

2.2

kΩ

-

R2

± 5%, 0402

2.2

kΩ

-

CMT2380F32

Rev0.9 | 5/65

www.cmostek.com

Table of Contents

1Electrical Specifications..................................................................................................................... 7

1.1 Recommended Operating Conditions ................................................................................................................7

1.2 Absolute Maximum Ratings................................................................................................................................ 7

1.3 RF Power Consumption.....................................................................................................................................8

1.4 Receiver.............................................................................................................................................................9

1.5 Transmitter....................................................................................................................................................... 11

1.6 RF Operating Mode Switching Time................................................................................................................. 12

1.7 RF Frequency Synthesizer............................................................................................................................... 12

1.8 Requirement on Crystals for RF Section.......................................................................................................... 13

1.9 Controller Output Features............................................................................................................................... 13

1.10 Controller Input Features(P0, P1, P2 and P3 Reset)..................................................................................... 14

1.11 Port External Input Sampling Requirements (Timer Gate/Timer Clock)........................................................... 14

1.12 Port Leakage Features (P0, P1, P2 and P3).................................................................................................... 15

1.13 Controller Power Consumption Features ......................................................................................................... 15

1.14 POR/BOR Features.......................................................................................................................................... 18

1.15 Controller External XTH Oscillator.................................................................................................................... 18

1.16 Controller External 32.768 kHz Oscillator......................................................................................................... 19

1.17 Controller Internal RCH Oscillator.................................................................................................................... 19

1.18 Controller Internal RCL Oscillator..................................................................................................................... 20

1.19 Controller Flash Features................................................................................................................................. 20

1.20 Controller Low Power Mode Recover Time...................................................................................................... 20

1.21 Controller ADC Features.................................................................................................................................. 21

1.22 Analog Voltage Comparator............................................................................................................................. 23

1.23 Low Battery Detection Features....................................................................................................................... 25

1.24 Receive Current and Supply Voltage Correlation............................................................................................. 27

1.25 Correlation Among Receive Current, Supply Voltage and Temperature.......................................................... 27

1.26 Receive Sensitivity and Supply Voltage Correlation......................................................................................... 28

1.27 Receive Sensitivity and Temperature Correlation ............................................................................................ 29

1.28 Transmit Power and Supply Voltage Correlation.............................................................................................. 29

1.29 Phase Noise..................................................................................................................................................... 30

2Pin Description.................................................................................................................................. 31

3Chip Structure.................................................................................................................................... 37

4Sub-GHz Transceiver........................................................................................................................ 39

4.1 Transmitter....................................................................................................................................................... 39

4.2 Receiver........................................................................................................................................................... 39

4.3 Transceiver Power-on Reset (POR)................................................................................................................. 39

4.4 Transceiver Crystal Oscillator........................................................................................................................... 40

4.5 Transceiver Built-in Low Frequency Oscillator (LPOSC).................................................................................. 41

4.6 Transceiver Built-in Low Battery Detection....................................................................................................... 41

4.7 Receiver Signal Strength Indication (RSSI)...................................................................................................... 41

4.8 Phase Jump Detector (PJD)............................................................................................................................. 42

4.9 Receiver Clock Data Recovery (CDR) ............................................................................................................. 42

CMT2380F32

Rev0.9 | 6/65

www.cmostek.com

4.10 Fast Manual Frequency Hopping ..................................................................................................................... 43

4.11 Transceiver Control Interface and Operating Mode.......................................................................................... 43

4.11.1 Transceiver SPI Interface Timing.............................................................................................................43

4.11.2 Transceiver FIFO Interface Timing...........................................................................................................44

4.11.3 Transceiver Operating Status, Timing, and Power Consumption.............................................................45

4.11.4 Transceiver GPIO Function and Interrupt Mapping..................................................................................48

5Controller function Introduction...................................................................................................... 50

5.1 Cortex M0+ Core Function Description ............................................................................................................ 50

5.2 Memory............................................................................................................................................................ 53

5.2.1 On-chip Program Memory Flash..............................................................................................................53

5.2.2 On-chip Data Memory Flash....................................................................................................................53

5.3 System Clock ................................................................................................................................................... 55

5.4 Operating Mode................................................................................................................................................ 55

5.5 RTC Hardware Real Time Clock RTC.............................................................................................................. 55

5.6 General Purpose IO Port.................................................................................................................................. 55

5.7 Interrupt Controller ........................................................................................................................................... 55

5.8 Reset Controller ............................................................................................................................................... 57

5.9 Timer/Counter .................................................................................................................................................. 57

5.10 Watchdog WDT................................................................................................................................................ 58

5.11 Universal Purpose Asynchronous Receiver UART0, UART1 and LPUART..................................................... 58

5.12 Synchronous Serial Interface SPI..................................................................................................................... 59

5.13 I2C Bus ............................................................................................................................................................ 59

5.14 Buzzer.............................................................................................................................................................. 59

5.15 Clock Calibration Circuit................................................................................................................................... 59

5.16 Unique ID number............................................................................................................................................ 59

5.17 CRC16 Hardware Cyclic Redundancy Check Code......................................................................................... 59

5.18 12-bit SARADC ................................................................................................................................................ 59

5.19 Voltage Comparator (VC)................................................................................................................................. 59

5.20 LVD Low Voltage Detector (LVD)..................................................................................................................... 59

5.21 Embedded Debug System ............................................................................................................................... 60

5.22 High Security.................................................................................................................................................... 60

6Order Information.............................................................................................................................. 61

7Packaging Information...................................................................................................................... 62

8Top Marking........................................................................................................................................ 63

9Reference Documents ...................................................................................................................... 64

10 Revise History.................................................................................................................................... 64

11 Contacts ............................................................................................................................................. 65

CMT2380F32

Rev0.9 | 7/65

www.cmostek.com

1 Electrical Specifications

VDD= 3.3 V,TOP= 25 °C ,FRF = 433.92 MHz, sensitivity is measured by receiving a PN9 sequence and matching to 50 Ω

impedance, 0.1% BER if nothing else stated. All measurement results are obtained using the evaluation board CMT2380F32-EM

if nothing else stated.

1.1 Recommended Operating Conditions

Table 3. Recommended Operating Conditions

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Operating supply voltage

VDD

1.8

3.6

V

Operating temperature

TOP

-40

85

℃

Operating speed

CPU frequency range

256k

4M

32 M

Hz

RF supply voltage slope

VRF-PSR

1

mV/us

Controller supply voltage

Slope

VMCU-PSR

50

mV/us

Controller power-on reset

effective voltage

VMCU-POR

0.1

V

1.2 Absolute Maximum Ratings

Table 4. Absolute Maximum Ratings[1]

Parameter

Symbol

Condition

Min.

Typ.

Max.

Supply voltage

VDD

-0.3

3.6

V

Interface voltage

VIN

-0.3

3.6

V

Junction temperature

TJ

-40

125

℃

Storage temperature

TSTG

-50

150

℃

Soldering temperature

TSDR

Lasts for at least 30 seconds

Human body model (HBM)

255

℃

ESD rating[2]

Human body model (HBM)

-2

2

kV

Latch-up current

@ 85 ℃

-100

100

mA

Notes:

[1]. Exceeding the Absolute Maximum Ratings may cause permanent damage to the equipment. This value is a pressure

rating and does not imply that the function of the equipment is affected under this pressure condition, but if it is exposed

to absolute maximum ratings for extended periods of time, it may affect equipment reliability.

[2]. The CMT2380F32 is a high performance RF integrated circuit. The operation and assembly of this chip should only be

performed on a workbench with good ESD protection.

Caution! ESD sensitive device. Precaution should be used when handling the device in order to

prevent performance degradation or loss of functionality.

CMT2380F32

Rev0.9 | 8/65

www.cmostek.com

1.3 RF Power Consumption

Table 5. RF Power Consumption

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Sleep current

ISLEEP

Sleep mode, sleep counter off

300

nA

Sleep mode ,sleep counter on

800

nA

Standby current

IStandby

Crystal oscillator on

1.45

mA

RFS current

IRFS

433 MHz

5.7

mA

868 MHz

5.8

mA

915 MHz

5.8

mA

TFS current

ITFS

433 MHz

5.6

mA

868 MHz

5.9

mA

915 MHz

5.9

mA

FSK, RX current

(high performance)

IRx-HP

433 MHz, 10 kbps,10 kHz FDEV

8.5

mA

868 MHz, 10 kbps, 10 kHz FDEV

8.6

mA

915 MHz, 10 kbps,10 kHz FDEV

8.9

mA

FSK, RX current

(low power mode)

IRx-LP

433 MHz, 10 kbps, 10 kHz FDEV

7.2

mA

868 MHz, 10 kbps, 10 kHz FDEV

7.3

mA

915 MHz, 10 kbps, 10 kHz FDEV

7.6

mA

FSK, TX current

ITx

433 MHz, +20 dBm (Direct-tie)

72

mA

433 MHz, +20 dBm (With RF switch)

77

mA

433 MHz, +13 dBm (Direct-tie)

23

mA

433 MHz, +10 dBm (Direct-tie)

18

mA

433 MHz, -10 dBm (Direct-tie)

8

mA

868 MHz, +20dBm (Direct-tie)

87

mA

868 MHz, +20dBm (With RF switch)

80

mA

868 MHz, +13 dBm (Direct-tie)

27

mA

868 MHz, +10 dBm (Direct-tie)

19

mA

868 MHz, -10 dBm (Direct-tie)

8

mA

915 MHz, +20 dBm (Direct-tie)

70

mA

915 MHz, +20 dBm (Direct-tie)

75

mA

915 MHz, +13 dBm (Direct-tie)

28

mA

915 MHz, +10 dBm (Direct-tie)

19

mA

915 MHz, +10 dBm (Direct-tie)

8

mA

CMT2380F32

Rev0.9 | 9/65

www.cmostek.com

1.4 Receiver

Table 6. Receiver Specifications

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Data Rate

DR

OOK

0.5

40

kbps

FSK and GFSK

0.5

300

kbps

Error

FDEV

FSK and GFSK

2

200

kHz

Sensitivity

@ 433 MHz

S433-HP

DR = 2.0 kbps, FDEV = 10 kHz

-121

dBm

DR = 10 kbps, FDEV = 10 kHz

-116

dBm

DR = 10 kbps, FDEV= 10 kHz (low power

mode)

-115

dBm

DR = 20 kbps, FDEV = 20 kHz

-113

dBm

DR = 20 kbps, FDEV = 20 kHz (low power

mode)

-112

dBm

DR = 50 kbps, FDEV = 25 kHz

-111

dBm

DR =100 kbps, FDEV = 50 kHz

-108

dBm

DR =200 kbps, FDEV = 100 kHz

-105

dBm

DR =300 kbps, FDEV = 100 kHz

-103

dBm

Sensitivity

@ 868 MHz

S868-HP

DR = 2 kbps, FDEV = 10 kHz

-119

dBm

DR = 10 kbps, FDEV = 10 kHz

-113

dBm

DR = 10 kbps, FDEV = 10 kHz (low power

mode)

-111

dBm

DR = 20 kbps, FDEV = 20 kHz

-111

dBm

DR = 20 kbps, FDEV = 20 kHz (low power

mode)

-109

dBm

DR = 50 kbps, FDEV = 25 kHz

-108

dBm

DR =100 kbps, FDEV = 50 kHz

-105

dBm

DR =200 kbps, FDEV = 100 kHz

-102

dBm

DR =300 kbps, FDEV = 100 kHz

-99

dBm

Sensitivity

@ 915 MHz

S915-HP

DR = 2 kbps, FDEV = 10 kHz

-117

dBm

DR = 10 kbps, FDEV = 10 kHz

-113

dBm

DR = 10 kbps, FDEV = 10 kHz(low power

mode)

-111

dBm

DR = 20 kbps, FDEV = 20 kHz

-111

dBm

DR = 20 kbps, FDEV = 20 kHz (low power

mode)

-109

dBm

DR = 50 kbps, FDEV = 25 kHz

-109

dBm

DR =100 kbps, FDEV = 50 kHz

-105

dBm

DR =200 kbps, FDEV = 100 kHz

-102

dBm

DR =300 kbps, FDEV = 100 kHz

-99

dBm

Saturation

PLVL

20

dBm

Image rejection ratio

IMR

FRF = 433 MHz

35

dBc

FRF = 868 MHz

33

dBc

FRF = 915 MHz

33

dBc

Receive channel

bandwidth

BW

Receive channel bandwidth

50

500

kHz

Co-channel rejection

CCR

DR = 10 kbps, FDEV = 10 kHz

Interference with the same modulation

-7

dBc

CMT2380F32

Rev0.9 | 10/65

www.cmostek.com

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Adjacent channel

rejection

ACR-I

DR = 10 kbps, FDEV = 10 kHz, BW = 100

kHz, 200 kHz channel spacing,

interference with the same modulation

30

dBc

Alternate channel

rejection

ACR-II

DR = 10 kbps, FDEV = 10 kHz,

BW=100kHz, 400 kHz channel spacing,

interference with the same modulation

45

dBc

Blocking

BI

DR = 10 kbps, FDEV = 10 kHz, ±1 MHz

offset, continuous wave interference

70

dBc

DR = 10 kbps, FDEV = 10 kHz, ±2 MHz

offset, continuous wave interference

72

dBc

DR = 10 kbps, FDEV = 10 kHz, ±10 MHz

offset, continuous wave interference

75

dBc

Input 3rd order

intercept point

IIP3

DR = 10 kbps, FDEV = 10 kHz, 1 MHz and

20 MHz offset two tone test, maximum

system gain setting

-25

dBm

RSSI range

RSSI

-120

20

dBm

Sensitivity

@ 433.92 MHz

(typical

configuration)

DR = 1.2 kbps, FDEV = 5 kHz

-122.9

dBm

DR = 1.2 kbps, FDEV = 10kHz

-121.8

dBm

DR = 1.2 kbps, FDEV = 20 kHz

-119.5

dBm

DR = 2.4 kbps, FDEV = 5 kHz

-120.6

dBm

DR = 2.4 kbps, FDEV = 10 kHz

-120.3

dBm

DR = 2.4 kbps, FDEV = 20 kHz

-119.7

dBm

DR = 9.6 kbps, FDEV = 9.6 kHz

-116.0

dBm

DR = 9.6 kbps, FDEV = 19.2 kHz

-116.1

dBm

DR = 20 kbps, FDEV = 10 kHz

-114.2

dBm

DR = 20 kbps, FDEV = 20 kHz

-113.0

dBm

DR = 50 kbps, FDEV= 25 kHz

-110.6

dBm

DR = 50 kbps, FDEV = 50 kHz

-109.0

dBm

DR = 100 kbps, FDEV = 50 kHz

-107.8

dBm

DR = 200 kbps, FDEV= 50 kHz

-103.5

dBm

DR = 200 kbps, FDEV = 100 kHz

-104.3

dBm

DR = 300 kbps, FDEV = 50 kHz

-98.0

dBm

DR = 300 kbps, FDEV = 150 kHz

-101.6

dBm

CMT2380F32

Rev0.9 | 11/65

www.cmostek.com

1.5 Transmitter

Table 7. Transmitter Specifications

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Output power

POUT

Specific matching network is required for

different frequency bands

-20

+20

dBm

Output power step

PSTEP

1

dB

GFSK (Gaussian filter

coefficient)

BT

0.3

0.5

1.0

-

Output power change

with different

temperature

POUT-TOP

Temperature range:-40 to + 85 C

1

dB

Spurious emissions

POUT = +13 dBm,433MHz, FRF<1 GHz

-54

dBm

1 GHz to12.75 GHz, including harmonics

-36

dBm

Harmonic output[1]

for FRF= 433 MHz

H2433

2nd harmonic,+20 dBm POUT

- 46

dBm

H3433

3nd harmonic,+20 dBm POUT

- 50

dBm

Harmonic output[1]

for FRF= 868 MHz

H2868

2nd harmonic,+20 dBm POUT

- 43

dBm

H3868

3nd harmonic,+20 dBm POUT

- 52

dBm

Harmonic output[1]

for FRF= 915 MHz

H2915

2nd harmonic,+20 dBm POUT

- 48

dBm

H3915

3nd harmonic,+20 dBm POUT

- 53

dBm

Harmonic output[1]

for FRF= 433 MHz

H2433

2nd harmonic,+13 dBm POUT

- 52

dBm

H3433

3nd harmonic,+13 dBm POUT

- 52

dBm

Harmonic output[1]

for FRF= 868 MHz

H2868

2nd harmonic,+13 dBm POUT

- 52

dBm

H3868

3nd harmonic,+13 dBm POUT

- 52

dBm

Harmonic output[1]

for FRF= 915 MHz

H2915

2nd harmonic,+13 dBm POUT

- 52

dBm

H3915

3nd harmonic,+13 dBm POUT

- 52

dBm

Notes:

[1]. The harmonic level mainly depends on the matching network. Above parameters are measured based on the

CMT2380F32-EM, users may get different results on their applications.

CMT2380F32

Rev0.9 | 12/65

www.cmostek.com

1.6 RF Operating Mode Switching Time

Table 8. RF Operating Mode Switching Time

Parameter

Symbol

Condition

Min.

Typ.

Max.

Units

RF operating mode

switching time

TSLP-RX[1]

From sleep to RX

1

ms

TSLP-TX[1]

From sleep to TX

1

ms

TSTB-RX

From standby to RX

350

us

TSTB-TX

From standby to TX

350

us

TRFS-RX

From RFS to RX

20

us

TTFS-RX

From TFS to TX

20

us

TTX-RX

From TX to RX

(Needs 2Tsymbol to ramp down)

2Tsymbol

+350

us

TRX-TX

From RX to TX

350

us

Notes:

[1]. TSLP-RX and TSLP-TX are dominated by the crystal oscillator startup time, and the start-up time is to a large degree crystal

dependent.

1.7 RF Frequency Synthesizer

Table 9. RF Frequency Synthesizer

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Frequency range

FRF

760

1020

MHz

380

510

MHz

190

340

MHz

127

170

MHz

Frequency resolution

FRES

25

Hz

Frequency tuning time

tTUNE

150

us

Phase noise @ 433

MHz

PN433

10 kHz deviation

-94

dBc/Hz

100 kHz deviation

-99

dBc/Hz

500 kHz deviation

-118

dBc/Hz

1MHz deviation

-127

dBc/Hz

10 MHz deviation

-134

dBc/Hz

Phase noise @ 868

MHz

PN868

10 kHz deviation

-92

dBc/Hz

100 kHz deviation

-95

dBc/Hz

500 kHz deviation

-114

dBc/Hz

1MHz deviation

-121

dBc/Hz

10 MHz deviation

-130

dBc/Hz

Phase noise @ 915

MHz

PN915

10 kHz deviation

-89

dBc/Hz

100 kHz deviation

-92

dBc/Hz

500 kHz deviation

-111

dBc/Hz

1MHz deviation

-121

dBc/Hz

10 MHz deviation

-130

dBc/Hz

CMT2380F32

Rev0.9 | 13/65

www.cmostek.com

1.8 Requirement on Crystals for RF Section

Table 10. Requirement on Crystals for RF Section

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Crystal frequency[1]

FXTAL

26

MHz

Crystal frequency tolerance[2]

ppm

20

ppm

Load capacitance

CLOAD

15

pF

ESR

Rm

60

Ω

Crystal startup time[3]

tXTAL

400

us

Notes:

[1]. An external 26 MHz reference clock can be used to drive the XI pin directly through a coupling capacitor if such a clock

is available. The peak-to-peak level of the external reference clock is required between 0.3 and 0.7 V.

[2]. It involves:(1) initial tolerance, (2) crystal loading, (3) aging, and (4) temperature changing. The acceptable crystal

frequency tolerance is subject to the bandwidth of the receiver and the RF tolerance between the receiver and its paired

transmitter.

[3]. This parameter is to a large degree crystal dependent.

1.9 Controller Output Features

Table 11. Controller Output Features

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Output high level

VOH

Sourcing 4 mA current, VDD = 3.3V

VDD - 0.25

V

Sourcing 6 mA current, VDD= 3.3V

VDD - 0.60

V

Output low level

VOL

Sinking 4 mA current, VDD = 3.3V

VDD + 0.25

V

Sinking 6 mA current, VDD= 3.3V

VDD + 0.60

V

Output high level

(enhanced mode)

VOHD

Sourcing 8 mA current, VDD = 3.3V

VDD - 0.25

V

Sourcing 12 mA current, VDD = 3.3V

VDD - 0.60

V

Output low level

(enhanced mode)

VOLD

Sinking 8 mA current, VDD = 3.3V

VDD + 0.25

V

Sinking 12 mA current, VDD = 3.3V

VDD + 0.60

V

Notes:

1. The maximum total current of IOH and IOL (sum of all pins) shall not exceed 40 mA to meet the specified maximum voltage

drop.

2. The maximum total current of IOH and IOL (sum of all pins, enhanced mode) shall not exceed 100 mAto meet the specified

maximum voltage drop.

CMT2380F32

Rev0.9 | 14/65

www.cmostek.com

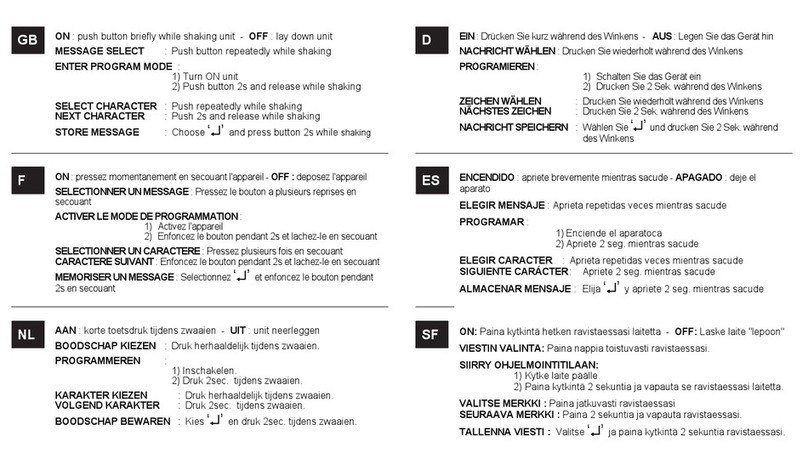

Figure 2. Controller I/O Driving Ability

1.10 Controller Input Features(P0, P1, P2 and P3 Reset)

Table 12. Controller Input Features(P0, P1, P2 and P3 Reset)

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Output high level

VIH

VDD = 1.8 V

1

1.1

1.2

V

VDD = 3.3 V

1.8

2

2.2

V

Output low level

VIL

VDD = 1.8 V

0.6

0.7

0.8

V

VDD = 3.3 V

1.1

1.3

1.5

V

Input hysteresis range

(VIH-VIL)

VHYS

VDD = 1.8 V

0.4

0.4

0.4

V

VDD = 3.3 V

0.7

0.7

0.7

V

Pull-up resistor

RPUP

Pull-up enabled

80

kΩ

Input capacitance

Sinking 12 mA current,VDD = 3.3 V

5

pF

1.11 Port External Input Sampling Requirements (Timer Gate/Timer

Clock)

Table 13. Port External Input Sampling Requirements (Timer Gate/Timer Clock)

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

External interrupt input pulse width

TINT

VDD = 1.8 V

30[1]

ns

VDD = 3.3 V

30[1]

ns

Timer 4/5/6 capture pulse width

(FSYS=4MHz)

TCAP

VDD = 1.8 V

0.5

us

VDD = 3.3 V

0.5

us

Timer 0/1/2/4/5/6 external clock

input (FSYS=4MHz)

TCLK

VDD = 1.8 V

PCLK/2

MHz

VDD = 3.3 V

PCLK/2

MHz

PCA external input clock

TPCA

VDD = 1.8 V

PCLK/8

MHz

VDD = 3.3 V

PCLK/8

MHz

Notes:

[1]. It's the minimum external interrupt input pulse width used in the practical test for triggering the interrupt. It can support

triggering the interrupt with even shorter pulse width based on the chip capability.

Low drive

High drive

Low drive

High drive

VOL @ VDD = 3.3 V

VOH @ VDD = 3.3 V

Current (mA)

Voltage (V)

Voltage (V)

Current (mA)

CMT2380F32

Rev0.9 | 15/65

www.cmostek.com

1.12 Port Leakage Features (P0, P1, P2 and P3)

Table 14. Port Leakage Features (P0, P1, P2, and P3)

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Leakage current

Ilkg(Px,y)

VDD: 1.8 to 3.6V

±50

nA

Notes:

[1]. Unless otherwise specified, the leakage current is measured with GND or VDD applied to the corresponding pin.

[2]. The pin to be tested must be set to input mode.

1.13 Controller Power Consumption Features

Table 15. Controller Power Consumption Features

Parameter

Symbol

Condition

Note

Typ.

Max.

Unit

Operating current

when program

running in SRAM

IDD-RAM

VCORE = 1.55 V, VDD = 3.3 V. All

peripheral clock sources are off.

Run While(1) in SRAM with RCH

as clock source.

4 MHz

220

uA

8 MHz

400

uA

16 MHz

740

uA

24 MHz

1080

uA

32 MHz

1400

uA

Core mark operating

current

IDD-Mark

VCORE = 1.55 V, VDD = 3.3 V. All

peripheral clock sources are off.

Run Core Mark in Flash with RCH

as clock source

4 MHz

670

uA

8 MHz

1300

uA

16 MHz

2380

uA

24 MHz

3410

uA

32 MHz

Flash Wait=1

3530

uA

Operating current

IRUN

VCORE = 1.55 V, VDD = 3.3 V. All

peripheral clock sources are on.

Run While(1) in Flash with RCH as

clock source.

4 MHz

700

880

uA

8 MHz

1350

1600

uA

16 MHz

2500

3000

uA

24 MHz

3600

4300

uA

VCORE = 1.55 V, VDD = 3.3 V. All

peripheral clock sources are off.

Run While(1) in Flash with RCH as

clock source.

4 MHz

550

750

uA

8 MHz

1050

1300

uA

16 MHz

1900

2400

uA

24 MHz

2700

3300

uA

32 MHz

Flash Wait=1

2850

3000

uA

Sleep current

ISLP

VCORE = 1.55 V,VDD = 1.8~3.6 V.

4 MHz

260

280

uA

CMT2380F32

Rev0.9 | 16/65

www.cmostek.com

Parameter

Symbol

Condition

Note

Typ.

Max.

Unit

All peripheral clock sources are on

with RCH as clock source.

8 MHz

500

520

uA

16 MHz

950

970

uA

24 MHz

1400

1420

uA

VCORE = 1.55 V, VDD = 1.8 ~ 3.6 V.

All peripheral clock sources are

off. RCH clock source is used.

4 MHz

110

125

uA

8 MHz

190

210

uA

16 MHz

330

360

uA

24 MHz

470

500

uA

32 MHz

580

610

uA

LP operating current

ILP-RUN

VCORE = 1.55 V, VDD = 1.8 ~ 3.6 V.

All peripheral clock sources are

on. Run While(1) in Flash with

XTAL (32768Hz, Driver = 1) as

clock source.

TA = -40 ~ 25 ℃

7

9

uA

TA = 50 ℃

7.3

9.2

uA

TA = 85 ℃

8.9

11.3

uA

ILP-RUN

VCORE = 1.55V, VDD = 1.8 ~ 3.6 V.

All peripheral clock sources are

off. Run While(1) in Flash with

XTAL (32768 Hz, Driver = 1) as

clock source.

TA = - 40 ~ 25 ℃

6

8

uA

TA = 50 ℃

6.1

8.2

uA

TA = 85 ℃

7.7

10.1

uA

LP sleep current

ILP-SLP

VCORE = 1.55 V, VDD = 1.8 ~ 3.6 V.

All peripheral clock sources are

on. Run While(1) in Flash with

XTAL (32768 Hz, Driver = 1) as

clock source.

TA = - 40 ~ 25 ℃

3.3

3.5

uA

TA = 50 ℃

3.6

3.8

uA

TA = 85 ℃

5.4

5.8

uA

ILP-SLP

VCORE = 1.55 V, VDD = 1.8 ~ 3.6 V.

All peripheral clock sources are off

(except LPTimer and RTC). Run

While(1) in Flash with XTAL

(32768Hz, Driver = 1) as clock

source.

TA = - 40 ~ 25 ℃

2.2

2.4

uA

TA = 50 ℃

2.5

2.6

uA

TA = 85 ℃

4.2

4.6

uA

Deep sleep current

IDEEP-SLP

VCORE = 1.55 V, VDD = 1.8 ~ 3.6 V.

All peripheral clock sources are

off, except LPTimer, WDT and

RTC.

TA = - 40 ~ 25 ℃

1.5

1.65

uA

TA = 50 ℃

1.85

2.2

uA

TA = 85 ℃

3.5

4.2

uA

VCORE = 1.55 V, VDD = 1.8 ~ 3.6 V.

All peripheral clock sources are

off, except WDT.

TA = - 40 ~ 25 ℃

1.2

1.3

uA

TA = 50 ℃

1.5

1.8

uA

TA = 85 ℃

3.1

3.7

uA

VCORE = 1.55 V, VDD = 1.8 ~ 3.6 V.

All peripheral clock sources are

off, except LPTimer.

TA = - 40 ~ 25 ℃

0.9

1

uA

TA = 50 ℃

1.1

1.3

uA

TA = 85 ℃

2.6

3

uA

CMT2380F32

Rev0.9 | 17/65

www.cmostek.com

Parameter

Symbol

Condition

Note

Typ.

Max.

Unit

VCORE = 1.55 V, VDD = 1.8~3.6V. All

peripheral clock sources are off,

except RTC.

TA = - 40 ~ 25 ℃

1.0

1.1

uA

TA = 50 ℃

1.2

1.5

uA

TA = 85 ℃

2.6

3.4

uA

VCORE = 1.55 V,VDD = 1.8 ~ 3.6 V.

All peripheral clock sources are

off.

TA = - 40 ~ 25 ℃

0.42

0.6

uA

TA = 50 ℃

0.75

0.95

uA

TA = 85 ℃

2.2

2.7

uA

CMT2380F32

Rev0.9 | 18/65

www.cmostek.com

1.14 POR/BOR Features

VBOR_hys+

VBOR_hys-

unknown unknown

1.65V

1.50v

BOR_5V

VCC

Vth ~0.8v

Figure 3. POR/BOR Features

Notes:

1. POR/BOR detects the VDD voltage.

2. It detects the threshold only instead of VDD power-up and power-down slew rate.

3. The detection threshold is the same no matter the VDD is powering on or off. A reset pulse is triggered when VDD is lower

than the threshold.

4. In case a reset pulse is generated, the pulse duration will not be less than Treset to guarantee a complete system reset.

Table 16. POR/BOR Features

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

POR release voltage (power-up process)BOR

detection voltage (power-down process)

VPOR

1.45

1.50

1.65

V

1.15 Controller External XTH Oscillator

Table 17. Controller External XTH Oscillator

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Crystal frequency

FFCLK

4

32

MHz

Equivalent series

resistance

ESRFCLK

32 MHz crystal

30

60

Ω

4 MHz crystal

400

1500

Ω

Load capacitance

CFCLK

The two pins of the crystal oscillator are

connected separately.

12

24

pF

Duty cycle

DCFCLK

40

50

60

%

Current consumption[1]

IDD

32 MHz crystal, CFCLK= 12 pF, ESRFCLK = 30 Ω

600

uA

Startup time

TFstart

4 MHz~32 MHz

200

400

us

Notes:

[1]. It is the current consumption when configure XTH_CR_Driver = 0b1110.

Treset

Treset

VDD

CMT2380F32

Rev0.9 | 19/65

www.cmostek.com

1.16 Controller External 32.768 kHz Oscillator

Table 18. Controller External 32.768 kHz Oscillator

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Crystal frequency

FSCLK

32.768

kHz

Equivalent series

resistance

ESRSCLK

65

85

kΩ

Load capacitance

CSCLK

The two pins of the crystal oscillator

are connected separately.

0

12

pF

Clock duty cycle

DCFCLK

40

50

60

%

Current consumption[1]

IDD

CSCLK =12pF,ESRSCLK = 65kΩ

0.6

1

uA

Startup time

Tstart

CSCLK =12pF,ESRSCLK = 65

kΩ,40%~60% duty cycle

500

ms

Notes:

[1]. The operating current is measured under the condition at XTL_CR_Driver = 0b0011 and ESR=65kΩ.

1.17 Controller Internal RCH Oscillator

Table 19. Controller Internal RCH Oscillator

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Internal high speed oscillating

frequency

FMCLK

4

4.0

32

MHz

8.0

16.0

22.12

24.0

Startup time

(not including software calibration)

TMstart

FMCLK = 4 MHz

6.0

us

FMCLK = 8 MHz

4.0

us

FMCLK = 16 MHz

3.0

us

FMCLK = 24 MHz

2.5

us

Current consumption

IMCLK

FMCLK = 4 MHz

80

uA

FMCLK = 8 MHz

100

uA

FMCLK = 16 MHz

120

uA

FMCLK = 24 MHz

140

uA

Clock duty cycle

DCMCLK

45

50

55

%

Frequency tolerance

DEVMCLK

VDD = 1.8 ~ 3.6 V,

TA = -40 ~ +85 ℃

-2.5

+2.5

%

VDD = 1.8 V ~ 3.6 V,

TA = - 20 ~ + 50 ℃

-2.0

+ 2.0

%

CMT2380F32

Rev0.9 | 20/65

www.cmostek.com

1.18 Controller Internal RCL Oscillator

Table 20. Controller Internal RCL Oscillator

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Internal high speed

oscillating frequency

FACLK

38.4

kHz

32.768

Startup time

TACLK

100

us

Current consumption

IACLK

0.25

uA

Clock duty cycle

DCACLK

25

50

75

%

Frequency tolerance

DEVACLK

VDD = 1.8 ~ 3.6V,

TA = - 40 ~ + 85 ℃

-2.0

+2.0

%

VDD = 1.8 ~ 3.6V,

TA = - 20 ~ + 50 ℃

-1.5

+1.5

%

1.19 Controller Flash Features

Table 21. Controller Flash Features

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Sector endurance

ECFlash

20

kcycles

Byte Program Time

TProg

6

7.5

us

Sector erase time

TErase

4

5

ms

Chip erase time

30

40

ms

Data retention

RETFlash

TA = +25 °C

20

Year

TA = +85 °C

10

Year

1.20 Controller Low Power Mode Recover Time

Table 22. Controller Low Power Mode Recover Time

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Return to active mode from

deep sleep mode

TWakeup

Regulated 1.5 V, TA = + 25°C, 4 MHz

4.0

us

Regulated 1.5 V, TA = + 25°C, 8 MHz

3.1

us

Regulated 1.5 V, TA = + 25°C, 16 MHz

2.8

us

Regulated 1.5 V, TA = + 25°C, 24 MHz

2.7

us

This manual suits for next models

1

Table of contents

Other CMOSTEK Microcontroller manuals

Popular Microcontroller manuals by other brands

PIKODER

PIKODER USB2PPM user manual

Silicon Laboratories

Silicon Laboratories C8051F12 Series manual

Bosch

Bosch XDK 110 Getting started

Silicon Laboratories

Silicon Laboratories EFM32 quick start guide

Equinox Systems

Equinox Systems Flash 8051 Getting started

Texas Instruments

Texas Instruments MSP432 user guide