CMOSTEK CMT2218-2219 User manual

AN160

Rev 0.8 | 1/12

www.cmostek.com

Overview

This document provides the schematic and PCB layout design guidelines for users engaging in the development based on the

CMT2218B/2219B receiver chip, which is part of the CMOSTEK NextGenRFTM product family. The document aims for guiding

users to quickly achieve target performance objectives such as improving sensitivity, reducing power consumption and system

cost, improving anti-interference ability.

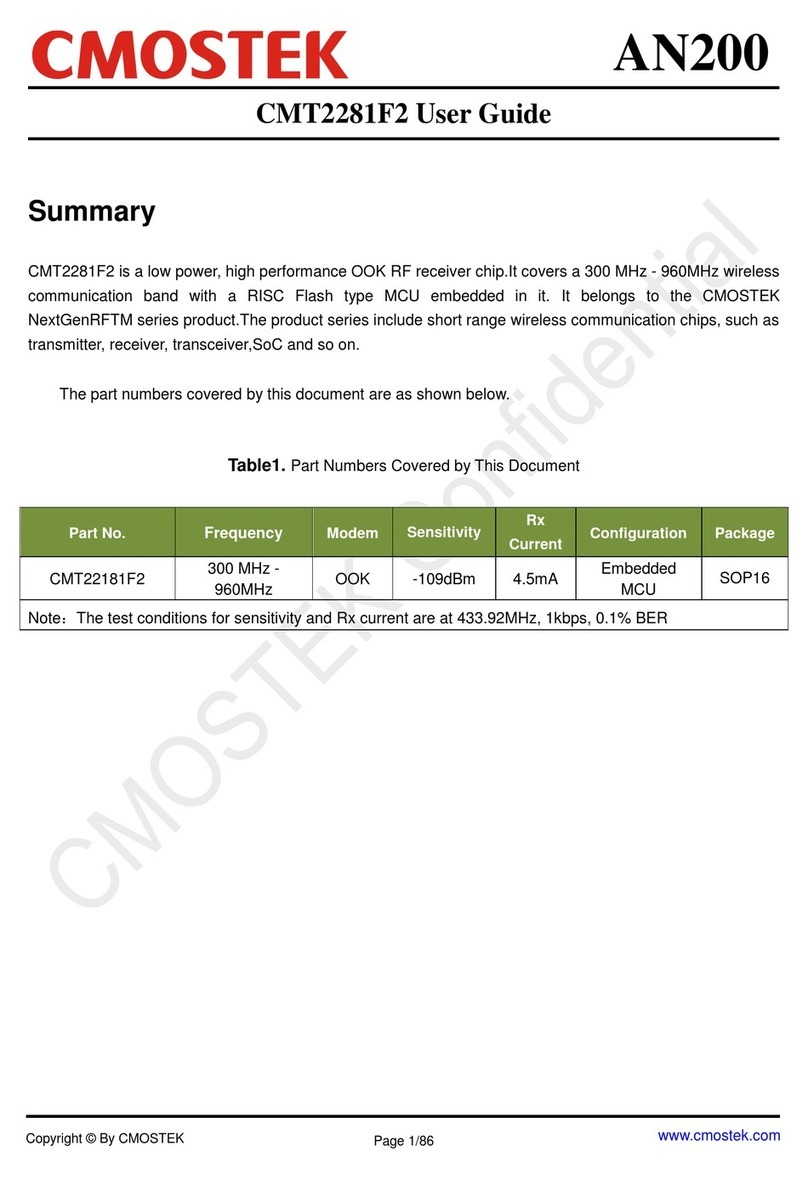

The product models covered in this document are shown in the table below.

Table 1. Product Models Covered in This Document

Product Model

Frequency Range

Modulation Method

Chip Function

Configuration Method

Package

CMT2218B

127 - 1020 MHz

FSK

Receiving

Programming

QFN16

CMT2219B

127 - 1020 MHz

(G)FSK/OOK

Receiving

Register

QFN16

AN160

CMT2218-2219 User Guide for Schematic and PCB Layout Design

Copyright ©By CMOSTEK

AN160

Rev 0.8 | 2/12

www.cmostek.com

Table of Contents

1RF Input Matching............................................................................................................................. 3

2Crystal Circuit Design ...................................................................................................................... 6

3Digital Signal Design........................................................................................................................ 7

4Power and Ground Design............................................................................................................... 8

4.1 Power Filter Circuit Design.................................................................................................................................8

4.2 Ground Plane Design.........................................................................................................................................8

5Sensitivity Optimization................................................................................................................... 9

6Test Circuit Design ........................................................................................................................... 9

7Design Checklist............................................................................................................................. 10

8Revise History..................................................................................................................................11

9Contacts........................................................................................................................................... 12

AN160

Rev 0.8 | 3/12

www.cmostek.com

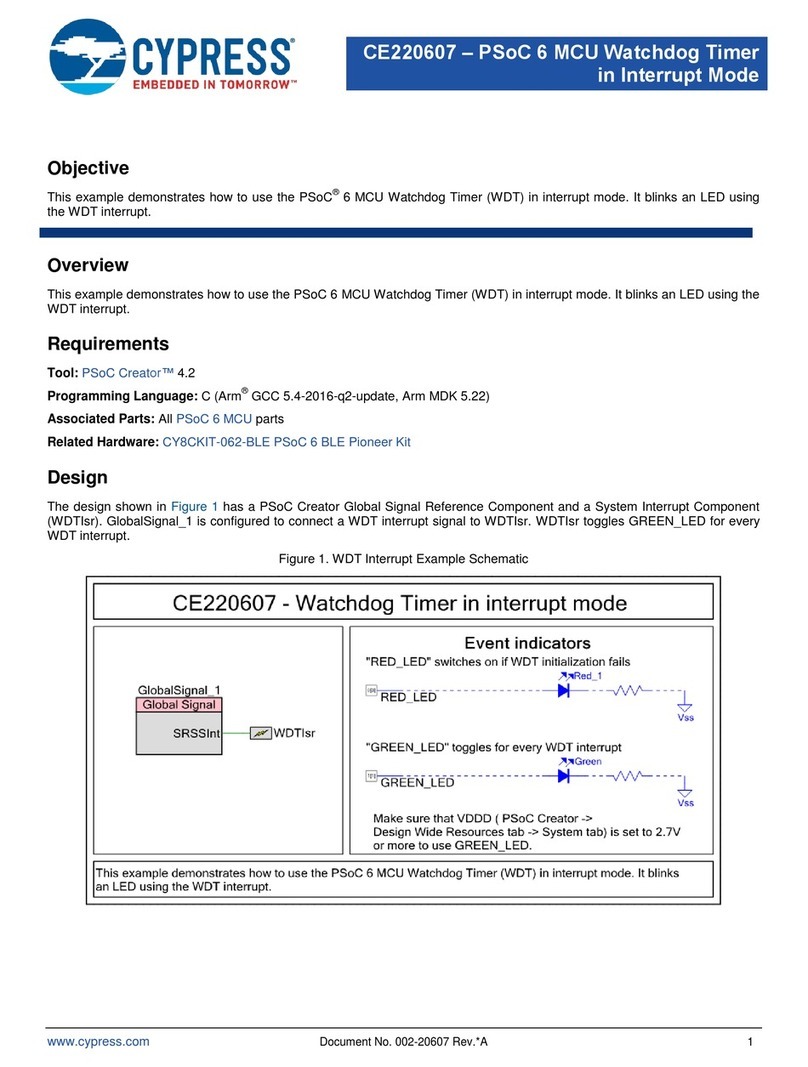

1 RF Input Matching

The matching network achieves high receiving sensitivity performance through the impedance matching between the antenna

and chip RF input. The LNA of the CMOSTEK NextGenRFTM CMT2218B/2219B is a differential port, using L1 and BALUN

network (L2, C2, L3 and C3) to achieve the impedance matching between the single-ended antenna and differential LNA. In

general, a parallel resonant filter network composed of L4 and C4 along with the input end of antenna can filter out the

interference to the receiver caused by complex electromagnetic environment. The reference schematic is shown in the figure

below.

Figure 1. CMT2218B/2219B Application Schematic Diagram

The followings are descriptions of the above figure.

1. L1, L2, C2, L3 and C3 form a matching network.

2. L4 and C4 form a parallel resonant filter network.

3. P1 is an antenna connector.

4. C5 and C6 are crystal load capacitors.

5. C7 and C8 are power supply decoupling capacitors.

The component parameter values to have matching between the CMT2218B/2219B differential LNA and the single-ended

antenna of 50 Ωat different operating frequencies are shown in the table below.

AN160

Rev 0.8 | 4/12

www.cmostek.com

Table 2. Typical Application Schematic Components

Label

Description

Component Value

Unit

Supplier

433 MHz

868 MHz

915 MHz

R1[1]

±10%, 0603, 1/8 W

10

2.2

2.2

kΩ

-

C2

±5%, 0603 NP0, 50 V

4.7

2.2

2.2

pF

-

C3

±5%, 0603 NP0, 50 V

4.7

2.2

2.2

pF

-

C4

±5%, 0603 NP0, 50 V

4.7

2.2

2.2

pF

-

C5

±5%, 0603 NP0, 50 V

24

24

24

pF

-

C6

±5%, 0603 NP0, 50 V

24

24

24

pF

-

C7

±5%, 0603 NP0, 50 V

470

2

pF

-

C8

±5%, 0603 NP0, 50 V

0.1

uF

-

L1

± 5%, 0603 multilayer chip inductor

68

12

12

nH

-

L2

± 5%, 0603 multilayer chip inductor

27

15

12

nH

Sunlord

L3

± 5%, 0603 multilayer chip inductor

27

15

12

nH

Sunlord

L4

± 5%, 0603 multilayer chip inductor

27

15

12

nH

Sunlord

Y1

± 20 ppm, SMD32*25 mm

26

MHz

EPSON

U1

CMT2218B/2219B, ultra-low power

sub-1 GHz RF receiver

-

-

CMOSTEK

Note:

[1]. Only applications of CMT2218B require the pull up resistor R1 on SDIO port.

In practical applications, due to factors such as product structure and physical space, the resistance of a user antenna is often

not 50 Ω. In the cases, an additional LC circuit can be added after P1 based on the application schematic in Figure 1 to achieve

the impedance matching between P1 (50Ω) and the user antenna. This way, users only need to adjust parameters of the added

LC, and the other component values keep as table 2, which helps simplifying the matching adjusting procedure much.

AN160

Rev 0.8 | 5/12

www.cmostek.com

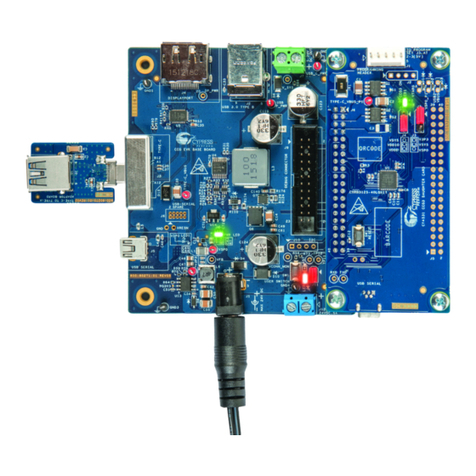

Figure 2. Matching Network Layout Design Reference

AN160

Rev 0.8 | 6/12

www.cmostek.com

Figure 2 shows the matching network layout of a receiver product based on the layout design of the CMT2218B/19B-EM. Users

need pay special considerations on the following items.

1. Keep the RF signal path as short as possible to reduce the energy loss of signal transmission.

2. Place L1, L2, L3, C2, and C3 as close as possible to the RF input port.

3. Since a chip has a relatively high impedance at the RF input end, the transmission line close to the RF input end should use

relatively narrower line (a line with 0.2 mm width is used in the reference design in the above figure). The transmission line

between the BALUN network and the antenna interface P1 uses 1 mm wide transmission line to have impedance matching with

the 50 Ω antenna.

4. Try not to have screen silk on RF devices and traces.

5. Ground plane and RF traces should be as flat as possible to reduce impedance fluctuations on the transmission line.

2 Crystal Circuit Design

The recommended crystal specifications are as follows.

Table 3. Crystal Oscillator Specifications

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Crystal frequency[1]

FXTAL

26

MHz

Crystal frequency accuracy[2]

VIN

±20

ppm

Load capacitance

CLOAD

15

pF

Crystal equivalent resistance

Rm

60

Ω

Crystal start-up time[3]

tXTAL

400

us

Notes:

[1]. This product series supports driving the XI pin directly by an external clock (a series connected coupling capacitor is

required) with the peak-to-peak amplitude limited between 0.3 and 0.7 V.

[2]. This refers to all frequency accuracy tolerances, including (1) initial tolerance (2) crystal loading tolerance (3) aging

tolerance and (4) temperature variation tolerance. The acceptable crystal tolerance depends on factors such as RF

frequency, channel spacing, bandwidth settings.

[3]. This parameter is related much to the crystal used.

AN160

Rev 0.8 | 7/12

www.cmostek.com

Figure 3. Crystal Circuit Layout Design

The below design considerations should be taken into account.

1. Variations in parasitic capacitance due to different PCB designs need to be considered to guarantee the frequency error

is within the allowable range.

2. A crystal should be placed as close as possible to the pin XI of a receiving chip to reduce the trace length with the

purpose of reducing the possibility of external interference to the crystal and reducing the required distributed

capacitances, to improve frequency accuracy.

3. The crystal circuit should be placed as far away as possible from RF signals, digital signals or other high-frequency and

large-interference signals. Place areas of ground plane as large as possible around the crystal circuit for isolation to

prevent interference to the RF signal or the impact on the reference clock quality caused by the interference.

4. The metal housing of a crystal needs to be grounded.

3 Digital Signal Design

The digital signal traces includes CSB, FCSB, SCLK, SDIO and GPIO1-3. As series ports of the CMT2218B and CMT2219B are

different, users need to pay following considerations on PIN10 and PIN12.

The CMT2218B provides a 3-wire series port mechanism using CSB, SCLK and SDIO. Please be noted that SDIO (PIN10) of

CMT2218B needs an external pull-up resistor, however it's not needed in the CMT2219B. Please use the programming tool

provided by CMOSTEK to configure the CMT2218B.

The CMT2219B provides a 4-wire series port mechanism using CSB, FCSB, SCLK and SDIO. Please be noted that PIN12 is

FCSB pin in CMT2219B, however it is unused NC pin in CMT2218B.

AN160

Rev 0.8 | 8/12

www.cmostek.com

The GPIO1 pin of CMT2218B is fixed as Data Out output, the GPIO2 pin is fixed as Rx Active output and the GPIO3 pin output

type is configurable. Please refer to CMOSTEK RFPDK for more details.

Moreover, please be noted the following wiring considerations.

1. Digital signal traces should be as far away as possible from the RF and crystal trace areas.

2. Place areas of ground plane as large as possible around digital signals to reduce crosstalk.

4 Power and Ground Design

4.1 Power Filter Circuit Design

To reduce the impact from the noise and ripple of the power supply, users should add a suitable filter capacitor to the power

supply pin of the chip.

Figure 4. Power Supply Design

4.2 Ground Plane Design

The following ground plane considerations should be taken into account.

1. Place areas of ground plane as large and continuous as possible.

2. To reduce the EMI radiated by the power supply loop externally, the ground trace design should in best effort minimize the

space of the path through which the current loop backs to the power supply.

3. Place a ground plane as large as possible under the chip to reduce the impact on the continuity of the RF output

transmission line impedance. Place one to several GND vias on the chip substrate as shown in the below figure.

4. On the PCB edges, place as many as possible vias with no more than λ/10 in size to reduce the higher harmonic

emissions from the PCB edges.

AN160

Rev 0.8 | 9/12

www.cmostek.com

Figure 5. Ground Plane Design

5 Sensitivity Optimization

In addition to impedance matching and filtering, the impact of antenna design on sensitivity should be considered as well. For

example, a commonly used monopole antenna actually is a dipole antenna, which is formed half by a λ/4 antenna and half by a

virtual λ/4 antenna of ground plane. Therefore, for a monopole antenna, the performance depends on the size of the ground

plane as well. Users can choose different types of monopole antenna such as PCB antennas, chip antennas, glue stick antennas,

wire antennas based on overall considerations of cost, performance, time to market, etc.

6 Test Circuit Design

Users can update the CMT2218B function via programming the chip (CMT2219B does not support it). Therefore, test points of

CSB, SCLK, SDIO, VDD and GND should be reserved in users' applications to support the functions described below.

When using CMT2218B, reserve test points of CSB, SCLK, SDIO, VDD, GND to accomplish the following two functions.

1. Update the chip's function via programming during production.

2. Read and get the chip configuration.

AN160

Rev 0.8 | 10/12

www.cmostek.com

7 Design Checklist

Users can check the actual design with the below checklist to make sure they are well considered.

Table 4. Design Checklist

RF Input Design

□

Whether the RF signal path is as short as possible to reduce the RF signal loss.

□

Whether the components of matching network are placed as closely as possible and whether the matching network

is placed as closely as possible to the RF input port.

□

Whether the amount of impedance is considered when choosing the trace width of the RF transmission line (a 1

mm wide transmission line is used for about 50 Ω impedance).

□

Whether users have tried to prevent silk screen printing on RF devices and traces.

□

Whether the ground plane and RF trace have been as flat as possible.

□

Whether the antenna length is close to λ/4.

□

Whether the crystal is as far away as possible from the antenna.

Crystal Circuit Design

□

Whether the crystal is placed as close as possible to the XI pin to reduce the trace parasitic capacitance.

□

Whether the crystal circuit is placed as far away as possible from strong interference sources such as digital

signals and whether areas of ground plane are placed as large as possible around the crystal circuit.

□

Whether the metal housing is grounded.

Digital Signal Design

□

Whether digital signal traces are as far away as possible from the RF and crystal trace areas.

□

Whether areas of ground plane are as large as possible around digital signals to reduce crosstalk.

□

Power and Ground Design

□

Whether more than one GND vias are placed on the chip substrate.

□

Whether the power supply filter capacitor is placed as close as possible to the power supply pin of the chip on the

layout.

□

Whether areas of ground plane are placed as large and continuous as possible.

□

Whether the ground trace design minimizes the space of the path through which the current loop backs to the

power supply, to reduce the EMI radiated by the power supply loop externally.

□

Whether a ground plane is placed as large as possible under the chip to reduce the impact on the continuity of the

RF output transmission line impedance and to improve ESD performance.

□

On the PCB edges, whether as many as possible vias with no more than λ/10 in size are placed to reduce the

higher harmonic emissions from the PCB edges

Test Circuit Design

□

Whether test points for programming are reserved in the PCB design.

AN160

Rev 0.8 | 11/12

www.cmostek.com

8 Revise History

Table 5. Revise History Records

Version No.

Chapter

Description

Date

0.7

All

Initial version

2017-09-15

0.8

Section 1

In Table 2, correct some component description and values

(translation error).

2020-12-07

AN160

Rev 0.8 | 12/12

www.cmostek.com

9 Contacts

CMOSTEK Microelectronics Co., Ltd. Shenzhen Branch

Address: 30th floor of 8th Building, C Zone, Vanke Cloud City, Xili Sub-district, Nanshan, Shenzhen, GD, P.R. China

Tel: +86-755-83231427

Post Code: 518055

Sales: sales@cmostek.com

Supports: sup[email protected]

Website: www.cmostek.com

The information furnished by CMOSTEK is believed to be accurate and reliable. However, no responsibility is assumed for

inaccuracies and specifications within this document are subject to change without notice. The material contained herein is

the exclusive property of CMOSTEK and shall not be distributed, reproduced, or disclosed in whole or in part without prior

written permission of CMOSTEK. CMOSTEK products are not authorized for use as critical components in life support

devices or systems without express written approval of CMOSTEK. The CMOSTEK logo is a registered trademark of

CMOSTEK Microelectronics Co., Ltd. All other names are the property of their respective owners.

Copyright. CMOSTEK Microelectronics Co., Ltd. All rights are reserved.

This manual suits for next models

2

Table of contents

Other CMOSTEK Microcontroller manuals