Cray X-MP Series User manual

c:

RESEARCH

J

INC.

Any

shipment

to

a

country

outside

of

the

United States requires a U.S. Government

export

license.

CRAY COMPUTER SYSTEMS

CRAY X-MP SERIES

MODELS

22

&

24

MAINFRAME REFERENCE

MANUAL

HR-0032

Copyright© 1982, 1984

by

CRAY RESEARCH, INC. This manual

or

parts thereof may

not

be reproduced in any form without

permission of CRAY RESEARCH, INC.

E i

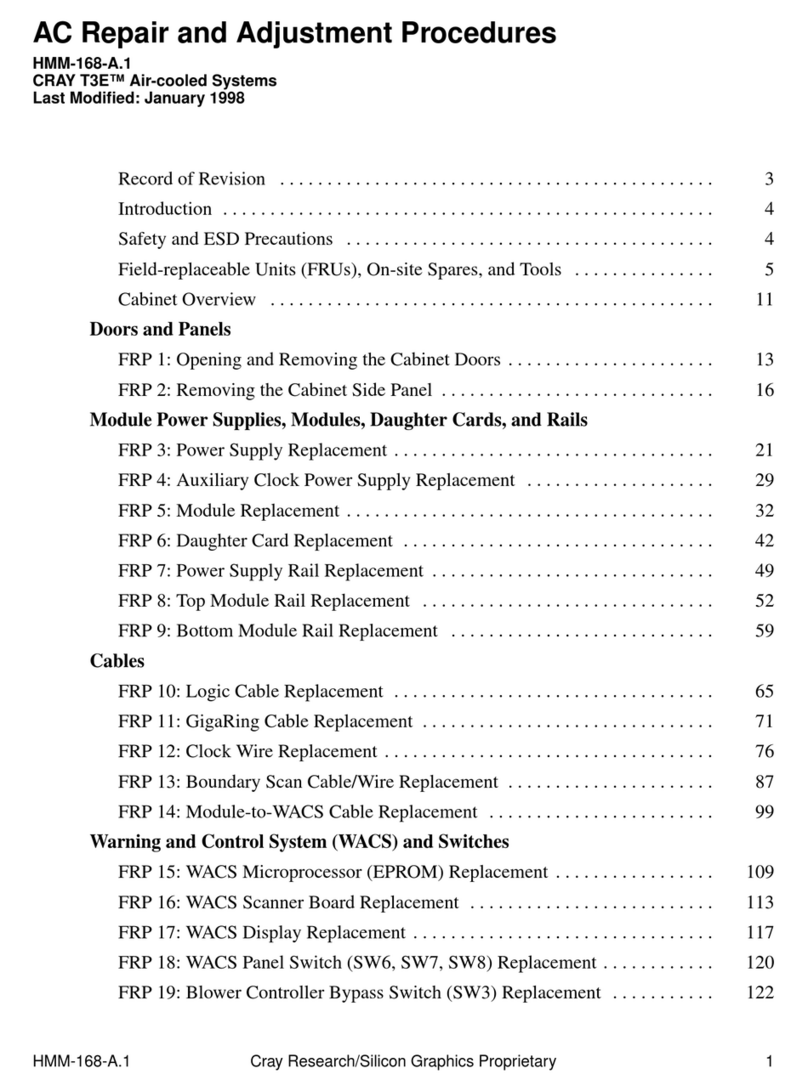

RECORD OF REVISION

~ESEA~CHJ

INC.

PUBLICATION

NUMBER

HR-0032

Each time

thil

manuel il revised and reprinted, all

chan~

issued against

the

previous version in

the

form

of

change packets are

incorporated into

the

new version and

the

new version IS

..

Igned an alphabetic level. Between reprints, changes may be issued

against

the

current

version in

the

form of ch.ange peckets. Each change packet

is

assigned 8 numeric designator, starting with

Ol

for

the

first change packet

of

each revillon level.

Every

P9

changed

by

a reprint

or

by

a change packet has

the

revision level

and

change packet number in

the

lower righthand

corner. Changes

to

part

of

8

P8SlI

are noted

bY

a change bar along

the

margin

of

the

page. A change bar in

the

margin opposite

the

page number indicates

that

the

entire page is new; a

dot

in

ttle same place indicates

that

information hasbeen moved from

one

page

to

another,

but

has

not

otherwise

changed.

Requests for copies

of

Crav Research, Inc. publications and comments

about

these publications should

be

directed to:

CRAY RESEARCH, INC.,

1440

Northland Drive,

Mendota Heights, Minnesota

55120

Revision

A

BR-0032

Description

November, 1982 -

Original

printing.

July,

1984 -

Reprint

with

revision.

Instructions

were added

for

hardware

performance

monitoring

and

SECDED

maintenance

functions.

Information

was

also

added

to

explain

how

the

Second

Vector

Logical

functional

unit

is

used

although

this

functional

unit

is

not

available

on

all

systems.

Numerous

technical

and

editorial

changes

and

correccions

were

also

made.

This

revision

obsoletes

all

previous

printings.

ii

A

PREFACE

This

publication

describes

the

functions

of

CRAY

X-MP

Series

dual-processor

computer

systems,

models

22

and

24.

It

is

written

to

assist

programmers

and

engineers

and

assumes

a

familiarity

with

digital

computers.

The

manual

describes

the

overall

computer

system,

its

configurations,

and

equipment.

It

also

describes

the

operation

of

the

Central

Processing

Units

that

execute

instructions,

provide

memory

protection,

report

hardware

exceptions,

and

provide

interprocessor

communications

within

the

computer

systems.

Details

of

the

I/O

Subsystem,

the

disk

storage

units,

and

the

Solid-state

Storage

Device

are

given

in

the

following

publications:

HR-0030

HR-0630

HR-003l

I/O

Subsystem

Hardware

Reference

Manual

Mass

Storage

Subsystem

Hardware

Reference

Manual

Solid-state

Storage

Device

(SSO@)

Reference

Manual

HR-0032

///////////////////////////////////////////////////////

WARNING

This

equipment

generates,

uses,

and

can

radiate

radio

frequency

energy

and

if

not

installed

and

used

in

accordance

with

the

instructions

manual,

may

cause

interference

to

radio

communications.

It

has

been

tested

and

found

to

comply

with

the

limits

for

a

Class

A

computing

device

pursuant

to

Subpart

J

of

Part

15

of

FCC

Rules,

which

are

designed

to

provide

reasonable

protection

against

such

interference

when

operated

in

a

commercial

environment.

Operation

of

this

equipment

in

a

residential

area

is

likely

to

cause

interference

in

which

case

the

user

at

his

own

expense

will

be

required

to

take

whatever

measures

may

be

required

to

correct

the

interference.

///////////////////////////////////////////////////////

iii

A

CONTENTS,

PREFACE

1.

2.

SYSTEM

DESCRIPTION

•

INTRODUCTION

•

CONVENTIONS

Italics

•

Register

conventions

Number

conventions

Clock

per

iod

SYSTEM

COMPONENTS

Central

Processing

Units

Interfaces

I/O

Subsystem

•

Disk

storage

units.

Solid-state

Storage

Device

Condensing

units

Power

distribution

units

Motor-generator

units

•

SYSTEM

CONFIGURATION

•

CPU

SHARED

RESOURCES

•

INTRODUCTION

•

CENTRAL

MEMORY

•

Memory

organization

•

Memory

addressing

•

Memory

addressing

for

6-co1umn

mainframe

•

Memory

addressing

for

12-co1umn

mainframe

Memory

access

•

Conflict

resolution

Bank Busy

conflict

Simultaneous

Bank

conflict

Section

Access

conflict

•

Memory

access

priorities

•

16-bank

phasing

•

Memory

error

correction

•

INTER-CPU

COMMUNICATION

SECTION

Real-time

clock

•

Inter-CPU

communication

and

control

•

Shared

Address

and

Shared

Scalar

registers

•

Semaphore

registers

HR-0032 v A

iii

1-1

1-1

1-4

1-4

1-4

1-4

1-4

1-5

1-5

1-7

1-9

1-11

1-12

1-13

1-14

1-15

1-16

2-1

2-1

2-1

2-2

2-3

2-3

2-4

2-4

2-7

2-7

2-7

2-7

2-7

2-8

2-8

2-10

2-10

2-11

2-12

2-12

2.

CPU

SHARED

RESOURCES

(continued)

3.

CPU

INPUT/OUTPUT

SECTION

• • • • • • • • • • • • • •

Data

transfer

for

Solid-state

Storage

Device

Data

transfer

for

I/O

Subsystem

• • • • • •

6 Mbyte

per

second

channels

• • • • •

Multi-CPU programming • • • • • •

~

6 Mbyte

per

second

channel

operation

••••

•

Input

channel

programming • • • • • •

Input

channel

error

conditions

••••••

Output

channel

programming

••••

Programmed

master

clear

to

external

device

Memory

access

• • • • •

I/O

lockout

• • • • • • • • • •

Memory

bank

conflicts

• • •

I/O

memory

conflicts

.......

. . .. . ...

. ...

· ....

. ..

·..

·.. ...

· .

· .

·..

I/O

memory

request

conditions

•

I/O

memory

addressing

• • • • • .....

CPU

CONTROL

SECTION

.. ... .. ... .. . .. .. ... . .

INTRODUCTION

• • • • • • • • •

INSTRUCTION

ISSUE

AND

CONTROL

Program

Address

register

Next

Instruction

Parcel

register

Current

Instruction

Parcel

register

Lower

Instruction

Parcel

register

•

Instruction

buffers

.,

.

EXCHANGE

MECHANISM

• • • • • • • • •

Exchange

package

Processor

number

vector

not

used

(VNU)

..

Enable

second

vector

logical

(ESVL)

Memory

error

data

••••

Exchange

registers

Exchange

Address

register

Mode

register

••••••

Flag

register

••••••

Cluster

Number

register

Program

State

register

A

registers

••

• • •

S

registers

•••••

..

..

·...

· .

· ......

· ..

· .

· .

Program

Address

register

•

Memory

field

registers

·.. ....

Active

Exchange Package • • • •

Exchange

sequence

• • • • • • •

Exchange

initiated

by

deadstart

sequence

•

Exchange

initiated

by

Interrupt

flag

set

•

Exchange

initiated

by

program

exit

• •

Exchange

sequence

issue

conditions

Exchange Package management • • · ..

. .

...

HR-0032

vi

A

2-14

2-15

2-16

2-16

2-17

2-18

2-19

2-20

2-20

2-21

2-21

2-24

2-24

2-24

2-25

2-25

3-1

3-1

3-1

3-2

3-2

3-2

3-3

3-3

3-5

3-5

3-7

3-7

3-8

3-8

3-9

3-9

3-9

3-11

3-12

3-12

3-12

3-12

3-13

3-13

3-13

3-13

3-14

3-14

3-14

3-15

3-15

3.

CPU

CONTROL

SECTION

(continued)

MEMORY

FIELD

PROTECTION

.....

Instruction

Base

Address

register

•

Instruction

Limit

Address

register

Data

Base

Address

register

Data

Limit

Address

register

•

Program

range

error

•

Operand

range

error

• •

PROGRAMMABLE

CLOCK

•

Instructions

Interrupt

Interval

register

•

Interrupt

Countdown

counter

•

Clear

programmable

clock

interrupt

request

PERFOBMANCE

MONITOR

DEADSTART

SEQUENCE

• • • • •

4.

CPU

COMPUTATION

SECTION

INTRODUCTION

•

OPERATING

REGISTERS

ADDRESS

REGISTERS

A

registers

B

registers

SCALAR

REGISTERS

S

registers

T

registers

•

VECTOR

REGISTERS

•

V

registers

V

register

reservations

and

chaining

•

Vector

control

registers

Vector

Length

register

•

Vector

Mask

register

•

FUNCTIONAL

UNITS

• • • • • •

HR-0032

Address

functional

units

Address

Add

functional

unit

Address

Multiply

functional

unit

• •

Scalar

functional

units

•

Scalar

Add

functional

unit

•

Scalar

Shift

functional

unit

Scalar

Logical

functional

unit

•

Scalar

Population/Parity/Leading

Zero

functional

unit

Vector

functional

units

•

Vector

functional

unit

reservation

•

Vector

Add

functional

unit

•

Vector

Shift

functional

unit

•

Full

Vector

Logical

functional

unit

Second

Vector

Logical

functional

unit

Vector

Population/parity

functional

unit

vii

3-16

3-17

3-17

..

3-18

3-18

3-18

3-19

3-19

3-19

3-19

3-20

3-20

3-20

3-21

4-1

4-1

4-3

4-3

4-3

4-5

4-6

4-6

4-8

4-9

4-9

4-12

4-13

4-13

4-13

4-14

4-14

4-15

4-15

4-15

4-15

4-16

4-16

4-16

4-16

4-17

4-17

4-17

4-18

4-18

4-19

A

5.

FONC'lIONAL

UNITS

(continued)

·..

Floating-point

functional

units

• • • •

Floating-point

Add

functional

unit

••

• • • • •

Floating-point

Multiply

functional

unit

Reciprocal

Approximation

functional

unit

• ·..

ARITHMETIC

OPERATIONS

• • • • • • • • • • • • • • • • • ..

..

Integer

arithmetic

•••••••••••

. ..

Floating-point

arithmetic

• • • • • • • • • • •

Normalized

floating-point

numbers

•••••

Floating-point

range

errors

• • •

Floating-point

Add

functional

unit

• • • • •

Floating-point

Multiply

functional

unit

• • •

Floating-point

Reciprocal

Approximation

functional

unit

• • • • • • • • • • •

Double-precision

numbers • • • • • • • • • •

Addition

algorithm

• • • • • • • • • • • • •

Multiplication

algorithm

• • • •

Division

algorithm

• • •

Newton's

method

•••

..... ...

Derivation

of

the

division

algorithm

• • ·.

LOGICAL

OPERATIONS

• • • • • • • • •

CPU

INSTRUCTIONS

••

.... .. .. · ..

INSTRUCTION

FORMAT

• .. · .

I-parcel

instruction

format

with

discrete

j

and k

fields

••

• • • • • • • • • • • • • • • •

I-parcel

instruction

format

with

combined j

and k

fields

•••

• • • • • • • • • • •

2-parcel

instruction

format

with

combined

j,

k,

and m

fields

• • • • • • • • • • • • • • • • •

2-parcel

instruction

format

with

combined

i,

j,

k,

and m

fields

• • • • • • • • •

SPECIAL

REGISTER

VALUES

• • • •

INSTRUCTION

ISSUE

• • •

INSTRUCTION

DESCRIPTIONS

• •

APPENDIX

SECTION

4-20

4-20

4-20

4-21

4-21

4-21

4-22

4-23

4-24

4-24

4-25

4-27

4-27

4-27

4-28

4-30

4-30

4-31

4-35

5-1

5-1

5-1

5-2

5-2

5-3

5-4

5-5

5-6

A.

INSTRUCTION

SUMMARY

FOR

CRAY

X-MP

MODELS

22

AND

24 • • • • • • •

A-I

B. 6

MBYTE

PER

SEOOND

CHANNEL

DESCRIPTIONS

... . . .

INTRODUCTION

• • • • • • • • • • .. ...

6

MBYTE

PER

SEOOND

INPUT

CHANNEL

SIGNAL

SEQUENCE.

Data

bits

20

through

2

15

• • • • • • • • • •

parity

bits

0

through

3 • • • • • • • • • • •

HR-0032

viii

...

.... . .

B-1

B-1

8-1

B-1

B-2

A

C.

D.

6

MBYTE

PER

SEOOND

INPUT

CHANNEL

SIGNAL

SEQUENCE

(continued)

Ready

signal

• • • • • • • • • • • • • • •

Resume

signal

• • • • • • • • • • • • • • • •

Disconnect

signal

• • • • • • • • • •

6

MBYTE

PER

SECOND

OUTPUT

CHANNEL

SIGNAL

SEQUENCE

Data

bits

20

through

2

15

••

• • • • • • • •

Parity

bits

0

through

3 •

Ready

signal

• • • •

Resume

signal

• • • • •

Disconnect

signal

• • • • .. .

. ...

PERFORMANCE

MONITOR

. . . . . .. . . .. . . ... . .. . . .

INTRODUCTION

• • • • • • • • •

SELECTING

PERFORMANCE

EVENTS

READING

PERFORMANCE

RESULTS

TESTING

PERFORMANCE

COUNTERS •

.... . .. . . . .

. .. .. . . .. . . . .

SECDED

MAINTENANCE

FUNCTIONS

. . . . . .. ... . . . . . . . .

INTRODUCTION

• • • • • • • • • • • • •

VERIFICATION

OF

CHECK

BIT

STORAGE

VERIFICATION

OF

CHECK

BIT

GENERATION

•

VERIFICATION

OF

ERROR

DETECTION

AND

CORRECTION

•

CLEARING

MAINTENANCE

MODE

FUNCTIONS

••••••

.. .

FIGURES

1-1

CRAY

X-MP

Model 22

or

24

l2-column

mainframe

with

a

1-2

1-3

1-4

1-5

1-6

1-7

1-8

1-9

1-10

1-11

1-12

1-13

2-1

2-2

2-3

2-4

Cray

I/O

Subsystem

and

an

SSD

••••••

• • • • • • • •

Basic

organization

of

the

dual-processor

system

Control

and

data

paths

for

a

single

CPU

CRAY

X-MP

Models 22

or

24

6-column

mainframe

chassis

• • • • •

TYPical

interface

cabinet

• • • •

I/O

Subsystem

chassis

•••

• • • • ...

DD-29

Disk

Storage

Unit

• • • • • • •

Solid-state

Storage

Device

chassis

• • • • • • • • • • • • • •

Condensing

unit

••••••••••

• • •

Power

distribution

units

• • • • • • • • •

Motor-generator

equipment

• • •

Block

diagram

of

CRAY

X-MP

dual-processor

system

with

full

disk

capacity

•••••••••

• • • • • • • • • •

Block

diagram

of

CRAY

X~

dual-processor

system

with

block

multiplexer

channels

•••••

• • • • • • •

Central

Memory

organization

for

a

dual-processor

system

6-column

memory

address

(32

banks)

• •

6-column

memory

address

(16

banks)

• • • •

12-co1umn memory

address

(32

banks)

•••

HR-0032

ix

B-3

B-3

B-3

B-3

B-4

B-5

B-5

B-5

B-5

C-l

C-1

C-l

C-3

C-3

D-l

D-l

D-1

D-2

D-2

D-3

1-2

1-5

1-6

1-7

1-8

1-10

1-11

1-12

1-13

1-14

1-15

1-16

1-17

2-2

2-3

2-3

2-4

A

FIGURES

(continued)

2-5

2-6

2-7

2-8

2-9

2-10

2-11

3-1

3-2

3-3

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

4-10

5-1

5-2

5-3

5-4

5-5

5-6

5-7

5-8

5-9

5-10

5-11

5-12

l2-column

memory

address

(16

banks)

• • • • • • • • • • •

Memory

data

path

with

SECDED

• • • • • • • • •

Error

correction

matrix

• • • • • • • • •

Shared

registers

and

real-time

clock

• • • • • • • • •

Basic

I/O

program

flowchart

•••••••••

• •

Channel

I/O

control

(shown

for

one

processor)

Input/output

data

paths

••••••••

Instruction

issue

and

control

elements

• • • • • • • • • • • •

Instruction

buffers

•••••••••••••

Exchange

package

for

a

dual-processor

system

•

Address

registers

and

functional

units

•

Scalar

registers

and

functional

units

••••

vector

registers

and

functional

units

••••

Integer

data

formats

• • • • •

".

• • • •

. ..

Floating-point

data

format

• • • • • • • • • • • • • • • •

Exponent

matrix

for

Floating-point

Multiply

unit

• • • • •

Integer

multiply

in

Floating-point

Multiply

functional

unit

••••

• • • • • • • • • • • •

49-bit

floating-point

addition

• • • • • • • • • •

Floating-point

multiply

partial-product

sums

pyramid

• •

Newton's

method

•••••••••••••••••••••••

General

form

for

instructions

•••••••••••

I-parcel

instruction

format

with

discrete

j and k

fields

•

I-parcel

instruction

format

with

combined j and

k

fields

• • • • • • • • • • • • • • • • • • • • • • • • • • •

2-parcel

instruction

format

with

combined

j,

k, and

m

fields

• • • • • • • • • • • • • • • • • • • • • • • • •

2-parcel

instruction

format

for

a

branch

with

combined

i,

j,

k,

and m

fields

•••••••••

2-parcel

instruction

format

for

a

24-bit

immediate

constant

with

combined

i,

j,

k,

and

m

fields

•••••••••••

vector

left

double

shift,

first

element,

VL

greater

than

1 • •

vector

left

double

shift,

second

element,

VL

greater

than

2

vector

left

double

shift,

last

element

• • • • • • • •

vector

right

double

shift,

first

element

•

vector

right

double

shift,

second

element,

VL

greater

than

1

••••••

• • • • • •

vector

right

double

shift,

last

operation

••••

• • • • • •

TABLES

1-1

2-1

2-2

3-1

CRAY

x~p

dual-processor

system

characteristics

Access

conflicts

to

shared

registers

in

a

dual-processor

computer

• • • •

Channel

word

assembly/disassembly

Exchange

Package

assignments

• • • •

HR-0032 x A

2-4

2-8

2-9

2-11

2-19

2-22

2-23

3-1

3-3

3-6

4-4

4-7

4-10

4-22

4-23

4-25

4-27

4-28

4-29

4-31

5-1

5-2

5-2

5-3

5-4

5-4

5-71

5-71

5-71

5-72

5-73

5-73

1-3

2-13

2-18

3-7

TABLES

(continued)

B-1

B-2

C-l

INDEX

Input

channel

signal

exchange

• • • • • • • • • • •

Output

channel

signal

exchange

• • • • • • • • • • • • • •

Performance

counter

group

descriptions

• • • • • •

HR-0032

xi

A

B-2

B-4

C-2

SYSTEM

DESCRIPTION

INTRODUCTION

The

CRAY

X-MP/22

and

CRAY

X-MP/24

are

powerful,

general

purpose

computer

systems

that

contain

two

central

processing

units

(CPUs). The

systems

can

achieve

extremely

high

multiprocessing

rates

by

efficiently

using

the

scalar

and

vector

processing

capabilities

of

both

CPUs

combined

with

the

systems'

random-access,

solid-state

memory

(RAM)

and

shared

registers.

Vector

processing

is

the

performance

of

iterative

operations

on

sets

of

ordered

data.

When

two

or

more

vector

operations

are

chained

together,

two

or

more

operations

can

be

executing

each

9.5-nanosecond

clock

period,

greatly

exceeding

the

computational

rates

of

conventional

scalar

processing.

Scalar

operations

complement

the

vector

capability

by

providing

solutions

to

problems

not

readily

adaptable

to

vector

techniques.

Equipment

options

allow

the

systems

to

be

configured

for

a

particular

use

(see

table

1-1).

Central

Memory

of

a

dual-processor

system

can

be

either

2

million

(model 22)

or

4

million

(model 24)

64-bit

words.

The

systems

are

compatible

with

all

existing

models

of

the

Cray

I/O

Subsystem,

which

matches

the

mainframe's

processing

rates

with

high

input/output

transfer

rates

for

communication

with

mass

storage

units,

other

peripheral

devices,

and

a

wide

variety

of

host

computers.

In

addition

to

the

mainframe

and

I/O

Subsystem,

a

Cray

Research,

Inc.,

Solid-state

Storage

Device

can

be

configured

with

the

system.

An

SSD

provides

significantly

improved

throughput

of

programs

that

access

large

data

files

repetitively.

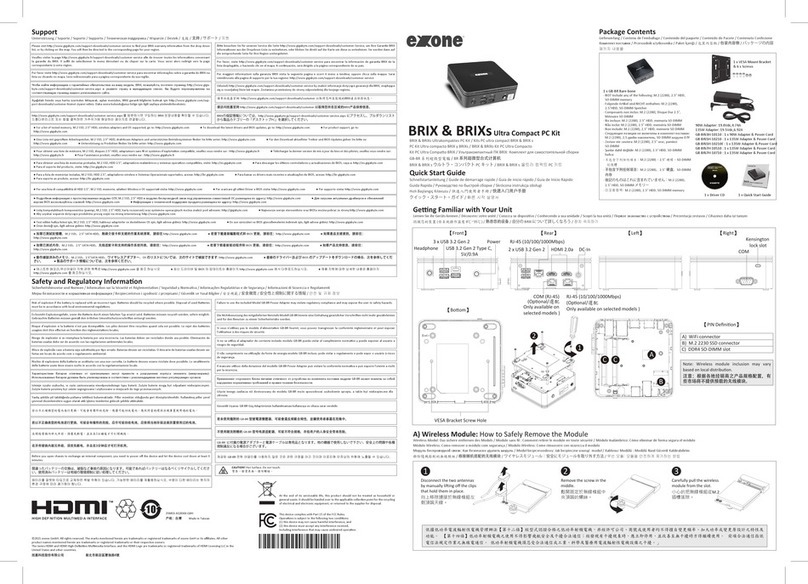

Figure

1-1

illustrates

the

mainframe

configured

with

a

Cray

I/O

Subsystem

and

an

SSD®.

This

section

describes

system

components

and

configurations.

Table

1-1

provides

overall

system

characteristics.

HR-0032

1-1

A

1

HR-0032

Figure

1-1.

CRAY

X-MP

Model 22

or

24

12-column

mainframe

with

a

Cray

I/O

Subsystem

and

an

SSD

1-2

A

I

I

I

I

Table

1-1.

CRAY

X~

dual-processor

system

characteristics

Configuration

-Mainframe

with

2

Central

Processing

Units

(CPUs)

-

I/O

Subsystem

with

2,

3,

or

4

I/O

Processors

CPU

speed

-

Optional

Solid-state

Storage

Device

(SSD)

-

9.5

ns

CPU

clock

period

-

105

million

floating-point

additions

per

second

per

CPU

-

105

million

floating-point

multiplications

per

second

per

CPU

-

105

million

half-precision

floating-point

divisions

per

second

per

CPU

-33

million

full-precision

floating-point

divisions

per

second

per

CPU

-

Simultaneous

floating-point

addition,

multiplication,

and

reciprocal

approximation

within

each

CPU

Memories -Mainframe

has

2

million

(model 22)

or

4

million

(model 24)

64-bit

words

in

Central

Memory

Input/Output

-One 1250 Mbyte

per

second

Solid-state

Storage

Device

(SSD)

channel

pair

-

Two

100 Mbyte

per

second

channel

pairs

for

interface

to

I/O

Subsystem

-

Four

6 Mbyte

per

second

channel

pairs

Physical

-

64

sq

ft

floor

space

for

l2-column

mainframe;

32

sq

ft

floor

space

for

6-column

mainframe.

-

15

sq

ft

floor

space

for

I/O

Subsystem

-

15

sq

ft

floor

space

for

SSD

-

5.25

tons,

l2-column

mainframe

weight;

2.95

tons,

6-column

mainframe

weight.

-

1.5

tons,

I/O

Subsystem

weight

-

1.5

tons,

SSD

weight

-

Liquid

refrigeration

of

each

chassis

-400

Hz

power from

motor-generators

HR-0032

1-3

A

CONVENTIONS

The

following

conventions

are

used

in

this

manual.

ITALICS

Italicized

lowercase

letters,

such

as

jk,

indicate

variable

information.

REGISTER

CONVENTIONS

Parenthesized

register

names

are

used

frequently

in

this

manual

as

a form

of

shorthand

notation

for

the

expression

"the

contents

of

register

___

.ft

For

example,

"Branch

to

(P)"

means

"Branch

to

the

address

indicated

by

the

contents

of

register

P."

Designations

for

the

A, B,

S,

T,

and

V

registers

are

used

extensively.

For

example,

"Transmit

(Tjk)

to

sin

means

"Transmit

the

contents

of

the

T

register

specified

by

the

jk

designators

to

the

S

register

specified

by

the

i

designator."

Register

bits

are

numbered

right

to

left

as

powers

of

2,

starting

with

2°.

Bit

263

of

an

S,

VL

or

T

register

value

represents

the

most

significant

bit.

Bit

2~3

of

an

A

or

B

register

value

represents

the

most

significant

bit.

(A

and

B

registers

are

24

bits.)

The

numbering

conventions

for

the

Exchange

Package

and

the

Vector

Mask

register

are

exceptions.

Bits

in

the

Exchange

Package

are

numbered

from

left

to

right

and

are

not

numbered

as

powers

of

2

but

as

bits

°

through

63

with

°

as

the

most

significant

and

63

as

the

least

significant.

The

Vector

Mask

register

has

64

bits,

each

corresponding

to

a word

element

in

a

vector

register.

Bit

2

63

corresponds

to

element

0,

bit

2°

corresponds

to

element

63.

NUMBER

CONVENTIONS

Unless

otherwise

indicated,

numbers

in

this

manual

are

decimal

numbers.

Octal

numbers

are

indicated

with

an

8

subscript.

Exceptions

are

register

numbers,

channel

numbers,

instruction

parcels

in

instruction

buffers,

and

instruction

forms

which

are

given

in

octal

without

the

subscript.

CLOCK

PERIOD

The

basic

unit

of

CPU

computation

time

is

9.5

nanoseconds

(ns)

and

is

referred

to

as

a

clock

period

(CP).

Instruction

issue,

memory

references,

and

other

timing

considerations

are

often

measured

in

CPs.

HR-0032

1-4

A

I

SYSTEM CDIPONEN'l'S

The

system

is

composed

of

a mainframe and an

I/O

Subsystem.

Mass

storage

devices,

front-end

interfaces,

and

optional

tape

devices

are

also

integral

parts

of

a

system.

Optionally,

a Cray

Solid-state

Storage

Device

(SSD)

can

be

part

of

the

system.

Supporting

this

equipment

are

condensing

units

for

refrigeration,

motor-generators

to

provide

system

power, and power

distribution

units

for

the

mainframe,

I/O

Subsystem,

and

the

SSD.

System

components

are

described

on

the

following

pages.

CENTRAL PROCESSING UNITS

Each

CPU

has

independent

control

and

computation

sections.

Both

CPOs

share

Central

Memory

and

the

inter-CPO communication and

I/O

sections.

(CPO

sections

are

described

in

later

sections.)

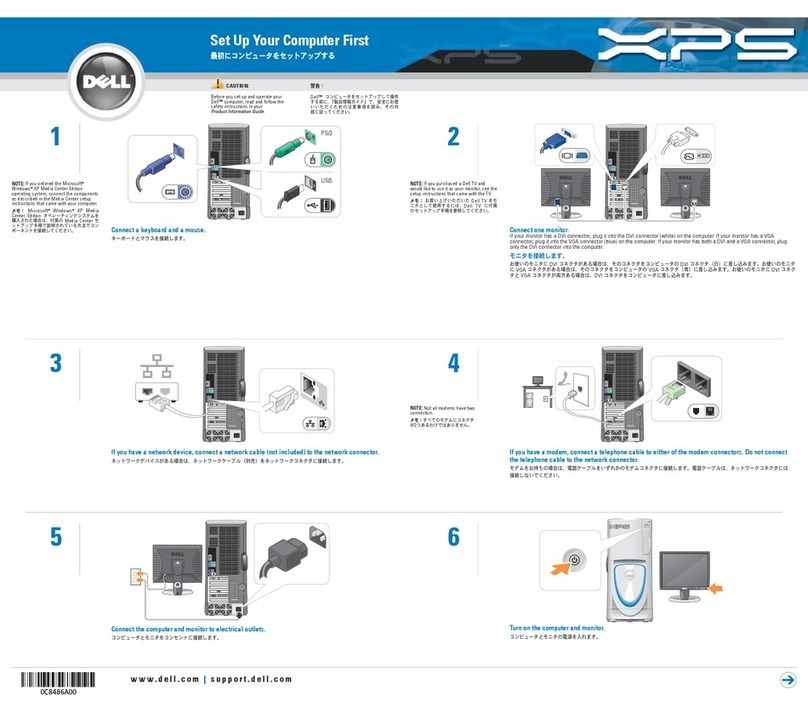

Figure

1-2

illustrates

the

basic

organization

of

the

computer,

figure

1-3

illustrates

the

components and

control

and

data

paths

of

a

single

CPU

in

the

system.

Figure

1-4

shows mainframe

chassis.

CONTROL

SECTION

•

Instruction

-•

buffers

•

•

Control

registers

• Exchange

mechanism

•

Interrupt

• Programmable

clock

•

Status

register

HR-0032

COMPUTATION

CPU

COMMUNICATION

COMPUTATION

SECTION

SECTION SECTION

Registers

•

Shared

registers

-•

Registers

Functional

• Semaphore •

Functional

units

registers

units

•

Real-time

Clock

register

MEMORY

SECTION

2

million

or

4

million

64-bit

words

,

I/O

SECTION

•

Four

6 Mbyte

per

second

channel

pairs

• One 1250 Mbyte

per

second

channel

pair

•

Two

100 Mbyte

per

second

channel

pairs

Figure

1-2.

Basic

organization

of

the

dual-processor

system

1-5

CONTROL

SECTION

•

Instruction

buffers

•

Control

registers

•

Exchange

mechanism

•

Interrupt

•

Programmable

clock

•

Status

register

A

77

Si

t

jSj

Si t

lSi

Si

t

lSi

Ait

IAi

Ai

AI:

Figure

1-3.

liD

Ak

\....-,ij----.:..;.:.....----I-4--+-~_..j

Functional

c::..(.;'ooo----

___

A-'-i

____

--

......

----1

Units

-I

ReaI-Ti.eClod

SM

0--

I

ST

0'-

I

S8

lOa

I"

Sjl

Sil

s;!

Ail

tSi

t

Si

tSi

tAi

*The

Vector

Pop/Parity

shares

its

input

path with

the

Reciprocal

Approximation

unit.

The

Second Vector

logical

s"ares

its

input

and

output

path

with

the

Floating-point

Multiply

unit.

Issue

Control

and

data

paths

for

a

single

CPU

t

Second

Vector

Logical

unit

not

available

on

all

machines.

HR-0032

1-6

A

Figure

1-4.

CRAY

X~P

Model

22

or

24 6-column

mainframe

chassis

INTERFACES

The

Cray

mainframe

is

designed

for

use

with

front-end

computers

in

a

computer

network.

A

front-end

computer

system

is

self

contained

and

executes

under

the

control

of

its

own

operating

system.

Standard

interfaces

connect

the

Cray

mainframe's

I/O

channels

to

channels

of

front-end

computers,

providing

input

data

to

the

Cray

and

receiving

output

from

it

for

distribution

to

peripheral

equipment.

Interfaces

compensate

for

differences

tn

channel

widths,

machine

word

size,

electrical

logic

levels,

and

control

signals.

The

Master

I/O

Processor

of

the

I/O

Subsystem

communicates

with

a

front-end

computer

system

through

a 6 Mbyte

per

second

channel

pair

to

a

channel

adapter

module

in

the

Cray

mainframe.

Communication

continues

through

a

front-end

interface,

to

the

front-end

computer

typically

through

a

front-end

computer

I/O

channel.

HR-0032

1-7

A

The

front-end

interface

is

housed

in

a

stand-alone

cabinet

(figure

1-5)

located

near

the

host

computer.

Its

operation

is

invisible

to

both

the

front-end

computer

user

and

the

Cray

user.

A

primary

goal

of

the

interface

is

to

maximize

the

use

of

the

front-end

channel

connected

to

the

Cray

system.

Since

the

MIOP

channel

connected

to

the

interface

is

faster

than

any

front-end

channel

connected

to

the

interface,

the

burst

rate

of

the

interface

is

limited

by

the

maximum

rate

of

the

front-end

channel.

Interfaces

to

front-end

computers

allow

the

front-end

computers

to

service

the

Cray

mainframe

in

the

following

ways:

•

As

a

master

operator

station

•

As

a

local

operator

station

•

As

a

local

batch

entry

station

•

As

a

data

concentrator

for

multiplexing

several

other

stations

into

a

Single

Cray

channel

•

As

a

remote

batch

entry

station

•

As

an

interactive

communication

station

Peripheral

equipment

attached

to

the

front-end

computer

varies

depending

on

the

use

of

the

Cray

system.

Figure

1-5.

Typical

interface

cabinet

HR-0032

1-8

A

This manual suits for next models

2

Table of contents

Other Cray Desktop manuals