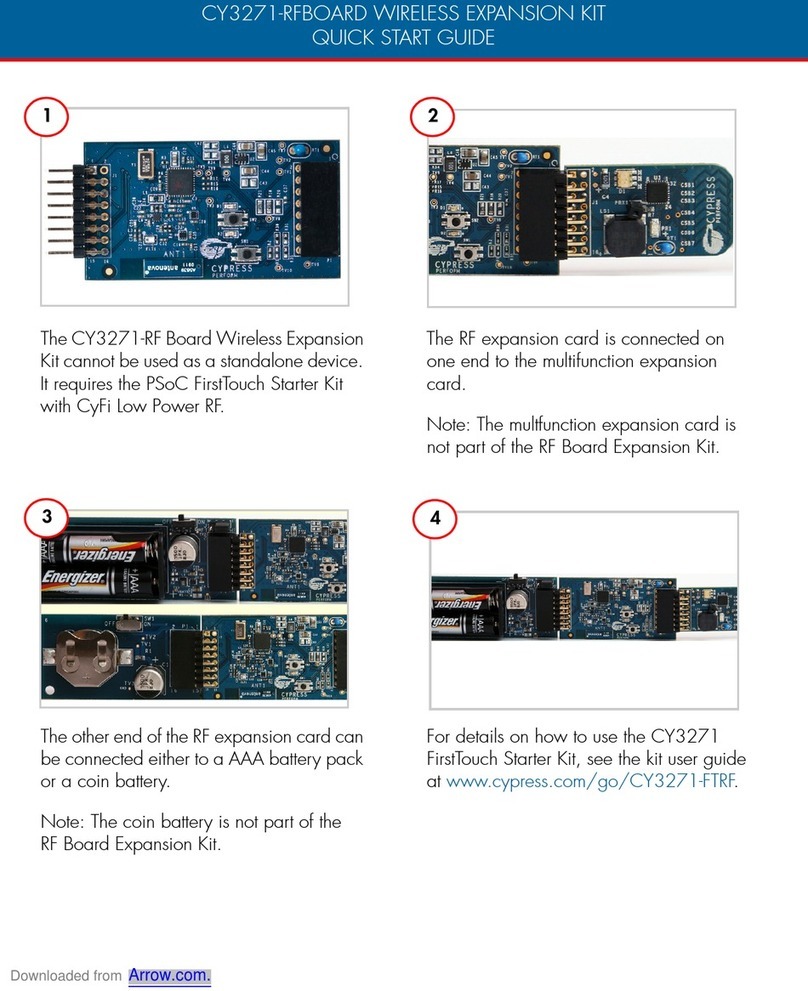

PRELIMINARY

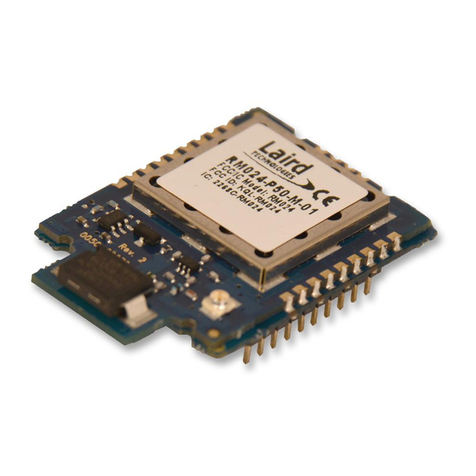

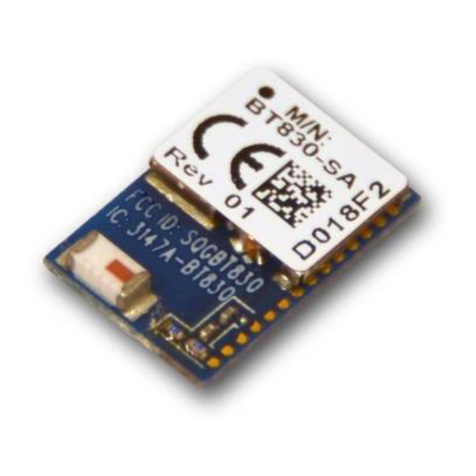

CYBLE-212006-01

CYBLE-202007-01

CYBLE-202013-11

EZ-BLE™ PRoC™ XR Module

Cypress Semiconductor Corporation • 198 Champion Court • San Jose,CA 95134-1709 • 408-943-2600

Document Number: 002-15631 Rev.*B Revised December 16, 2016

General Description

The CYBLE-2X20XX-X1 is a BluetoothLow Energy (BLE)

wireless module solution. The CYBLE-2X20XX-X1 is a turnkey

solution and includes onboard crystal oscillators, passive

components, and the Cypress PRoC™ BLE. Refer to the

CYBL1XX7X datasheet for additional details on the capabilities

of the PRoC BLE device used on this module.

The CYBLE-2X20XX-X1 supports a number of peripheral

functions (ADC, timers, counters, PWM) and serial

communication protocols (I2C, UART, SPI) through its

programmable architecture. The CYBLE-2X20XX-X1 includes a

royalty-free BLE stack compatible with Bluetooth 4.2 and

provides up to 19 GPIOs in a 15.0 × 23.0 × 2.0 mm package.

The CYBLE-2X20XX-X1 is offered in two fully certified versions

(CYBLE-212006-01 and CYBLE-202007-01), as well as an

uncertified version (CYBLE-202013-11). The CYBLE-212006-01

includes an integrated trace antenna. The CYBLE-202007-01

supports an external antenna via a u-FL connector. The

CYBLE-202013-11 supports an external antenna through a RF

solder pad output. The CYBLE-202013-11 does not include a RF

shield and is not Bluetooth SIG or regulatory certified.

Module Description

■Module size: 15.00 mm × 23.00 mm × 2.00 mm

■Extended Range:

❐Up to 400 meters bidirectional communication[1,2]

❐Up to 450 meters in beacon only mode[1]

■Bluetooth 4.2 qualified single-mode module

❐QDID: 88957

❐Declaration ID: D032786

■Footprint compatible options for integrated antenna or

antenna-less design options

■Certified to FCC, IC, MIC, KC, and CE regulations

(CYBLE-212006-01 and CYBLE-202007-01 only)

■Castelated solder pad connections for ease-of-use

■256-KB flash memory, 32-KB SRAM memory

■Up to 19 GPIOs

■Industrial temperature range: –40 °C to +85 °C

■32-bit processor (0.9 DMIPS/MHz) operating up to 48 MHz

■Watchdog timer with dedicated internal low-speed oscillator

Power Consumption

■Maximum TX output power: +7.5 dbm

■RX Receive Sensitivity: –93 dbm

■Received signal strength indicator (RSSI) with 1-dB resolution

■TX current consumption

❐BLE silicon: 15.6 mA (radio only, 0 dbm)

❐RFX2401C: 27 mA (PA/LNA only, +7.5 dBm)

■RX current consumption

❐BLE silicon: 16.4 mA (radio only, 0 dbm)

❐RFX2401C: 8.0 mA (PA/LNA only)

■Cypress CYBL1XX7X silicon low power mode support

❐Deep Sleep: 1.3 A with watch crystal oscillator (WCO) on

❐Hibernate: 150 nA with SRAM retention

❐Stop: 60 nA with XRES wakeup

Functional Capabilities

■Up to 18 capacitive sensors for buttons or sliders

■12-bit, 1-Msps SAR ADC with internal reference,

sample-and-hold (S/H), and channel sequencer

■Two serial communication blocks (SCBs) supporting I2C

(master/slave), SPI (master/slave), or UART

■Four dedicated 16-bit timer, counter, or PWM blocks

(TCPWMs)

■LCD drive supported on all GPIOs (common or segment)

■Programmable low voltage detect (LVD) from 1.8 V to 4.5 V

■I2S master interface

■BLE protocol stack supporting generic access profile (GAP)

Central, Peripheral, Observer, or Broadcaster roles

■Switches between Central and Peripheral roles on-the-go

■Standard BLE profiles and services for interoperability

■Custom profile and service for specific use cases

Benefits

CYBLE-2X20XX-X1 is provided as a turnkey solution, including

all necessary hardware required to use BLE communication

standards.

■Proven hardware design ready to use

■Cost optimized for applications without space constraint

■Reprogrammable architecture

■Fully certified module eliminates the time needed for design,

development and certification

■Bluetooth SIG qualified with QDID and Declaration ID

■Flexible communication protocol support

■PSoC Creator™ provides an easy-to-use integrated design

environment (IDE) to configure, develop, program, and test a

BLE application

Notes

1. Connection range tested module-to-module in full line-of-sight environment, free of obstacles or interference sources with output power of +7.5 dBm.

2. Specified as EZ-BLE XR module to module range. Mobile phone connection range will decrease based on the PA/LNA performance of the mobile phone used.