Sidekiq™ Mini PCIe | Hardware User Manual Hardware Interfaces

Epiq Solutions Proprietary Page 19

maximum of 3.3V can be safely applied to this input port. This 1PPS input is optional. Note: Since

this signal is routed directly into the on-board FPGA, it is possible to also use this signal as a general

purpose input. Contact Epiq Solutions for details of alternate usage of this port.

The External Reference Clock Input interface is a W.FL jack connector that allows an external 40

MHz reference clock to be brought in to Sidekiq and utilized instead of the default on-board 40 MHz

TCVCXO. This provides the facility to have multiple Sidekiq cards share a common external 40 MHz

reference clock. Note: On RevB Sidekiq cards, a hardware modification (resistor swap) is required to

disable the on-board 40 MHz TCVCXO, and to accept the external 40 MHz reference clock input.

Contact Epiq Solutions for details. RevC Sidekiq and beyond provide a means to switch between the

on-board reference clock and external reference clock through the libsidekiq software API.

The electrical specification for this input signal is defined below.

Input Level 0.8 – 1.3 Vpp, 0 dBm max from 50 ohm source

Input Impedance AC-Coupled high impedance

Frequency 40 MHz

Waveform Square or Sinewave

Connector Type W.FL

Table 6: Electrical specification for external reference clock input

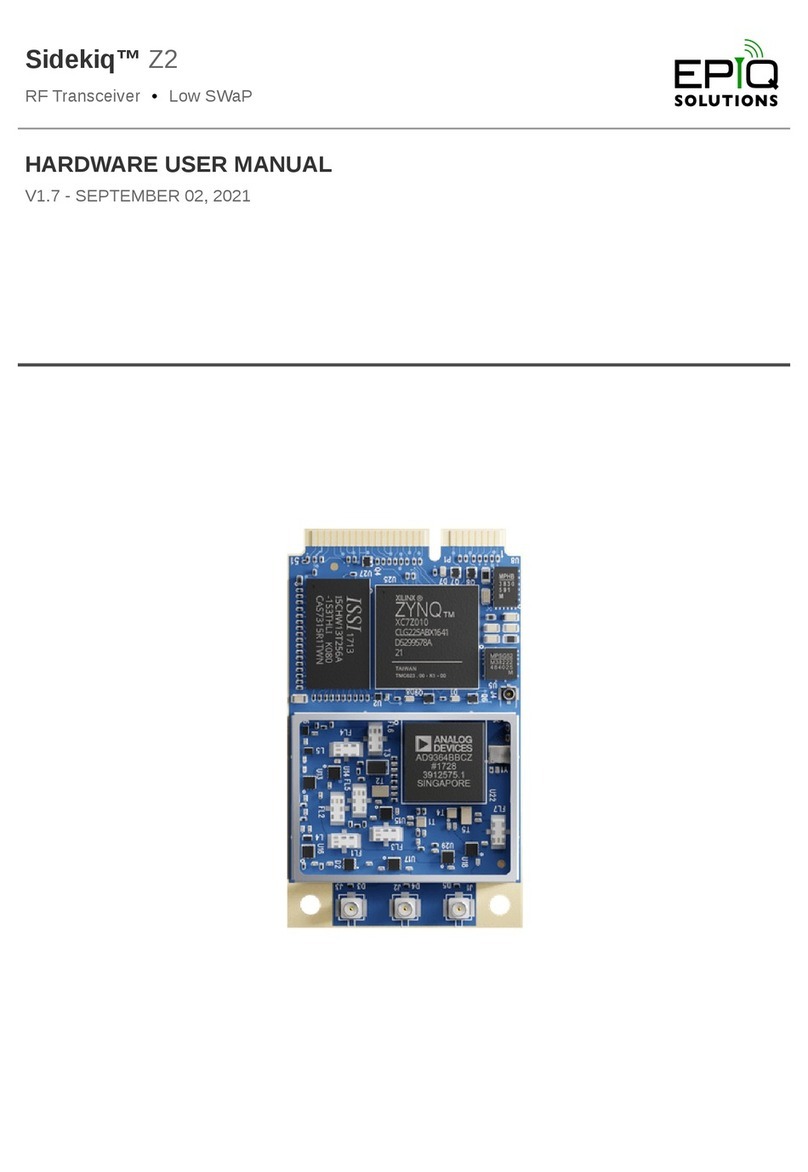

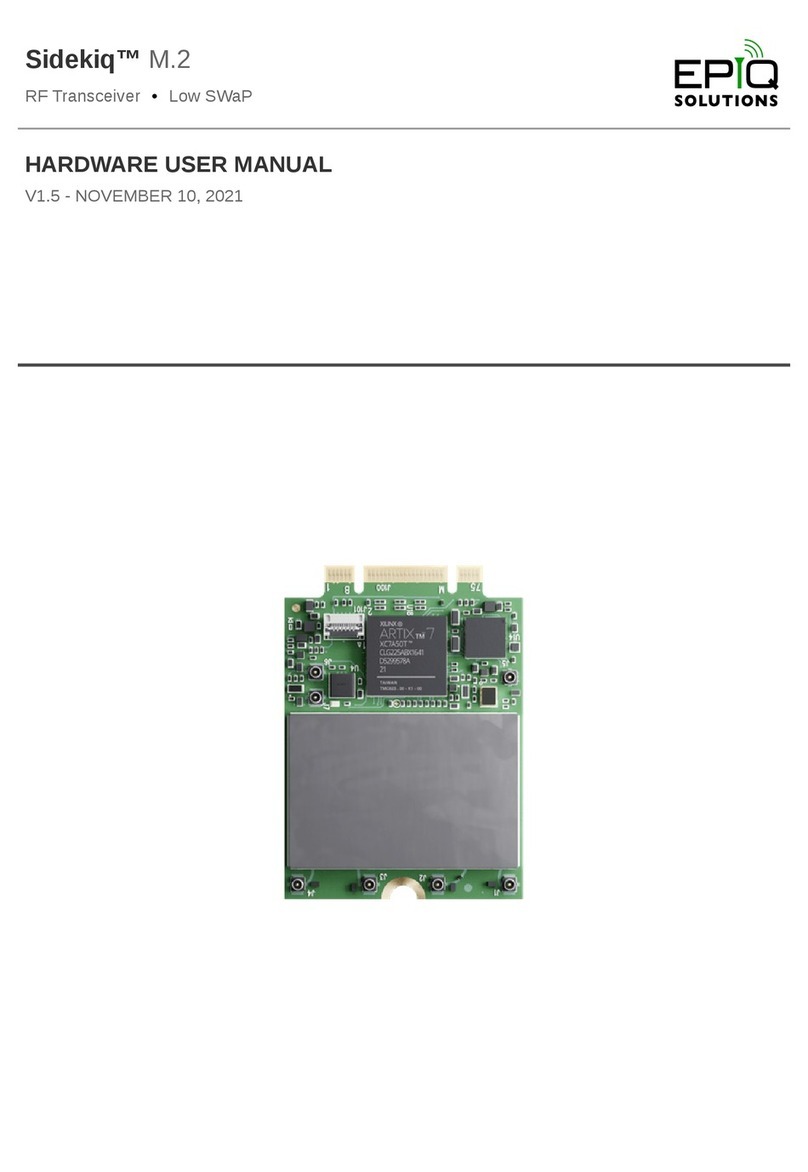

The RF shield (used to minimize the effects of RF noise entering the RF front end) serves as the

primary thermal relief path for heat dissipation in the system. Underneath the shield, thermal gap

pad material is used to transfer heat from components to the shield itself, yielding a minimal thermal

resistance. If no air flow is available in the host system where Sidekiq is being integrated, it is highly

recommended that the user provide a thermal dissipation path from this shield to a thermally

conductive surface in the host system, such as a metal back plate or other metal housing. The use

of thermal gap pad material [8] can provide a flexible yet efficient thermal path between the RF

shield and the host system.

In addition to the RF shield, the other primary component generating heat in Sidekiq is the Xilinx

Spartan 6 FPGA (which is located right next to the RF shield). If an end user is developing a thermal

dissipation path for the RF shield, it is also recommended to include the FPGA in the thermal

EXTERNAL REFERENCE CLOCK INPUT

PRIMARY THERMAL RELIEF (RF SHIELD)