Sidekiq™ X2 | Hardware User Manual Hardware Interfaces

Epiq Solutions Proprietary Page 20

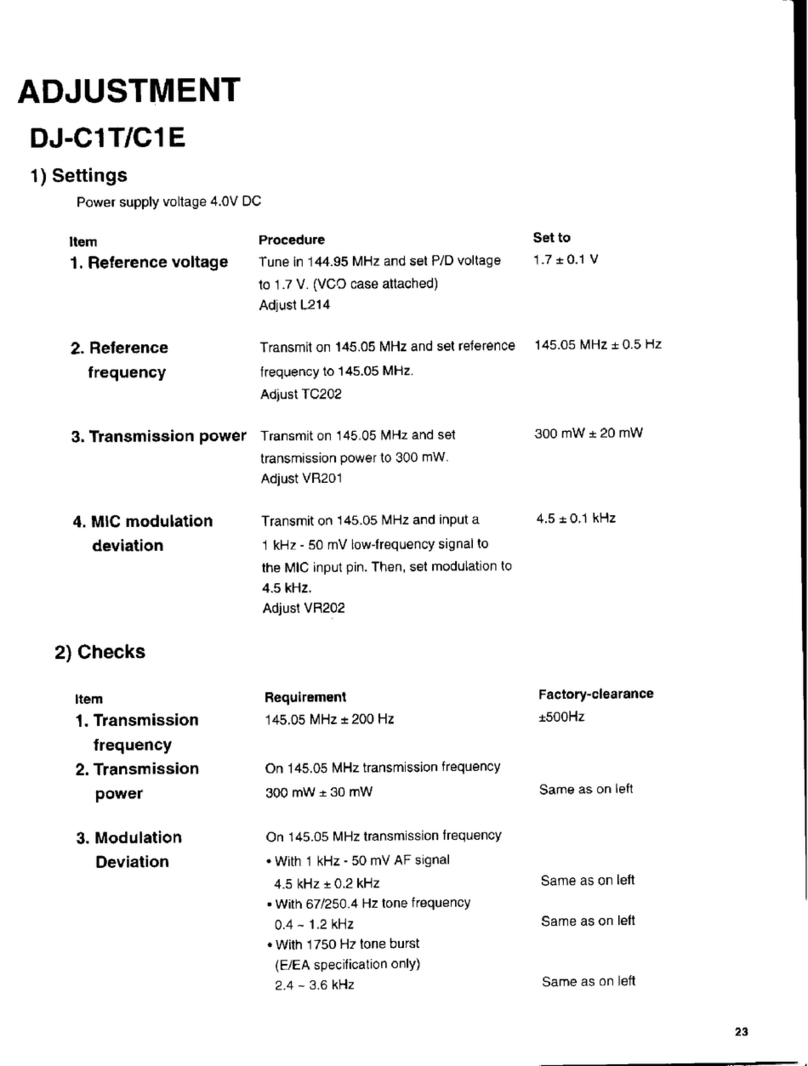

reference clock on board that is used for phase locking the system. In order to use an external 10

MHz reference input, the libsidekiq software API provides a function call to disable on the on-board

10 MHz reference and lock on to this external 10 MHz reference input.

The PPS Input port is an SSMC jack connector that accepts a pulse per second (PPS) input signal

for the purpose of providing a temporal frame of reference relative to this PPS edge. This PPS signal

is routed through a SN74LVC2G17YZPR buffer directly to the FMC electrical interface, and thus

routes directly into the FPGA on the host system. The PPS edge is expected to be a rising edge with

a fast slew rate, with a logic level high defined as any voltage between 0.85V and 5V, dependent on

Vadj (+1.8V / +2.5V). This PPS signal is used by the Sidekiq X2 FPGA reference design to latch the

digital timestamp of when the PPS edge occurs in the FPGA, and can then be queried by the

libsidekiq software API. It is also possible to coordinate other actions to take place based on the

occurrence of a PPS edge, such as starting Rx or Tx streaming.

Note: for conduction cooled applications, MMCX or SMP connectors are available. Contact Epiq

Solutions for details.

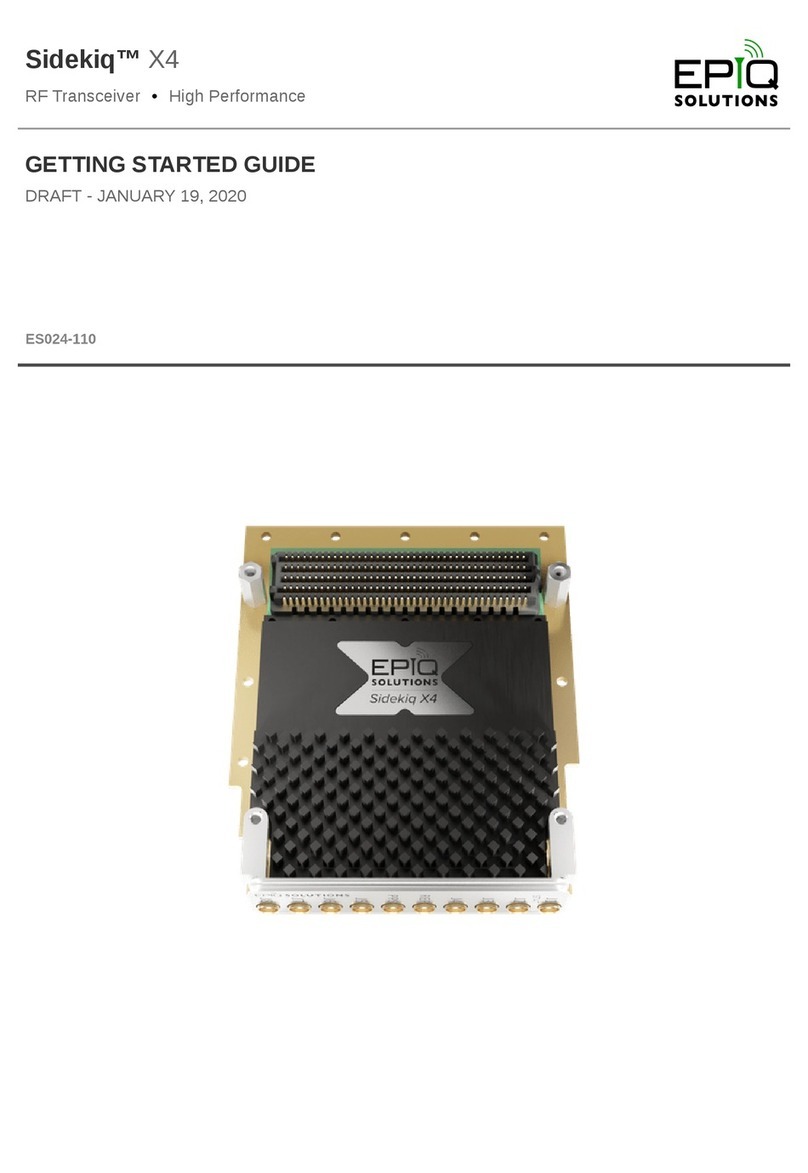

The RF shield/heatsink provides both RF isolation from spurious RF signals, while also providing a

thermal dissipation path for the card when used in convection cooled application. A minimum air flow

of TBD LFM is required to ensure that the heat generated by the card is adequately dissipated.

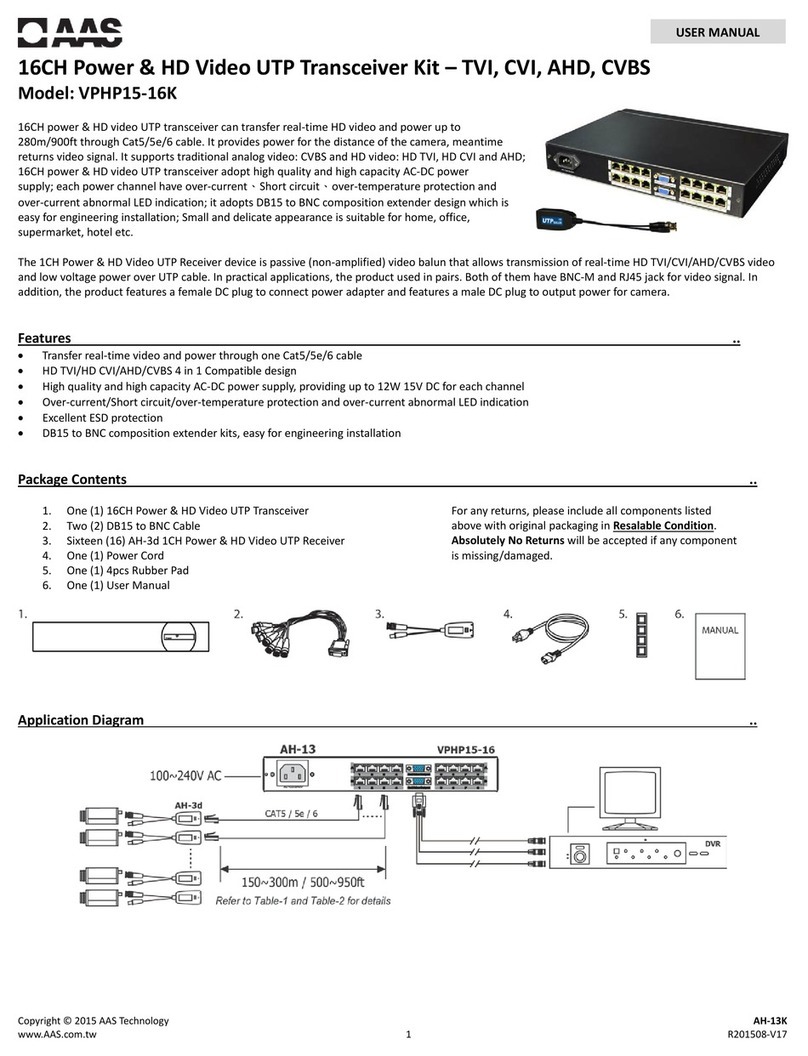

The VITA 57.1 HPC connector is the primary electrical interface for connecting Sidekiq X2 to a host

system. The complete pin mapping for signals accessible through this HPC interface on Sidekiq X2

is defined in the FMC High Pin Count (HPC) Section..

Note: It is assumed that the standard Sidekiq X2 FPGA reference design + libsidekiq software API

is being utilized by the host system. This reference design + software API provides all of the

infrastructure and control necessary to control the operation of the card, as well as stream data

between the card and the host system. The Sidekiq X2 FPGA reference design + libsidekiq software

API can be ported to alternate host platforms other than the PDK reference platform. Please contact

Epiq Solutions for details.

PPS INPUT

RF SHIELD + HEATSINK

VITA 57.1 HPC CONNECTOR