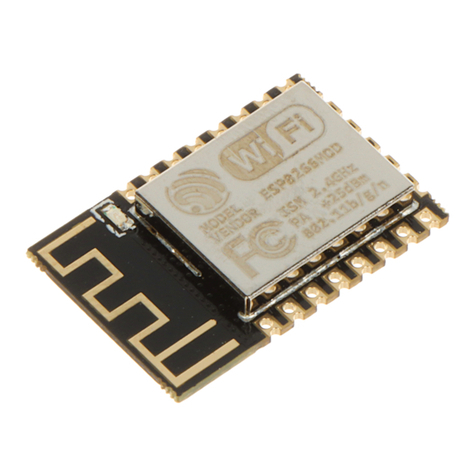

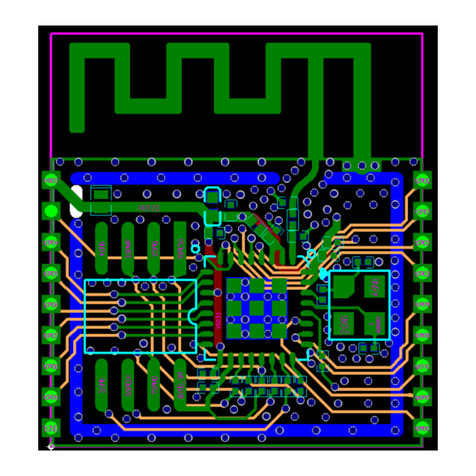

2. Schematic Checklist and PCB Layout Design

2.1.1.2 Analog Power Supply

Pin1, pin3, pin4, pin43 and pin46 are the analog power supply pins. It should be noted that the sudden increase

in current draw, when ESP32 is in transmission mode, may cause a power rail collapse. Therefore, it is highly

recommended to add another 10 µF capacitor to the power trace, which can work in conjunction with the 0.1 µF

capacitor. LC filter circuit needs to be added near the power pin so as to suppress high-frequency harmonics.

The inductor’s rated current is preferably 500 mA and above.

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

The capacitance of C1 and C2 varies

with the selection of the crystal.

SENSOR_VP

SENSOR_VN

GPIO32

GPIO33

CHIP_PU

GPIO35

SCK/CLK

SCS/CMD

SENSOR_VP

SHD/SD2 SWP/SD3

SDI/SD1

SDO/SD0

SENSOR_VN

GPIO34

GPIO26

GPIO27

GPIO14

GPIO12

GPIO2

GPIO15

GPIO0

GPIO18

GPIO2

U0TXD

U0RXD

GPIO22

GPIO21

GPIO4

GPIO19

SHD/SD2

SWP/SD3

SCS/CMD

SCK/CLK

SDO/SD0

SDI/SD1

GPIO23

CHIP_PU

GPIO34

GPIO35

GPIO25

GPIO26

GPIO27

GPIO14

GPIO12

GPIO13

GPIO0

GPIO15

GPIO4

GPIO16

GPIO5

GPIO17

GPIO32

GPIO33

GPIO21

U0TXD

U0RXD

GPIO25

GPIO13

GPIO16

SDI/SD1

SDO/SD0

SCK/CLK

SCS/CMD

SWP/SD3

SHD/SD2

GPIO5

GPIO18

GPIO23

GPIO17

GPIO19

GPIO22

GND

VDD33

GND

VDD33

GND

GND

GND

VDD33

GND

GND

VDD_SDIO GND

VDD_SDIO

GND

GND

GND

GNDGND

GND

VDD33

VDD33

GND

GNDGND

GND

GND

GND

GND GND

VDD33

GND

GND

Title

Size Document Number Re v

Date: Sheet o f

<Doc>

ESP-WROOM-32-5X5

A2

1 1Tuesday, July 03, 2018

Title

Size Document Number Re v

Date: Sheet o f

<Doc>

ESP-WROOM-32-5X5

A2

1 1Tuesday, July 03, 2018

Title

Size Document Number Re v

Date: Sheet o f

<Doc>

ESP-WROOM-32-5X5

A2

1 1Tuesday, July 03, 2018

L5 2.0nH

R1 20K(5%)

C13

10uF

U3 FLASH

/CS

1

DO 2

/WP 3

GND

4

DI 5

CLK

6

/HOLD

7

VCC 8

J30

CON1

1

J23

CON1

1

C5

10nF/6.3V(10%)

C14

TBD

J26

CON1

1

J31

CON1

1

C6

3.3nF/6.3V(10%)

D1

ESD3.3V88D-LCDN

C9

0.1uF

J4

CON1

1

R3 499R

C11

1uF J22

CON1

1

J14

CON1

1

J35

CON1

1

C15

TBD

J36

CON1

1

J12

CON1

1

ANT1

PCB ANT

1

2

C16

270pF(NC)

J7

CON1

1

J25

CON1

1

J21

CON1

1

J6

CON1

1

J33

CON1

1

J17

CON1

1

J32

CON1

1

C17

270pF(NC)

J10

CON1

1

J1

CON1

1

J15

CON1

1

J3

CON1

1

J24

CON1

1

J37

CON1

1

J27

CON1

1

J2

CON1

1

U2 ESP32-D0WD

VDDA

1

LNA_IN

2

VDD3P3

3

VDD3P3

4

SENSOR_VP

5

SENSOR_CAPP

6

SENSOR_CAPN

7

SENSOR_VN

8

CHIP_PU

9

VDET_1

10

VDET_2

11

32K_XP

12

32K_XN

13

GPIO25

14

GPIO26

15

GPIO27

16

MTMS

17

MTDI

18

VDD3P3_RTC

19

MTCK

20

MTDO

21

GPIO2

22

GPIO0

23

GPIO4

24

VDD_SDIO 26

GPIO16 25

GPIO17 27

SD_DATA_2 28

SD_DATA_3 29

SD_CMD 30

SD_CLK 31

SD_DATA_0 32

GND 49

SD_DATA_1 33

GPIO5 34

GPIO18 35

GPIO19 38

CAP2 47

VDDA 43

XTAL_N 44

XTAL_P 45

GPIO23 36

U0TXD 41

GPIO22 39

GPIO21 42

VDD3P3_CPU 37

CAP1 48

VDDA 46

U0RXD 40

C20

1uF

L4 TBD

C1

TBD

C18

1uF

J20

CON1

1

J16

CON1

1

J5

CON1

1

C12

NC

U1

40MHz+/-10ppm

XIN

1

GND

2XOUT 3

GND 4

C21

NC

J29

CON1

1

J8

CON1

1

J13

CON1

1

C2

TBD

J19

CON1

1

J9

CON1

1

C4

0.1uF

C10

0.1uF

C3

100pF

J34

CON1

1

C19

0.1uF

J11

CON1

1

J38

CON1

1

R2

0R

J28

CON1

1

J18

CON1

1

Figure 3: ESP32 Analog Power Supply Pins

Notice:

• The recommended voltage of the power supply for ESP32 is 3.3 V, and its recommended output current is 500 mA

or more.

• It is suggested that users add an ESD tube at the power entrance.

2.1.2 Power-on Sequence and System Reset

2.1.2.1 Power-on Sequence

ESP32 uses a 3.3 V system power supply. The chip should be activated after the power rails have stabilized. This

is achieved by delaying the activation of CHIP_PU (Pin9) after the 3.3 V rails have been brought up. More details

can be found in section Power Scheme in ESP32 Datasheet.

Notice:

If CHIP_PU is driven by a power management chip, then the power management chip controls the ESP32 power

state. When the power management chip turns on/off Wi-Fi through the high/low level on GPIO, a pulse current

may be generated. To avoid level instability on CHIP_PU, an RC delay circuit is required.

2.1.2.2 Reset

CHIP_PU serves as the reset pin of ESP32. The input level (VIL_nRST ) for resetting the chip should be low enough

and remain so for a period of time. More details can be found in section Power Scheme in ESP32 Datasheet.

Espressif Systems 4 ESP32 Hardware Design Guidelines V2.7