4 - 4

4-2 TRANSMITTER CIRCUITS

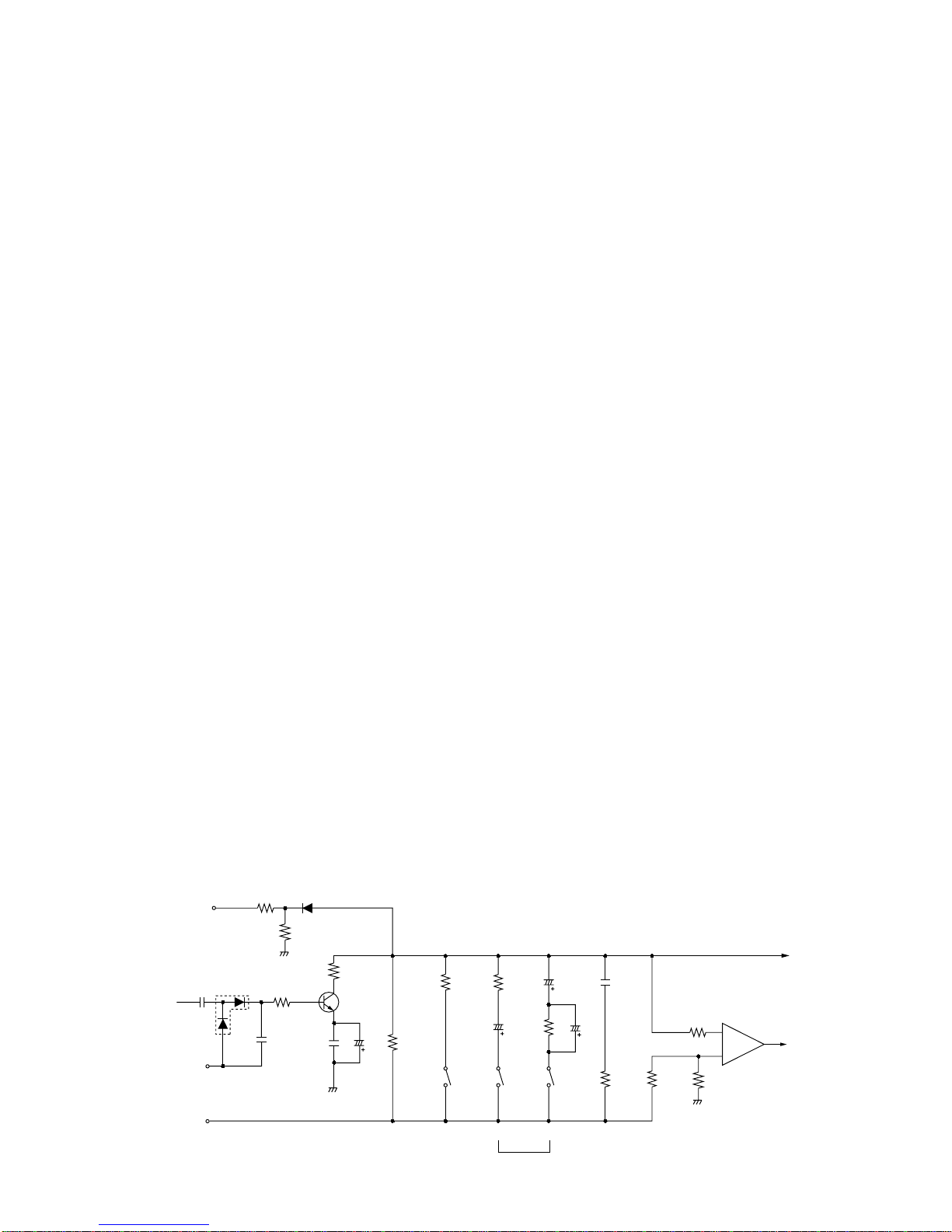

4-2-1 MICROPHONE AMPLIFIER CIRCUIT

(FRONT AND MAIN UNITS)

The microphone amplifier circuit amplifies microphone-input

signals and outputs the amplified signal to the balanced

modulator.

Audio signals from the [MIC] connector are applied to the

MIC amplifier IC (IC2201). IC2201 consists of the micro-

phone amplifier, microphone gain control, speech compres-

sor and VOX function. External modulation input from the

[ACC] socket (pin 11) is also applied to IC2201. The micro-

phone bias voltage is supplied from the 8V line via R2225

and R2201.

In AM mode, the ALC circuit (IC2351b, D2381) limits maxi-

mum level of the IC2201 output. The maximum modulation

level is set by R2385 (MAIN unit).

4-2-2 BALANCED MODULATOR (MAIN UNIT)

The balanced modulator converts the AF signal from the

microphone amplifier to a 455 kHz IF signal with a BFO sig-

nal.

Output signals from the microphone amplifier and the CW

keying signal are applied to the balanced modulator

(IC2301, pin 1). The BFO signal from the PLL unit is applied

to IC2301 (pin 10) as a carrier signal.

C2301 is a doubled balanced mixer IC and outputs a double

side band (DSB) signal with –40 dB carrier suppression.

R2303 adjusts the balanced level of IC2301 for maximum

carrier suppression. In CW mode, the CW keying signal

upsets the balance to create a carrier signal. In AM mode,

Q2302 and R2321 upset the balance to create an AM carri-

er signal.

4-2-3 CW KEYING CIRCUIT (MAIN UNIT)

When the CW key is closed, control signal is output from

CPU (LOGIC unit) and controls break-in operation, the side

tone signal.

The input signal (DOT or DAS) from CW keyer is applied to

the CPU (LOGIC unit; IC1, pins 71, 70) and then CPU out-

puts CW control signal (KDS) from pin 77. The CW control

signal is applied to the balanced modulator (IC2301) via

Q3701, Q3702, D3701 to unbalance the IC2301 input bias

voltage and create a carrier signal. R3703 determines the

transmit delay timing.

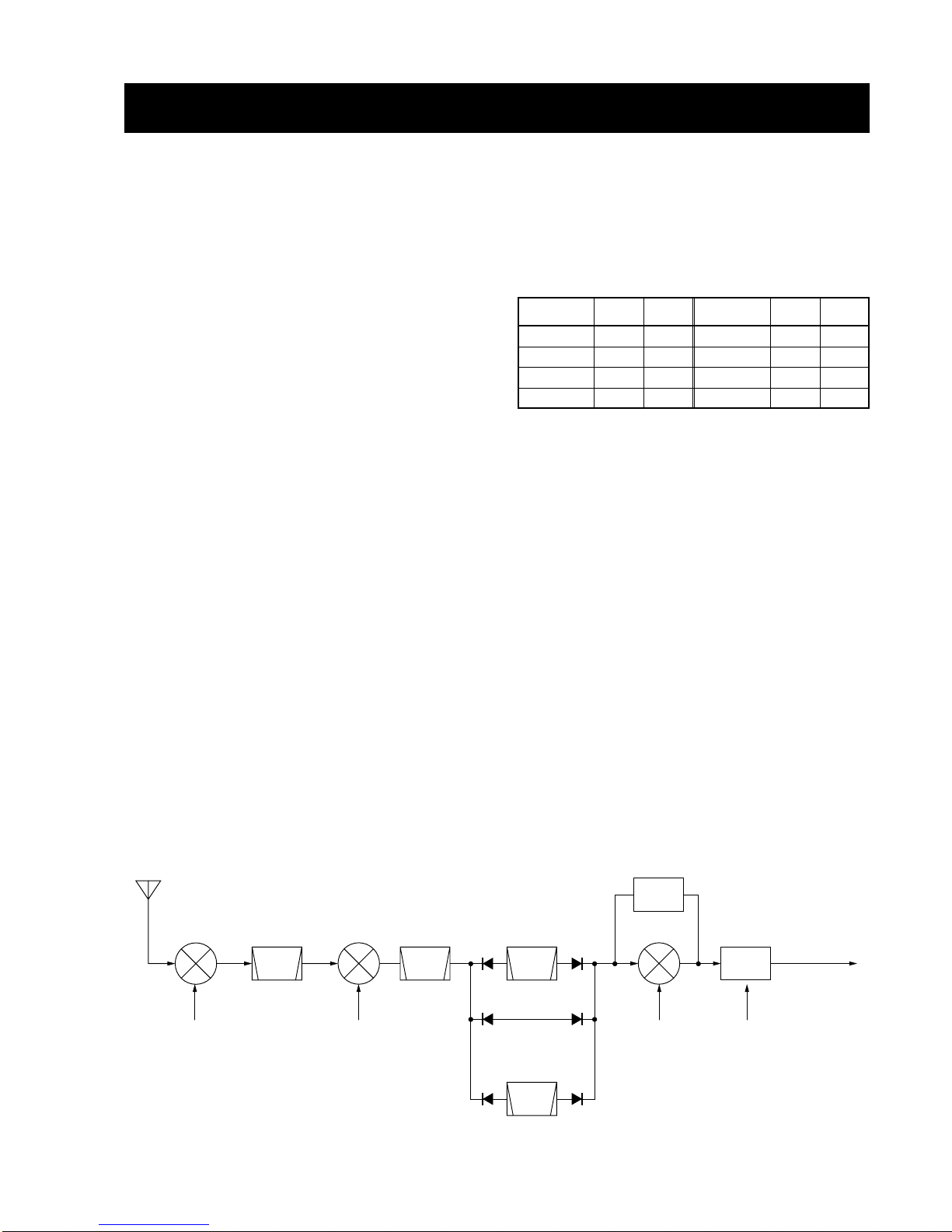

4-2-4 IF AMPLIFIER (MAIN UNIT)

The SSB/CW/RTTY 455 kHz IF signal passes through FI611

(FL-65) to suppress unwanted sideband signals, then the

signal is applied to a transmit IF amplifier (Q502). The

optional CW narrow filter is not used in transmitting.

The amplified signal from Q502 is mixed with the 2nd LO

signal and converted to a 64.455 MHz IF signal at D401.

D401 is used in receiving and transmitting. The AM signal

bypasses FI611, and is amplified at Q502 and is then

applied to D401.

The 64.455 MHz IF signal is filtered at FI301, amplified at

the IF amplifier (Q151) and is then converted to the dis-

played frequency at the balanced mixer (Q101, Q102) with

the 1st LO signal.

The gates of the IF amplifiers (Q151, Q502) are controlled

by ALC bias voltage from the ALC circuit. A thermistor

(R508), connected to the gate of Q502, improves the tem-

perature characteristics of the transmitter gain. R503 adjusts

the total transmitter gain.

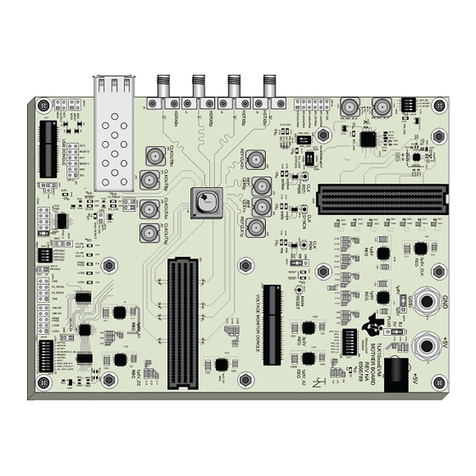

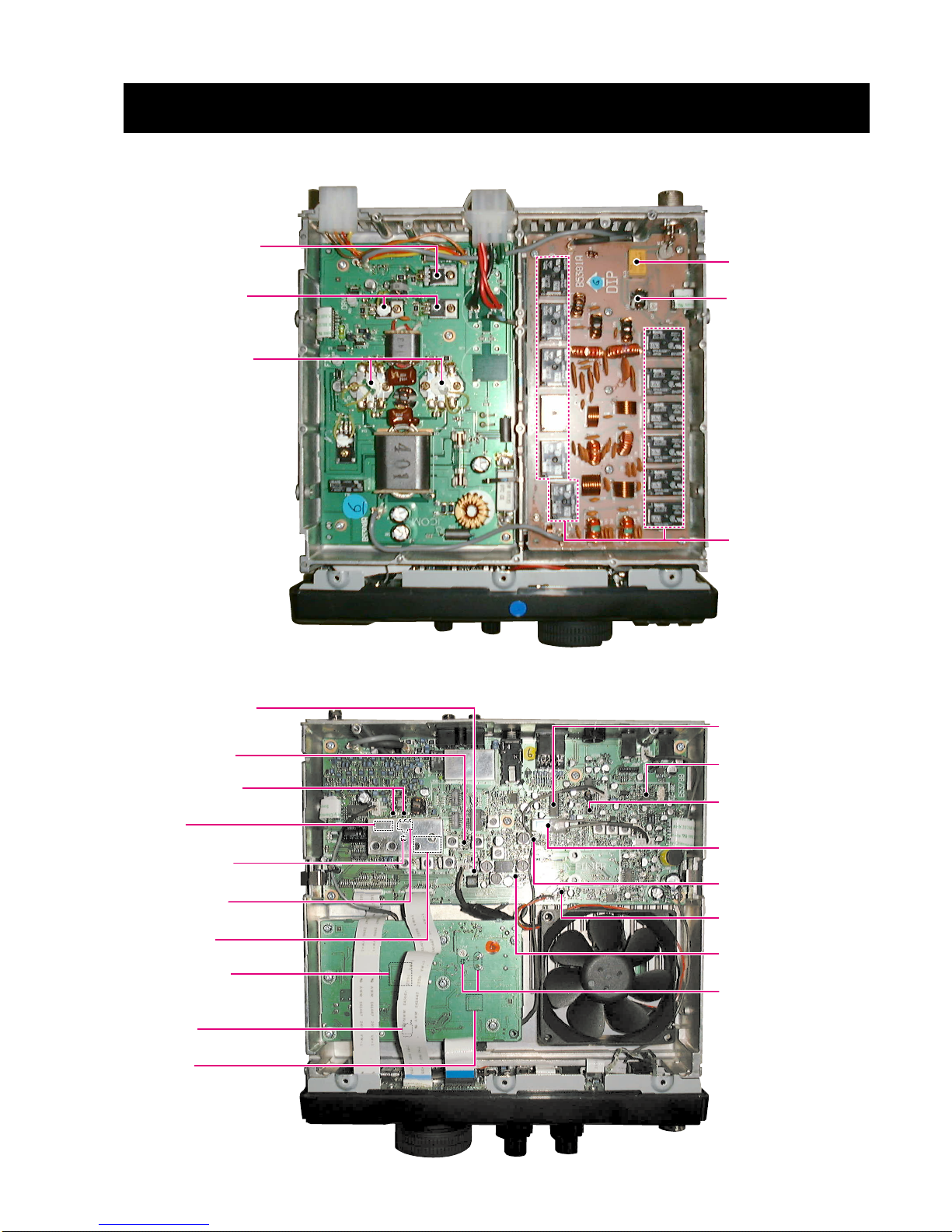

4-2-5 RF CIRCUIT (MAIN AND PA UNITS)

The displayed frequency signal converted at the balanced

mixer (MAIN unit; Q101, Q102) is applied to the bandpass

filter (L101–L103, C101–C107) where unwanted LO signal

emission is reduced. The filtered signal is attenuated at

R5–R7 and amplified at IC1, and is then applied to the PA

unit via the attenuator (R1–R3).

The signals from the MAIN unit are amplified at the predrive

amplifier (Q1), drive amplifier (Q2, Q3) and power amplifier

(Q4, Q5) in the PA unit to obtain a stable 100 W of RF out-

put power.

The predrive amplifier is a class-A amplifier with a VCC of

13.8 V. The drive amplifier is a class-AB push-pull amplifier

with a VCC of 13.8 V. D1 controls bias voltage to the drive

amplifier.

The impedance of the signal from the drive amplifier is con-

verted at L2, and then the signal is applied to the power

amplifier (Q4, Q5). The power amplifier is a class-AB push-

pull amplifier and amplifies the input signal to 100 W. D2 and

D3 control bias voltage to the power amplifier. The signal

from the power amplifier is applied to one of the low-pass fil-

ters in the FILTER unit.

4-2-6 LOW-PASS FILTER CIRCUIT (FILTER UNIT)

The low-pass filter circuit consists of 6 Chebyschev low-

pass filters to suppress the higher harmonic components.

The signal from the power amplifier (Q4, Q5) is applied to

one of the low-pass filters (depending on its frequency). The

filter switching voltage from the MAIN unit (J4001) is applied

to the FILTER unit via J1.

The filtered signal passes through the SWR detector circuit

(L13) and is then applied to the antenna connector.

4-2-7 ALC CIRCUIT (MAIN UNIT)

The ALC (Automatic Level Control) circuit controls the gain

of IF amplifiers in order for the IC-718 to output a constant

RF power set by the [RF PWR] control even when the sup-

plied voltage shifts, etc.

The “FOR”voltage from the FILTER unit is applied to

IC1701c (pin 9) in the MAIN unit. The “POCV”voltage from

the D/A converter (IC3301, pin 2), determined by the RF

power setting, is applied to IC1701c (pin 10) as the refer-

ence voltage.