Infineon TLE4997 User manual

Sense & Control

User’s Manual

v01_01, 2019-08

TLE4997

Configuration and Calibration of Linear Hall Sensor

Edition 2019-08

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2019 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties

and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest

Infineon Technologies Office (www.infineon.com).

Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in

question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

TLE4997

User’s Manual

Table of Contents

User’s Manual 3 v01_01, 2019-08

Table of Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 TLE4997 Signal Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3 TLE4997 Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1 Programmer Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2 Programming Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2.1 Communication Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.3 Command Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.3.1 Data Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.3.2 Interface Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.4 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.5 EEPROM Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.6 Programming Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.6.1 Setting the TEST register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.6.2 Readout of the EEPROM Content . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.6.3 Setting the EEPROM Content . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.6.4 Calculation of Bits to Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.6.5 Calculation of Bits to Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.6.6 Margin Voltage Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.6.7 DATA access example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.6.8 Temporary overwrite of EEPROM data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.6.9 DAC setup example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4 Configuration & Calibration Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.1 Magnetic Field Range - R . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2 Gain Setting - G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.3 Offset Setting - OS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.4 Low-Pass Filter - LP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.5 DAC Input Interpolation Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4.6 Clamping - CH, CL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.7 Temperature Compensation - TL, TQ & TT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5 Calibration of TLE4997 Temperature Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.1 Integrated Temperature Polynomial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.2 Application Sensitivity Polynomial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.3 Determination of Sensitivity Polynomial from Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.4 Calculation of Final Temperature Compensation Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

5.4.1 Algorithm for Finding the Optimum Temperature Coefficient Set . . . . . . . . . . . . . . . . . . . . . . . . . . 28

5.4.2 Example Implementation Code for Temperature Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

5.5 Usage of Infineon’s Temperature Calibration Tool . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6 Calibration of TLE4997 Output Characteristic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.1 Two-Point Calibration Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2 Two-Point Calibration Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.2.1 Calibration with Application Readout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.2.2 Calibration without Application Readout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table of Contents

TLE4997

User’s Manual

Scope

User’s Manual 4 v01_01, 2019-08

1Scope

This document is valid for all TLE4997 variants and derivates. It gives a detailed description of the configuration

and calibration procedure, which is recommended to configure the TLE4997 for optimum accuracy in a sensing

application.

2 TLE4997 Signal Processing

The TLE4997 uses a fully digital signal processing concept. Analog values from the Hall probe are directly

converted to raw digital signals by the Hall ADC and then compensated and processed in the digital signal

processing unit (DSP) using configuration parameters stored in the EEPROM and the temperature data acquired

by an integrated temperature sensor. A configurable second-order temperature polynomial is implemented to

compensate the thermal reduction of the remanent magnetic flux of a permanent magnet used in a position

sensing application. Additionally, an application-specific output characteristic can be set by configuring the

EEPROM parameters of Gain and Offset.

Figure 2-1 Signal Flow Diagram of the TLE4997

Figure 2-1 shows the signal flow diagram for temperature compensation and output characteristic in the DSP, and

the influence of the relevant configuration parameters stored in the EEPROM. The Hall signal is processed in the

following sequence of steps:

1. The analog Hall signal is converted by the Hall ADC, which operates at the configured magnetic range setting.

2. The digital value is filtered by a digital low-pass filter, which operates at a configurable filter frequency given

by the “LP filter”-setting. The output of the filter is stored in the HADC register.

3. The HADC value is multiplied by the temperature compensation polynomial and stored in the HCAL register.

The first order (TL) and second order (TQ) coefficients of the polynomial are configurable. The third order

coefficient (TT) is fixed.

4. The HCAL value is multiplied by the configured gain value.

5. The configured offset value is added to the HCAL value.

6. The digital Hall value is clamped according to the configured upper and lower clamping limits. The output value

of the clamping stage is converted from digital to analog.

7. An output voltage is transmitted on the OUT pin and is proportional to the supply voltage (ratiometric DAC).

Stored in

EEPROM

Memory

+

A

D

Hall

Sensor

Limiter

(Clamp)

Out

X

Range LP

Offset

Gain

x

Clamping Low

Clamping High

A

D

TADC TCAL

Temperature

Sensor

Norm-

alize T-Polynomial

TL

TT

TQ

HADC

HCAL

VOUT

D

A

VDAC

TLE4997

User’s Manual

TLE4997 Programming

User’s Manual 5 v01_01, 2019-08

3 TLE4997 Programming

3.1 Programmer Connection

Figure 3-1 shows the connection of the TLE4997 to a programmer. The pins VDD and OUT of the sensor IC are

used for the digital programming interface as described in Table 3-1 (See datasheet of corresponding TLE4997

type for pinout).

Figure 3-1 Connection of TLE4997 to Programmer

Table 3-1 Pin Functions for Programming Interface

Pin Programming Function

VDD Programming interface clock

GND Ground

OUT Programming interface data I/O

optional

VDD

I/O 1

I/O2

GND

47nF

47nF

47nF

47nF

PROGRAMMER

TLE

4997x

out

V

DD

GND

TLE

4997x

out

V

DD

GND

application module

Table of contents

Other Infineon Accessories manuals

Infineon

Infineon TLI493D-A2B6 User manual

Infineon

Infineon XENSIV BGT60TR13C User manual

Infineon

Infineon SP37 Instruction and safety manual

Infineon

Infineon TLE493D-A2B6 User manual

Infineon

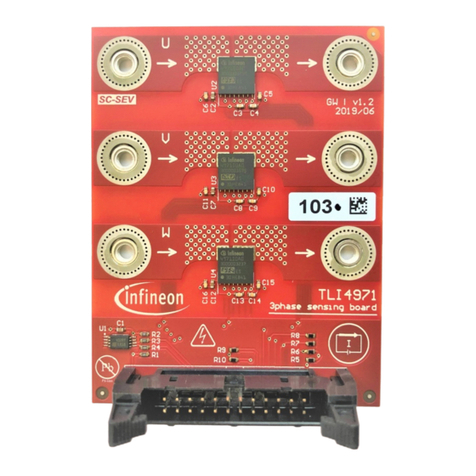

Infineon XENSIV TLI4971 Operating instructions

Infineon

Infineon TLI4970 Mounting instructions

Infineon

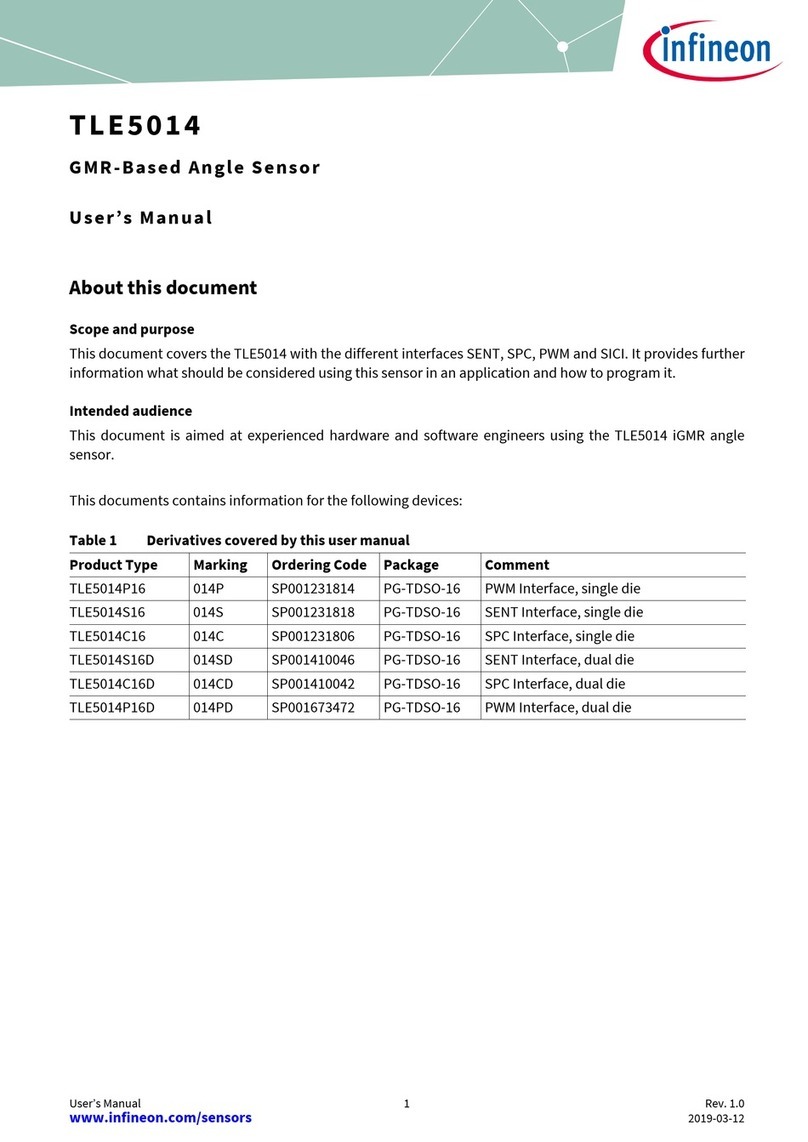

Infineon TLE5014P16 User manual

Infineon

Infineon TLE5501 Series User manual

Infineon

Infineon TLI4970-D050T4 CurrentSense Shield2Go User manual