Ingenic JZ4780 Owner's manual

JZ4780

Mobile Application Processor

Programming Manual

Release Date: Jan 6, 2013

JZ4780 Mobile Application Processor

Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co. Ltd. All rights reserved.

Disclaimer

This documentation is provided for use with Ingenic products. No license to Ingenic property rights is

granted. Ingenic assumes no liability, provides no warranty either expressed or implied relating to the

usage, or intellectual property right infringement except as provided for by Ingenic Terms and

Conditions of Sale.

Ingenic products are not designed for and should not be used in any medical or life sustaining or

supporting equipment.

All information in this document should be treated as preliminary. Ingenic may make changes to this

document without notice. Anyone relying on this documentation should contact Ingenic for the current

documentation and errata.

Ingenic Semiconductor Co., Ltd.

Room 108, Building A, Information Center, Zhongguancun Software Park

8 Dongbeiwang West Road, Haidian District, Beijing, China,

Tel: 86-10-82826661

Fax: 86-10-82825845

Http: //www.ingenic.cn

CONTENTS

i

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

CONTENTS

CONTENTS.............................................................................................i

TABLES...................................................................................................i

FIGURES.................................................................................................i

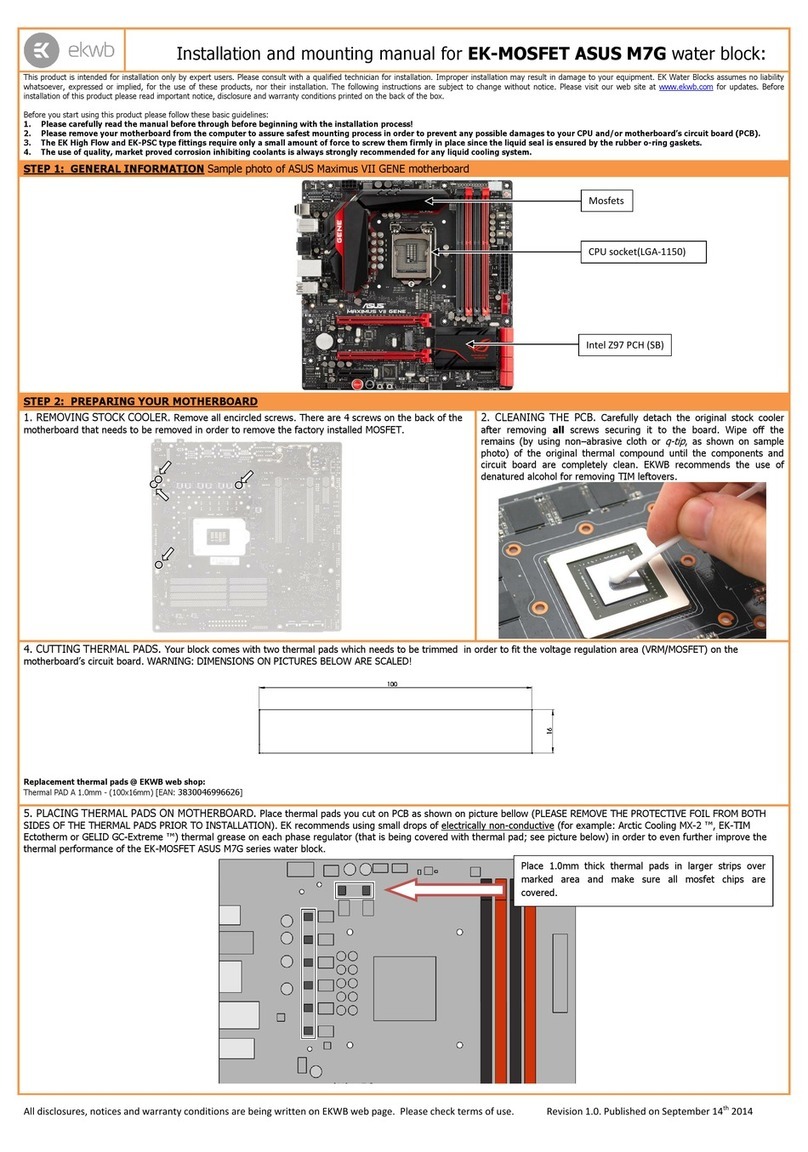

Section 1 Overview

1Overview .......................................................................................... 2

1.1 Block Diagram......................................................................................................................... 3

1.2 Features.................................................................................................................................. 3

1.2.1 CPU................................................................................................................................. 3

1.2.2 VPU................................................................................................................................. 4

1.2.3 GPU................................................................................................................................. 4

1.2.4 Display............................................................................................................................. 5

1.2.5 Camera............................................................................................................................ 7

1.2.6 Audio ............................................................................................................................... 7

1.2.7 Memory Interface ............................................................................................................ 9

1.2.8 System............................................................................................................................. 9

1.2.9 Peripheral.......................................................................................................................11

1.2.10 Bootrom......................................................................................................................... 14

1.3 Characteristic........................................................................................................................ 14

Section 2 Core Functions

2CPU................................................................................................ 16

2.1 Overview............................................................................................................................... 16

2.2 CP0 Register Description...................................................................................................... 16

2.2.1 Cores Control (CP0 Register 12, Select 2)................................................................... 16

2.2.2 Cores Status (CP0 Register 12, Select 3)..................................................................... 17

2.2.3 Reset Entry & IRQ Mask (CP0 Register 12, Select 4).................................................. 17

2.2.4 SPINLOCK (CP0 Register 12, Select 5)....................................................................... 18

2.2.5 SPINATOMIC (CP0 Register 12, Select 6) ................................................................... 18

2.2.6 Processor Identification (CP0 Register 15, Select 0).................................................... 19

2.2.7 EBase (CP0 Register 15, Select 1)............................................................................... 19

2.2.8 Config1 Register (CP0 Register 16, Select 1)............................................................... 19

2.2.9 Config7 Register (CP0 Register 16, Select 7)............................................................... 20

2.2.10 Mailbox0 (CP0 Register 20, Select 0)........................................................................... 21

2.2.11 Mailbox1 (CP0 Register 20, Select 1)........................................................................... 21

2.3 Application Notes.................................................................................................................. 21

CONTENTS

ii

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

2.3.1 Mapping of IRQs observed by CPU core ......................................................................22

2.3.2 EJTAG debug for multiple cores....................................................................................22

3VPU ................................................................................................23

3.1 Block Diagram.......................................................................................................................23

3.2 Features of VPU....................................................................................................................24

3.3 Internal physical address base definition ..............................................................................25

3.4 AUX .......................................................................................................................................26

3.4.1 Register Definition .........................................................................................................26

3.5 TCSM/SRAM.........................................................................................................................29

3.5.1 TCSM/SRAM space usage............................................................................................29

3.6 Video Acceleration Block.......................................................................................................29

4GPU................................................................................................30

4.1 3D graphics ...........................................................................................................................30

4.1.1 Introduction....................................................................................................................30

4.1.2 PowerVR SGX Architecture - Key Features ..................................................................30

4.1.3 SGX540 –3D Features .................................................................................................30

4.1.4 SGX540 –Performance.................................................................................................32

4.2 EXtreme 2D...........................................................................................................................32

4.2.1 Overview........................................................................................................................32

4.2.2 Registers Descriptions...................................................................................................33

4.3 Software stack.......................................................................................................................45

Section 3 Display/Camera/Audio

5LCD Controller................................................................................47

5.1 Overview................................................................................................................................47

5.2 Pin Description ......................................................................................................................48

5.3 Block Diagram.......................................................................................................................49

5.4 LCD Display Timing...............................................................................................................51

5.5 OSD Graphic.........................................................................................................................52

5.5.1 Color Key.......................................................................................................................52

5.6 Register Description..............................................................................................................54

5.6.1 Configure Register (LCDCFG).......................................................................................56

5.6.2 Control Register (LCDCTRL).........................................................................................58

5.6.3 Status Register (LCDSTATE).........................................................................................59

5.6.4 OSD Configure Register (LCDOSDC)...........................................................................59

5.6.5 OSD Control Register (LCDOSDCTRL)........................................................................61

5.6.6 OSD State Register (LCDOSDS)...................................................................................61

5.6.7 Background0 Color Register (LCDBGC0).....................................................................62

5.6.8 Background1 Color Register (LCDBGC1).....................................................................62

5.6.9 Foreground Color Key Register 0 (LCDKEY0)..............................................................62

CONTENTS

iii

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

5.6.10 Foreground Color Key Register 1 (LCDKEY1).............................................................. 63

5.6.11 ALPHA Register (LCDALPHA) ................................................................................... 63

5.6.12 IPU Restart (LCDIPUR)................................................................................................. 64

5.6.13 RGB Control (LCDRGBC) .......................................................................................... 64

5.6.14 Virtual Area Setting (LCDVAT) ...................................................................................... 66

5.6.15 Display Area Horizontal Start/End Point (LCDDAH)...................................................... 66

5.6.16 Display Area Vertical Start/End Point (LCDDAV) .......................................................... 67

5.6.17 Foreground 0 XY Position Register (LCDXYP0)........................................................ 67

5.6.18 Foreground 1 XY Position Register (LCDXYP1)........................................................ 67

5.6.19 Foreground 0 Size Register (LCDSIZE0)................................................................... 68

5.6.20 Foreground 1 Size Register (LCDSIZE1)................................................................... 68

5.6.21 Vertical Synchronize Register (LCDVSYNC) ................................................................ 68

5.6.22 Horizontal Synchronize Register (LCDHSYNC)............................................................ 69

5.6.23 PS Signal Setting (LCDPS)........................................................................................... 69

5.6.24 CLS Signal Setting (LCDCLS) ...................................................................................... 70

5.6.25 SPL Signal Setting (LCDSPL)....................................................................................... 70

5.6.26 REV Signal Setting (LCDREV)...................................................................................... 70

5.6.27 Interrupt ID Register (LCDIID)....................................................................................... 71

5.6.28 Descriptor Address Registers (LCDDAx) ...................................................................... 71

5.6.29 Source Address Registers (LCDSA) ............................................................................. 72

5.6.30 Frame ID Registers (LCDFIDx)..................................................................................... 72

5.6.31 DMA Command Registers (LCDCMDx)........................................................................ 73

5.6.32 DMA OFFSIZE Registers (LCDOFFSx)........................................................................ 74

5.6.33 DMA Page Width Registers (LCDPWx) ........................................................................ 74

5.6.34 DMA Commend Counter Registers (LCDCNUMx) ....................................................... 75

5.6.35 DMA Commend Counter Registers (LCDCPOSx)........................................................ 75

5.6.36 Foreground x Size in Descriptor (LCDDESSIZEx)........................................................ 76

5.6.37 Priority level threshold configure Register (LCDPCFG)................................................ 77

5.6.38 Dual LCDC Channel Control(LCDCDUALCTRL).......................................................... 78

5.6.39 Image Enhancement CFG (LCDENH_CFG)................................................................. 78

5.6.40 Color Space Conversion CFG (LCDENH_CSCCFG) ................................................... 79

5.6.41 LUMA CFG (LCDENH_LUMACFG) .............................................................................. 80

5.6.42 CHROMA0 CFG (LCDENH_CHROCFG0) ................................................................... 81

5.6.43 CHROMA1 CFG (LCDENH_CHROCFG1) ................................................................... 81

5.6.44 DITHER CFG (LCDENH_DITHERCFG)....................................................................... 81

5.6.45 Enhance status (LCDENH_STATUS)............................................................................ 82

5.6.46 GAMMA CFG (LCDENH_GAMMA) .............................................................................. 82

5.6.47 VEE CFG (LCDENH_VEE)........................................................................................... 83

5.7 LCD Controller Pin Mapping................................................................................................. 83

5.7.1 TFT and CCIR Pin Mapping.......................................................................................... 83

5.7.2 Data mapping to GPIO function. ................................................................................... 85

5.8 Display Timing....................................................................................................................... 86

5.8.1 General 16-bit and 18-bit TFT Timing ........................................................................... 86

CONTENTS

iv

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

5.8.2 8-bit Serial TFT Timing...................................................................................................87

5.8.3 Special TFT Timing........................................................................................................87

5.8.4 Delta RGB panel timing .................................................................................................89

5.8.5 RGB Dummy mode timing.............................................................................................89

5.9 Format of Frame Buffer.........................................................................................................90

5.9.1 16bpp.............................................................................................................................90

5.9.2 18bpp.............................................................................................................................90

5.9.3 24bpp.............................................................................................................................91

5.9.4 16bpp with alpha............................................................................................................91

5.9.5 18bpp with alpha............................................................................................................91

5.9.6 24bpp with alpha............................................................................................................91

5.9.7 24bpp compressed ........................................................................................................91

5.10 Format of Data Pin Utilization................................................................................................92

5.10.1 18-bit Parallel TFT .........................................................................................................92

5.10.2 16-bit Parallel TFT .........................................................................................................92

5.10.3 8-bit Serial TFT (24bpp).................................................................................................92

5.11 LCD Controller Operation......................................................................................................93

5.11.1 Set LCD Controller AHB Clock and Pixel Clock ............................................................93

5.11.2 Enabling the Controller ..................................................................................................93

5.11.3 Disabling the Controller .................................................................................................93

5.11.4 Resetting the Controller.................................................................................................94

5.11.5 Frame Buffer..................................................................................................................94

5.11.6 CCIR601/CCIR656 ........................................................................................................94

5.11.7 OSD Operation ..............................................................................................................94

5.11.8 Descriptor Operation......................................................................................................95

5.11.9 IPU direct connect mode ...............................................................................................96

5.11.10 VGA output.................................................................................................................96

6Smart LCD Controller......................................................................97

6.1 Overview................................................................................................................................97

6.2 Structure................................................................................................................................97

6.3 Pin Description ......................................................................................................................98

6.4 Register Description..............................................................................................................98

6.4.1 SLCD Configure Register (MCFG)................................................................................99

6.4.2 SLCD Control Register (MCTRL) ................................................................................100

6.4.3 SLCD Status Register (MSTATE) ................................................................................101

6.4.4 SLCD Data Register (MDATA).....................................................................................101

6.5 System Memory Format......................................................................................................102

6.5.1 Data format..................................................................................................................102

6.5.2 Command Format........................................................................................................102

6.6 Transfer Mode .....................................................................................................................103

6.6.1 DMATransfer Mode.....................................................................................................103

6.6.2 Register Transfer Mode ...............................................................................................104

CONTENTS

v

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

6.7 Timing ................................................................................................................................. 104

6.7.1 Parallel Timing............................................................................................................. 104

6.7.2 Serial Timing................................................................................................................ 105

6.8 Operation Guide.................................................................................................................. 105

6.8.1 DMA Operation............................................................................................................ 105

6.8.2 Register Operation ...................................................................................................... 106

7Decompresser.............................................................................. 107

7.1 Overview............................................................................................................................. 107

7.2 Compress Method............................................................................................................... 107

7.3 Operation Guide.................................................................................................................. 109

8Image Enhancement .....................................................................110

8.1 Overview..............................................................................................................................110

8.2 Operation Guide...................................................................................................................110

9Image Process Unit.......................................................................111

9.1 Overview..............................................................................................................................111

9.1.1 Feature.........................................................................................................................111

9.2 Block ....................................................................................................................................112

9.3 Data flow..............................................................................................................................112

9.3.1 Input data......................................................................................................................112

9.3.2 Output data...................................................................................................................112

9.3.3 Resize Coefficients LUT...............................................................................................112

9.4 Registers Descriptions.........................................................................................................113

9.4.1 IPU global Control Register..........................................................................................114

9.4.2 IPU OSD Control Register............................................................................................114

9.4.3 IPU Frame Control Register.........................................................................................115

9.4.4 IPU Status Register......................................................................................................116

9.4.5 IPU trigger register .......................................................................................................117

9.4.6 IPU register configure enable control register..............................................................117

9.4.7 Data Format Register...................................................................................................118

9.4.8 Input Y Data Address Register.....................................................................................119

9.4.9 Input U Data Address Register.................................................................................... 120

9.4.10 Input V Data Address Register.................................................................................... 120

9.4.11 Input source TLB base address .................................................................................. 121

9.4.12 Destination TLB base address.................................................................................... 121

9.4.13 Input Y Data Address of next frame Register.............................................................. 122

9.4.14 Input U Data Address of next frame Register.............................................................. 122

9.4.15 Input V Data Address of next frame Register.............................................................. 122

9.4.16 Source TLB base address of next frame..................................................................... 123

9.4.17 Destination TLB base address of next frame.............................................................. 123

9.4.18 ADDRESS Mapping.................................................................................................... 124

CONTENTS

vi

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

9.4.19 Input Geometric Size Register.....................................................................................124

9.4.20 Input Y Data Line Stride Register ................................................................................125

9.4.21 Input UV Data Line Stride Register..............................................................................125

9.4.22 Output Frame Start Address Register..........................................................................125

9.4.23 Output Data Address of next frame Register...............................................................126

9.4.24 Output Frame offset on screan Register .....................................................................126

9.4.25 Output Geometric Size Register..................................................................................127

9.4.26 Output Data Line Stride Register.................................................................................127

9.4.27 CSC C0 Coefficient Register .......................................................................................128

9.4.28 CSC C1 Coefficient Register .......................................................................................128

9.4.29 CSC C2 Coefficient Register .......................................................................................129

9.4.30 CSC C3 Coefficient Register .......................................................................................129

9.4.31 CSC C4 Coefficient Register .......................................................................................129

9.4.32 Resize Coefficients Table Index Register ....................................................................130

9.4.33 Horizontal Resize Coefficients Look Up Table Register group....................................130

9.4.34 Vertical Resize Coefficients Look Up Table Register group ........................................135

9.4.35 Calculation for Resized width and height ....................................................................136

9.4.36 CSC Offset Parameter Register ..................................................................................137

9.5 IPU Operation Flow.............................................................................................................138

9.5.1 Data out to frame buffer...............................................................................................138

9.5.2 Data out to lcdc............................................................................................................139

9.5.3 Operation example ......................................................................................................140

9.6 Special Instruction ...............................................................................................................142

9.6.1 Resizing size feature ...................................................................................................142

9.6.2 Color convention feature..............................................................................................142

9.6.3 YUV/YCbCr to RGB CSC Equations...........................................................................143

9.6.4 Output data package format (RGB order)....................................................................143

9.6.5 Input data package format (RGB order) ......................................................................144

9.6.6 Source Data storing format in external memory (separated YUV Frame)...................144

10 LVDS Controller ............................................................................146

10.1 Overview..............................................................................................................................146

10.2 Register Description............................................................................................................146

10.2.1 TXCTRL (LVDS Transmitter Control Register) ............................................................146

10.2.2 TXPLL0 (LVDS Transmitter‘s PLL Control Register 0) ................................................148

10.2.3 TXPLL1 (LVDS Transmitter‘s PLL Control Register 0) ................................................149

10.2.4 TXECTRL (LVDS Transmitter‘s Enhance Control) ......................................................149

10.3 Operate Description ............................................................................................................150

10.3.1 Operate Mode..............................................................................................................150

10.3.2 LVDS Output Amplitude Control ..................................................................................150

10.3.3 LVDS Input Clock Edge-Delay Control........................................................................151

10.3.4 Output data start-edge Control....................................................................................152

10.3.5 PLL Input Divider Value Setting...................................................................................152

CONTENTS

vii

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

10.3.6 PLL Feedback Divider Value Setting........................................................................... 152

10.3.7 VCO Gain Calibration.................................................................................................. 153

10.3.8 PLL Output Clock Frequency Setting.......................................................................... 153

10.3.9 LVDS-LCDC RGB Data Mapping................................................................................ 153

10.3.10 LVDS VESA/JEIDA Mode........................................................................................ 154

10.4 Operate Flow ...................................................................................................................... 155

10.4.1 Power Down Mode...................................................................................................... 155

10.4.2 LVDS Output Mode ..................................................................................................... 156

10.4.3 RGB CMOS Output Mode........................................................................................... 156

11 Camera Interface Module............................................................. 157

11.1 Overview............................................................................................................................. 157

11.1.1 Features ...................................................................................................................... 157

11.1.2 Pin Description ............................................................................................................ 157

11.2 CIM Special Register .......................................................................................................... 158

11.2.1 CIM Register Map ....................................................................................................... 158

11.2.2 CIM Configuration Register (CIMCFG) ....................................................................... 158

11.2.3 CIM Control Register (CIMCR) ................................................................................... 161

11.2.4 CIM Control Register 2 (CIMCR2) .............................................................................. 162

11.2.5 CIM Status Register (CIMST)...................................................................................... 164

11.2.6 CIM Interrupt Mask Register (CIMIMR)....................................................................... 166

11.2.7 CIM Interrupt ID Register (CIMIID).............................................................................. 166

11.2.8 CIM Descriptor Address (CIMDA) ............................................................................... 167

11.2.9 CIM Frame buffer Address Register (CIMFA) ............................................................. 167

11.2.10 CIM Frame ID Register (CIMFID)............................................................................ 168

11.2.11 CIM DMA Command Register (CIMCMD)............................................................... 168

11.2.12 CIM Window Size (CIMWSIZE)............................................................................... 169

11.2.13 CIM Window Offset (CIMWOFFSET)...................................................................... 170

11.2.14 CIM Frame Size Register (CIMFS) ......................................................................... 170

11.2.15 CIM Y Frame buffer Address Register (CIMYFA).................................................... 171

11.2.16 CIM Y DMA Command Register (CIMYCMD)......................................................... 171

11.2.17 CIM Cb Frame buffer Address Register (CIMCBFA)............................................... 172

11.2.18 CIM Cb DMA Command Register (CIMCBCMD).................................................... 172

11.2.19 CIM Cr Frame buffer Address Register (CIMCRFA) ............................................... 173

11.2.20 CIM Cr DMA Command Register (CIMCRCMD)..................................................... 173

11.2.21 CIM TLB Control Register (CIMTC) ........................................................................ 174

11.2.22 CIM TLB Index Register (CIMTINX)........................................................................ 174

11.2.23 CIM TLB Content Register (CIMTCNT)................................................................... 175

11.3 CIM Data Sampling Modes................................................................................................. 175

11.3.1 Gated Clock Mode....................................................................................................... 175

11.3.2 ITU656 Interlace Mode................................................................................................ 176

11.3.3 ITU656 Progressive Mode........................................................................................... 177

11.4 DMA Descriptors................................................................................................................. 178

CONTENTS

viii

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

11.4.1 4-Word Descriptor........................................................................................................178

11.4.2 8-Word Descriptor........................................................................................................178

11.5 Interrupt Generation ............................................................................................................179

11.6 Software Operation..............................................................................................................180

11.6.1 Enable CIM with DMA..................................................................................................180

11.6.2 Enable CIM without DMA.............................................................................................180

11.6.3 Disable CIM .................................................................................................................180

12 AC97/I2S/SPDIF Controller...........................................................181

12.1 Overview..............................................................................................................................181

12.1.1 Block Diagram..............................................................................................................182

12.1.2 Features.......................................................................................................................182

12.1.3 Interface Diagram ........................................................................................................183

12.1.4 Signal Descriptions......................................................................................................186

12.2 Register Descriptions ..........................................................................................................188

12.2.1 AIC Configuration Register (AICFR)............................................................................190

12.2.2 AIC Common Control Register (AICCR) .....................................................................193

12.2.3 AIC AC-link Control Register 1 (ACCR1).....................................................................196

12.2.4 AIC AC-link Control Register 2 (ACCR2).....................................................................197

12.2.5 AIC I2S/MSB-justified Control Register (I2SCR).........................................................198

12.2.6 AIC Controller FIFO Status Register (AICSR).............................................................199

12.2.7 AIC AC-link Status Register (ACSR)............................................................................201

12.2.8 AIC I2S/MSB-justified Status Register (I2SSR)...........................................................202

12.2.9 AIC AC97 CODEC Command Address & Data Register (ACCAR, ACCDR)..............203

12.2.10 AIC AC97 CODEC Status Address & Data Register (ACSAR, ACSDR) .................204

12.2.11 AIC I2S/MSB-justified Clock Divider Register (I2SDIV)...........................................205

12.2.12 AIC FIFO Data Port Register (AICDR).....................................................................205

12.2.13 SPDIF Enable Register (SPENA)............................................................................206

12.2.14 SPDIF Control Register (SPCTRL)..........................................................................206

12.2.15 SPDIF State Register (SPSTATE) ...........................................................................208

12.2.16 SPDIF Configure 1 Register (SPCFG1) ..................................................................208

12.2.17 SPDIF Configure 2 Register (SPCFG2) ..................................................................209

12.2.18 SPDIF FIFO Register (SPFIFO) ..............................................................................211

12.3 Serial Interface Protocol......................................................................................................211

12.3.1 AC-link serial data format ............................................................................................211

12.3.2 I2S and MSB-justified serial audio format ...................................................................212

12.3.3 Audio sample data placement in SDATA_IN/SDATA_OUT .........................................214

12.3.4 SPDIF Protocol............................................................................................................216

12.4AC97/I2S Operation ............................................................................................................216

12.4.1 Initialization..................................................................................................................217

12.4.2 AC ‘97 CODEC Power Down.......................................................................................218

12.4.3 Cold and Warm AC ‘97 CODEC Reset........................................................................218

12.4.4 External CODEC Registers Access Operation............................................................219

CONTENTS

ix

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

12.4.5 Audio Replay............................................................................................................... 220

12.4.6 Audio Record............................................................................................................... 221

12.4.7 FIFOs operation .......................................................................................................... 222

12.4.8 Data Flow Control........................................................................................................ 224

12.4.9 Audio Samples format................................................................................................. 225

12.4.10 Serial Audio Clocks and Sampling Frequencies ..................................................... 227

12.4.11 Interrupts.................................................................................................................. 231

12.5 SPDIF Guide....................................................................................................................... 231

12.5.1 Set SPDIF clock frequency ......................................................................................... 231

12.5.2 PCM audio mode operation (Reference IEC60958) ................................................... 231

12.5.3 Non-PCM mode operation (Reference IEC61937) ..................................................... 232

12.5.4 Disable operation ........................................................................................................ 232

13 PCM Interface .............................................................................. 233

13.1 Overview............................................................................................................................. 233

13.2 Pin Description.................................................................................................................... 233

13.3 Block Diagram..................................................................................................................... 234

13.4 Register Description............................................................................................................ 234

13.4.1 PCM Control Register (PCMCTL)............................................................................... 234

13.4.2 PCM Configuration Register (PCMCFG) .................................................................... 236

13.4.3 PCM FIFO DATA PORT REGISTER (PCMDP) .......................................................... 237

13.4.4 PCM INTERRUPT CONTROL REGISTER (PCMINTC)............................................. 237

13.4.5 PCM INTERRUPT STATUS REGISTER (PCMINTS)................................................. 238

13.4.6 PCM CLOCK DIVIDE REGISTER (PCMDIV)............................................................. 239

13.5 PCM Interface Timing ......................................................................................................... 240

13.5.1 Short Frame SYN........................................................................................................ 240

13.5.2 Long Frame SYN......................................................................................................... 241

13.5.3 Multi-Slot Operation..................................................................................................... 242

13.6 PCM Operation ................................................................................................................... 242

13.6.1 PCM Initialization......................................................................................................... 242

13.6.2 Audio Replay............................................................................................................... 243

13.6.3 Audio Record............................................................................................................... 243

13.6.4 FIFOs operation .......................................................................................................... 244

13.6.5 Data Flow Control........................................................................................................ 245

13.6.6 PCM Serial Clocks and Sampling Frequencies .......................................................... 245

13.6.7 Interrupts ..................................................................................................................... 246

14 Internal CODEC Interface............................................................. 247

14.1 Overview............................................................................................................................. 247

14.2 Features.............................................................................................................................. 247

14.2.1 Signal Descriptions...................................................................................................... 248

14.2.2 Block Diagram............................................................................................................. 249

14.2.3 Application schematic.................................................................................................. 250

CONTENTS

x

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

14.3 Mapped Register Descriptions............................................................................................251

14.3.1 CODEC internal register access control (RGADW).....................................................251

14.3.2 CODEC internal register data output (RGDATA).........................................................252

14.4 Operation.............................................................................................................................253

14.4.1 Access to internal registers of the embedded CODEC ...............................................253

14.4.2 CODEC controlling and typical operations ..................................................................253

14.4.3 Power saving ...............................................................................................................254

14.4.4 Pop noise and the reduction of it.................................................................................254

14.5 Timing parameters...............................................................................................................255

14.6 C parameters.......................................................................................................................256

14.7 CODEC internal Registers ..................................................................................................257

14.7.1 CODEC internal registers ............................................................................................258

14.8 Programmable gains ...........................................................................................................285

14.8.1 Programmable boost gain: GIM...................................................................................285

14.8.2 Programmable input gain amplifier: GID .....................................................................286

14.8.3 Programmable digital attenuation: GOD......................................................................286

14.8.4 Programmable attenuation: GO...................................................................................287

14.8.5 Programmable Bypass path attenuation: GI................................................................288

14.8.6 Programmable digital mixer gain: GIMIX and GOMIX.................................................288

14.8.7 Gain refresh strategy ...................................................................................................289

14.9 Configuration of the headphone output stage.....................................................................289

14.10 Out-of-band noise filtering...................................................................................................289

14.11 Output short-circuit protection (headphone output).............................................................290

14.11.1 Indication of the short circuit detection ....................................................................290

14.11.2 Reset of short circuit detection.................................................................................290

14.11.3 Capacitor-coupled headphone connection ..............................................................290

14.12 Sampling frequency: FREQ.................................................................................................290

14.13 Programmable data word length.........................................................................................291

14.14 Ramping system note..........................................................................................................291

14.15 AGC system guide ..............................................................................................................292

14.15.1 AGC operating mode ...............................................................................................292

14.16 Digital Mixer description ......................................................................................................295

14.17 Digital microphone interface................................................................................................296

14.17.1 Timing Diagram........................................................................................................297

14.17.2 Timings.....................................................................................................................297

14.17.3 Noise template (TBC) ..............................................................................................298

14.18 CODEC Operating modes...................................................................................................298

14.18.1 Power-On mode and Power-Off mode ....................................................................299

14.18.2 RESET mode...........................................................................................................299

14.18.3 STANDBY mode ......................................................................................................300

14.18.4 SLEEP mode............................................................................................................300

14.18.5 Initial all the gain ......................................................................................................301

14.18.6 Soft Mute mode........................................................................................................301

CONTENTS

xi

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

14.18.7 Power-Down mode and ACTIVE mode................................................................... 302

14.18.8 Working modes summary........................................................................................ 302

14.19 SYS_CLK turn-off and turn-on............................................................................................ 303

14.20 Requirements on outputs and inputs selection and power-down modes ........................... 304

14.21 Anti-pop operation sequences............................................................................................ 304

14.21.1 Initialization and configuration................................................................................. 304

14.21.2 Start up sequence (DAC)......................................................................................... 304

14.21.3 Shutdown sequence (DAC)..................................................................................... 306

14.21.4 Start up sequence (Line input) ................................................................................ 307

14.21.5 Shutdown sequence (Line input)............................................................................. 308

14.22 Circuits design suggestions................................................................................................ 309

14.22.1 Avoid quiet ground common currents...................................................................... 309

14.22.2 Headphone connection (Capacitor-coupled)........................................................... 310

14.22.3 Microphone connection ........................................................................................... 310

14.22.4 Description of the connections to the jack............................................................... 313

14.22.5 PCB considerations................................................................................................. 314

14.23 Analog characteristics......................................................................................................... 315

14.23.1 Line input to audio ADC path................................................................................... 315

14.23.2 Audio DAC to headphone output path..................................................................... 316

14.23.3 Audio DAC to mono line output path....................................................................... 318

14.23.4 Line input to headphone output path (analog bypass)............................................ 318

14.23.5 Micbias and reference............................................................................................. 320

Section 4 Memory Interface

15 DDR Controller............................................................................. 322

15.1 Overview............................................................................................................................. 322

15.1.1 Supported DDR SDRAM Types .................................................................................. 322

15.1.2 Block Diagram............................................................................................................. 322

15.2 Register Description............................................................................................................ 323

15.2.1 DSTATUS .................................................................................................................... 325

15.2.2 DCFG .......................................................................................................................... 326

15.2.3 DCTRL......................................................................................................................... 328

15.2.4 DLMR .......................................................................................................................... 331

15.2.5 DTIMING1,2,3,4,5,6 (DDR Timing Configure Register).............................................. 333

15.2.6 DREFCNT (DDR Auto-Refresh Counter).................................................................... 336

15.2.7 DMMAP0,1 (DDR Memory Map Configure Register) ................................................. 337

15.2.8 DDLP (DDR DFI low power handshake control register)............................................ 338

15.2.9 DREMAP1,2,3,4,5 (DDR Address Remapping Register 1,2,3,4,5) ............................ 339

15.2.10 WCMDCTRL1 (Performance wcmd reorder & grouping)........................................ 340

15.2.11 RCMDCTRL0 (Performance rcmd request control) ................................................ 341

15.2.12 RCMDCTRL1 (Performance rcmd request control) ................................................ 343

15.2.13 WDATTHD0 (performance wcmd request control).................................................. 343

CONTENTS

xii

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

15.2.14 WDATTHD1 (performance wcmd request control) ..................................................344

15.2.15 IPORTPRI (performance priority control).................................................................344

15.2.16 CHQOS0,1,2,3,4,5 (performance QoS control).......................................................346

15.2.17 CPM_DRCG.............................................................................................................347

15.3 Functional Description.........................................................................................................347

15.3.1 DDRC and DDR2 Memory Initialization Sequence .....................................................347

15.4 Change Clock Frequency....................................................................................................348

15.4.1 Manually SELF-REFRESH Mode................................................................................348

15.4.2 CPM driven SELF-REFRESH Mode............................................................................348

15.4.3 DLL bypass mode........................................................................................................349

15.5 Data Endian.........................................................................................................................349

15.6 DDR Connection Diagrams.................................................................................................349

15.6.1 Connection to one 512Mb x16 DDR2 device ..............................................................349

15.6.2 Connection to two 512Mb x16 DDR2 devices.............................................................350

16 External NAND Memory Controller................................................351

16.1 Overview..............................................................................................................................351

16.2 Pin Description ....................................................................................................................351

16.3 Physical Address Space Map..............................................................................................352

16.4 Static Memory Interface.......................................................................................................355

16.4.1 Register Description ....................................................................................................355

16.4.2 Example of Connection................................................................................................360

16.4.3 Basic Interface.............................................................................................................361

16.4.4 Burst ROM Interface....................................................................................................364

16.5 NAND Flash Interface .........................................................................................................365

16.5.1 Register Description ....................................................................................................365

16.5.2 NAND Flash Boot Loader ............................................................................................381

16.5.3 NAND Flash Operation................................................................................................382

16.5.4 Example of Toggle NAND Flash Access......................................................................383

17 BCH Controller..............................................................................385

17.1 Overview..............................................................................................................................385

17.2 Register Description............................................................................................................387

17.2.1 BCH Control Register (BHCR).....................................................................................387

17.2.2 BCH Control Set Register (BHCSR)............................................................................388

17.2.3 BCH Control Clear Register (BHCCR) ........................................................................389

17.2.4 BCH ENC/DEC Count Register (BHCNT)...................................................................389

17.2.5 BCH Data Register (BHDR).........................................................................................390

17.2.6 BCH Parity Register (BHPARn, n=0, 1, 2, 3, 4, 5…26, 27) .........................................390

17.2.7 BCH Error Report Register (BHERRn, n=0,1,2,3,4,5,6,7,…,61,62,63) .......................391

17.2.8 BCH Interrupt Status Register (BHINT).......................................................................392

17.2.9 BCH Interrupt Enable Set Register (BHINTES)...........................................................394

17.2.10 BCH Interrupt Enable Clear Register (BHINTEC) ...................................................394

CONTENTS

xiii

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

17.2.11 BCH Interrupt Enable Register (BHINTE)............................................................... 395

17.2.12 BCH User TAG OUTPUT Register (BHTO)............................................................. 396

17.3 BCH Operation.................................................................................................................... 396

17.3.1 Encoding Sequence .................................................................................................... 396

17.3.2 Decoding Sequence.................................................................................................... 398

Section 5 System Functions

18 Clock Reset and Power Controller................................................ 401

18.1 Overview............................................................................................................................. 401

18.1.1 CGU Block Diagram.................................................................................................... 402

18.1.2 CGU Registers ............................................................................................................ 404

18.1.3 PLL Operation ............................................................................................................. 440

18.1.4 Main Clock Division Change Sequence...................................................................... 441

18.2 Power Manager................................................................................................................... 441

18.2.1 Low-Power Modes and Function................................................................................. 441

18.2.2 Register Description.................................................................................................... 442

18.2.3 Doze Mode.................................................................................................................. 455

18.2.4 IDLE Mode .................................................................................................................. 456

18.2.5 SLEEP Mode............................................................................................................... 456

18.2.6 Power Down Mode...................................................................................................... 456

18.3 Reset Control Module......................................................................................................... 457

18.3.1 Register Description.................................................................................................... 457

18.3.2 Power On Reset.......................................................................................................... 458

18.3.3 WDT Reset.................................................................................................................. 458

19 Timer/Counter Unit ....................................................................... 459

19.1 Overview............................................................................................................................. 459

19.2 Pin Description.................................................................................................................... 459

19.3 Register Description............................................................................................................ 459

19.3.1 Timer Control Register (TCSR)................................................................................... 461

19.3.2 Timer Data FULL Register (TDFR).............................................................................. 463

19.3.3 Timer Data HALF Register (TDHR)............................................................................. 464

19.3.4 Timer Counter (TCNT)................................................................................................. 464

19.3.5 Timer Counter Enable Register (TER)........................................................................ 464

19.3.6 Timer Counter Enable Set Register (TESR) ............................................................... 465

19.3.7 Timer Counter Enable Clear Register (TECR)............................................................ 466

19.3.8 Timer Flag Register (TFR) .......................................................................................... 467

19.3.9 Timer Flag Set Register (TFSR).................................................................................. 468

19.3.10 Timer Flag Clear Register (TFCR) .......................................................................... 469

19.3.11 Timer Mast Register (TMR)..................................................................................... 470

19.3.12 Timer Mask Set Register (TMSR) ........................................................................... 471

19.3.13 Timer Mask Clear Register (TMCR)........................................................................ 471

CONTENTS

xiv

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

19.3.14 Timer Stop Register (TSR).......................................................................................472

19.3.15 Timer Stop Set Register (TSSR)..............................................................................473

19.3.16 Timer Stop Clear Register (TSCR) ..........................................................................474

19.3.17 Timer Status Register (TSTR)..................................................................................475

19.3.18 Timer Status Set Register (TSTSR).........................................................................476

19.3.19 Timer Status Clear Register (TSTCR) .....................................................................476

19.3.20 Timer control mode Register (TCUMOD) ................................................................477

19.3.21 Timer fifo write data (TFWD)....................................................................................478

19.3.22 Timer fifo state Register (TFIFOSR)........................................................................478

19.4 Operation.............................................................................................................................479

19.4.1 Basic Operation in TCU1 Mode...................................................................................479

19.4.2 Disable and Shutdown Operation in TCU1 Mode........................................................479

19.4.3 Basic Operation in TCU2 Mode...................................................................................479

19.4.4 Disable and Shutdown Operation in TCU2 Mode........................................................480

19.4.5 Read Counter in TCU2 Mode ......................................................................................480

19.4.6 Pulse Width Modulator (PWM) ....................................................................................481

19.4.7 Trackball Input Waveform Detect.................................................................................481

19.4.8 Basic Operation in FIFO Mode 1.................................................................................482

19.4.9 Basic Operation in FIFO Mode 2.................................................................................482

20 Operating System Timer................................................................484

20.1 Overview..............................................................................................................................484

20.2 Register Description............................................................................................................485

20.2.1 Operating System Control Register (OSTCSR) ..........................................................485

20.2.2 Operating System Timer Data Register (OSTDR).......................................................486

20.2.3 Operating System Timer Counter (OSTCNTH, OSTCNTL) ........................................487

20.2.4 Operating System Timer Counter high 32 bits buffer (OSTCNTHBUF) ......................487

20.3 Operation.............................................................................................................................487

20.3.1 Basic Operation ...........................................................................................................487

20.3.2 Disable and Shutdown Operation................................................................................488

21 Interrupt Controller........................................................................489

21.1 Overview..............................................................................................................................489

21.2 Register Description............................................................................................................489

21.2.1 Interrupt Controller Source Register (ICSR0)..............................................................490

21.2.2 Interrupt Controller Source Register (ICSR1)..............................................................490

21.2.3 Interrupt Controller Mask Register (ICMR0)................................................................490

21.2.4 Interrupt Controller Mask Register (ICMR1)................................................................491

21.2.5 Interrupt Controller Mask Set Register (ICMSR0) .......................................................491

21.2.6 Interrupt Controller Mask Set Register (ICMSR1) .......................................................492

21.2.7 Interrupt Controller Mask Clear Register (ICMCR0)....................................................492

21.2.8 Interrupt Controller Mask Clear Register (ICMCR1)....................................................492

21.2.9 Interrupt Controller Pending Register (ICPR0)............................................................493

CONTENTS

xv

JZ4780 Mobile Application Processor Cores/Systems Programming Manual

Copyright © 2005-2013 Ingenic Semiconductor Co., Ltd. All rights reserved.

21.2.10 Interrupt Controller Pending Register (ICPR1)........................................................ 493

21.2.11 Interrupt Source Register0 for PDMA (DSR0)......................................................... 494

21.2.12 Interrupt Mask Register0 for PDMA (DMR0)........................................................... 494

21.2.13 Interrupt Pending Register0 for PDMA (DPR0)....................................................... 494

21.2.14 Interrupt Source Register1 to PDMA (DSR1).......................................................... 495

21.2.15 Interrupt Mask Register1 for PDMA (DMR1)........................................................... 495

21.2.16 Interrupt Pending Register1 for PDMA (DPR1)....................................................... 496

21.3 Software Considerations..................................................................................................... 496

22 Watchdog Timer ........................................................................... 498

22.1 Overview............................................................................................................................. 498

22.2 Register Description............................................................................................................ 498

22.2.1 Watchdog Control Register (TCSR)............................................................................ 498

22.2.2 Watchdog Enable Register (TCER) ............................................................................ 499

22.2.3 Watchdog Timer Data Register (TDR) ........................................................................ 500

22.2.4 Watchdog Timer Counter (TCNT) ............................................................................... 500

22.3 Watchdog Timer Function................................................................................................... 500

23 PDMA Controller........................................................................... 502

23.1 Features.............................................................................................................................. 502