Intel I7-900 DEKSTOP SPECIFICATION User manual

Other Intel Computer Hardware manuals

Intel

Intel SRCZCR - RAID Controller Storage User manual

Intel

Intel Core 2 Duo Processor User manual

Intel

Intel BX80619I73820 Guide

Intel

Intel 12Gb/s User manual

Intel

Intel 80302 Technical manual

Intel

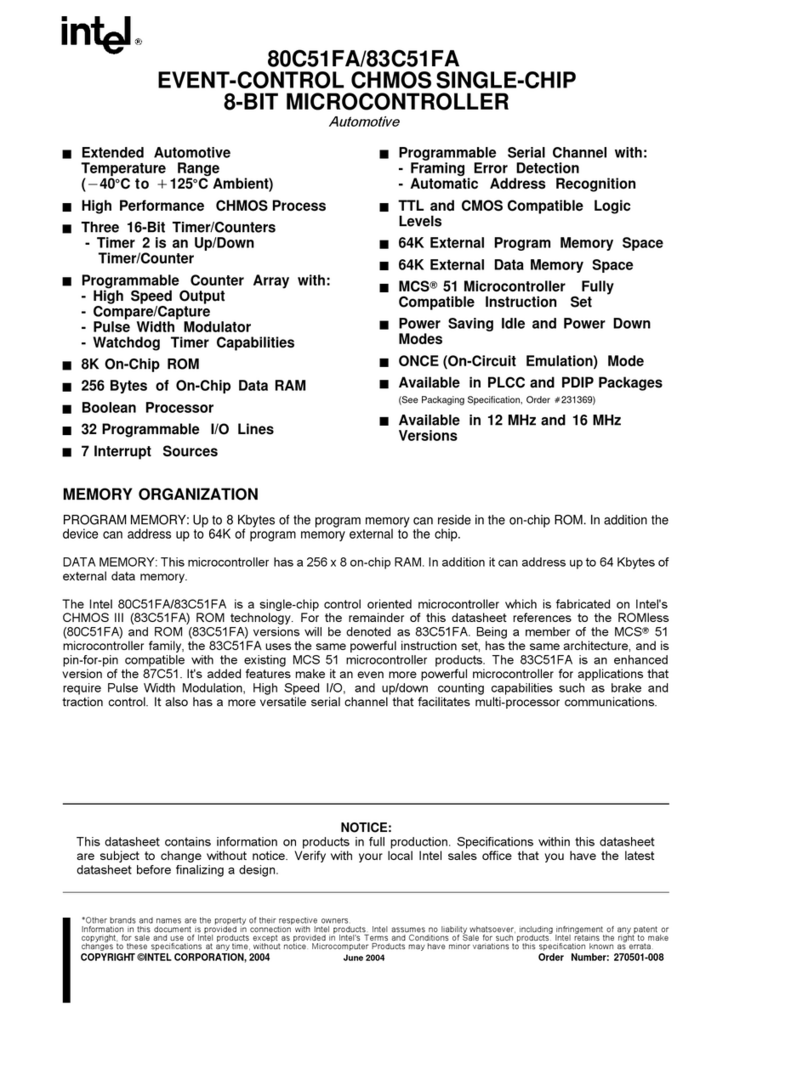

Intel 80C51FA User manual

Intel

Intel SRCMR - RAID Controller User manual

Intel

Intel 81342 User manual

Intel

Intel CORE 2 DUO E4000 - 3-2008 User manual

Intel

Intel AXXRMS2LL040 Installation manual

Intel

Intel SASWT4I Installation manual

Intel

Intel DG45ID - CARACTERISTIQUES TECHNIQUES Configuration guide

Intel

Intel 80C186XL User manual

Intel

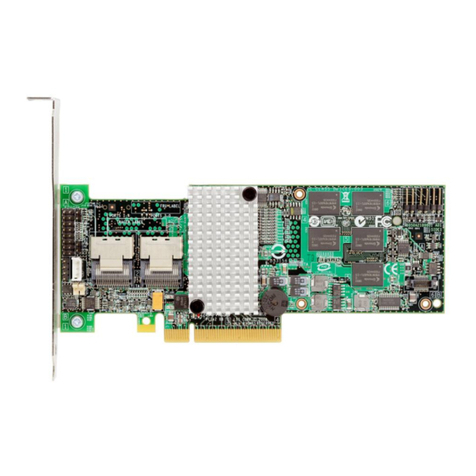

Intel RMS25CB080 Setup guide

Intel

Intel UPI- 41A User manual

Intel

Intel IXP2400 User manual

Intel

Intel 440GX Guide

Intel

Intel Core Duo Mobile 945GM User manual

Intel

Intel LGA1155 SOCKET - THERMAL MECHANICAL S AND DESIGN GUIDELINES... User manual

Intel

Intel 925 - Pentium D 925 3.0GHz 800MHz 4MB-Cache Socket 775... User manual

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual