viii

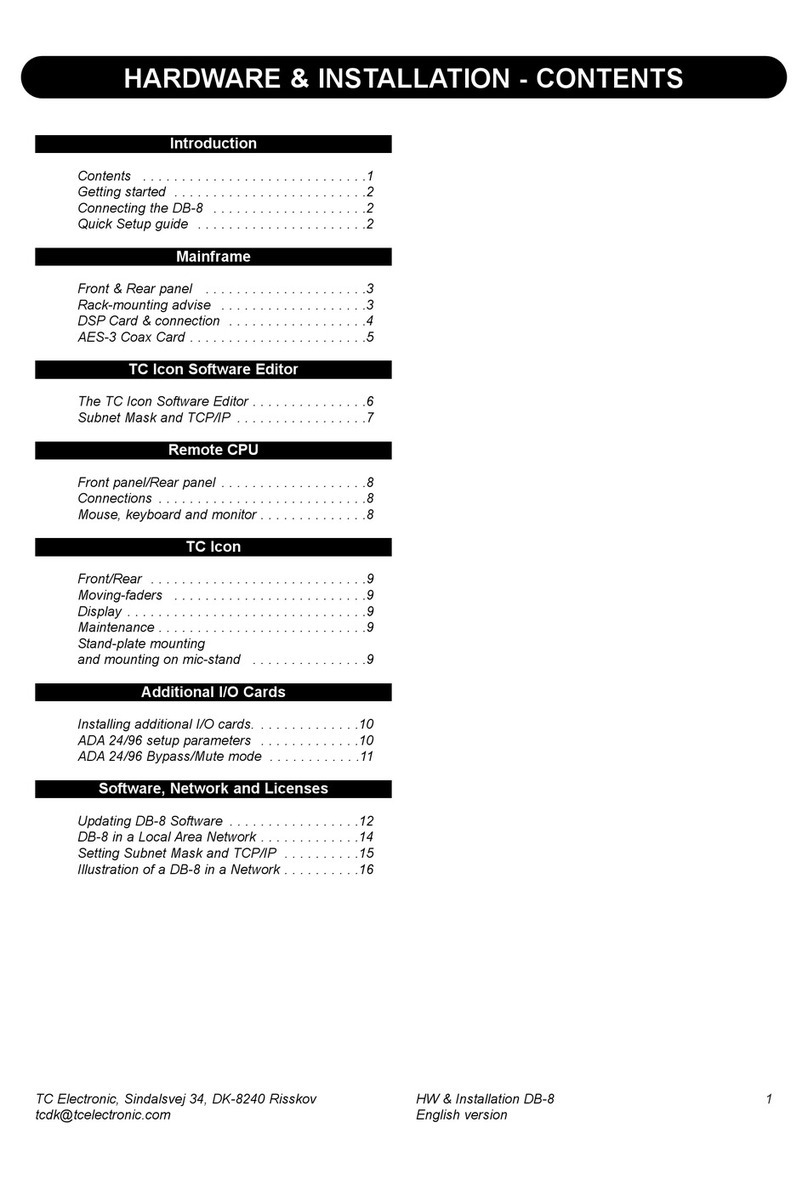

TABLE OF CONTENTS MOTOROLA

Table of Contents (Continued)

Paragraph Page

Number Title Number

SYNCHRONOUS SERIAL INTERFACE (SSI0 and SSI1)

8.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.2 SSI OPERATING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.3 SSI CLOCK AND FRAME SYNC GENERATION . . . . . . . . . . . . . . . . . 8-4

8.4 SSIx DATA AND CONTROL PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

8.4.1 Serial Transmit Data Pin - STDx . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.4.2 Serial Receive Data Pin - SRDx . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.4.3 Serial Clock - SCK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.4.4 Serial Control - SC1x . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.4.5 Serial Control - SC0x . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

8.5 SSI RESET AND INITIALIZATION PROCEDURE . . . . . . . . . . . . . . . . 8-8

8.6 SSIx INTERFACE PROGRAMMING MODEL . . . . . . . . . . . . . . . . . . . . 8-9

8.7 SSI TRANSMIT SHIFT REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-10

8.8 SSI TRANSMIT DATA REGISTER (TX) . . . . . . . . . . . . . . . . . . . . . . . . 8-12

8.9 SSI RECEIVE SHIFT REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-12

8.10 SSI RECEIVE DATA REGISTER (RX) . . . . . . . . . . . . . . . . . . . . . . . . . 8-12

8.11 SSI CONTROL REGISTER A (CRA) . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-12

8.11.1 CRA Prescale Modulus Select (PM0…PM7) Bits 0-7 . . . . . . . . . . . 8-13

8.11.2 CRA Frame Rate Divider Control (DC0…DC4) Bits 8-12 . . . . . . . . 8-13

8.11.3 CRA Word Length Control (WL0,WL1) Bits 13, 14 . . . . . . . . . . . . . 8-14

8.11.4 CRA Prescaler Range (PSR) Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . . 8-15

8.12 SSI CONTROL REGISTER B (CRB) . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-15

8.12.1 CRB Serial Output Flag 0 and 1 (OF0, OF1) Bit 0, 1 . . . . . . . . . . . . 8-16

8.12.2 Transmit and Receive Frame Sync Directions - (FSD0, FSD1) Bit 2,4 8-16

8.12.3 CRB A/Mu Law Selection Bit (A/MU) Bit 3 . . . . . . . . . . . . . . . . . . . . 8-17

8.12.4 Transmit and Receive Frame Sync Directions - (FSD1) Bit 4 . . . . . 8-17

8.12.5 CRB Clock Source Direction (SCKD) Bit 5 . . . . . . . . . . . . . . . . . . . . 8-17

8.12.6 CRB Clock Polarity Bit (SCKP) Bit 6 . . . . . . . . . . . . . . . . . . . . . . . . 8-17

8.12.7 CRB MSB Position Bit (SHFD) Bit 7 . . . . . . . . . . . . . . . . . . . . . . . . . 8-17

8.12.8 CRB Frame Sync Length (FSL) Bit 8 . . . . . . . . . . . . . . . . . . . . . . . . 8-17

8.12.9 CRB Frame Sync Invert (FSI) Bit 9 . . . . . . . . . . . . . . . . . . . . . . . . . 8-17

8.12.10 CRB Sync/Async (SYN) Bit 10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-18

8.12.11 CRB SSI Mode Select (MOD) Bit 11 . . . . . . . . . . . . . . . . . . . . . . . . 8-18