MOTOROLA DSP56309UM/D vii

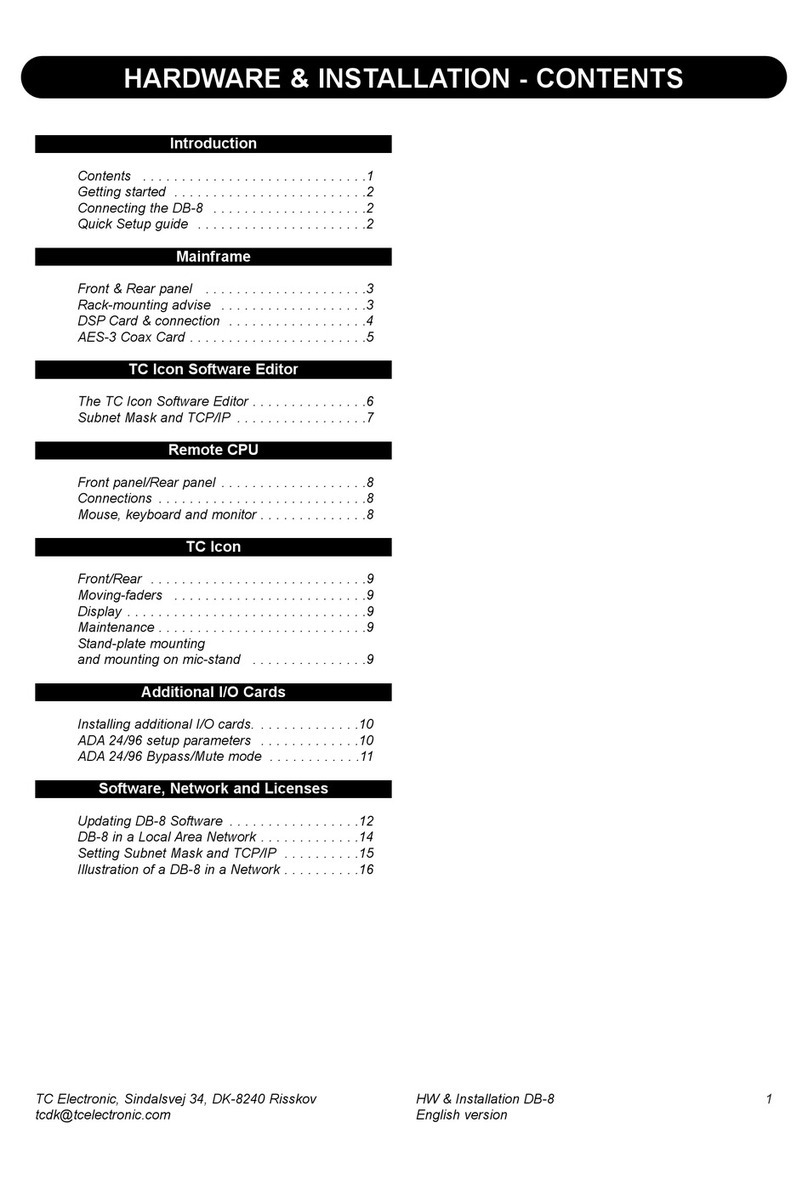

6.5.6.9 HPCR Host Request Open Drain (HROD) Bit 8 . . . . . 6-14

6.5.6.10 HPCR Host Data Strobe Polarity (HDSP) Bit 9. . . . . . 6-14

6.5.6.11 HPCR Host Address Strobe Polarity (HASP) Bit 10 . . 6-15

6.5.6.12 HPCR Host Multiplexed Bus (HMUX) Bit 11 . . . . . . . . 6-15

6.5.6.13 HPCR Host Dual Data Strobe (HDDS) Bit 12 . . . . . . . 6-15

6.5.6.14 HPCR Host Chip Select Polarity (HCSP) Bit 13 . . . . . 6-16

6.5.6.15 HPCR Host Request Polarity (HRP) Bit 14 . . . . . . . . . 6-16

6.5.6.16 HPCR Host Acknowledge Polarity (HAP) Bit 15 . . . . . 6-16

6.5.7 Host Data Direction Register (HDDR) . . . . . . . . . . . . . . . 6-17

6.5.8 Host Data Register (HDR) . . . . . . . . . . . . . . . . . . . . . . . . 6-17

6.5.9 DSP Side Registers After Reset . . . . . . . . . . . . . . . . . . . 6-18

6.5.10 Host Interface DSP Core Interrupts . . . . . . . . . . . . . . . . . 6-19

6.6 HI08-EXTERNAL HOST PROGRAMMERÕS MODEL . . . . . 6-20

6.6.1 Interface Control Register (ICR) . . . . . . . . . . . . . . . . . . . 6-22

6.6.1.1 ICR Receive Request Enable (RREQ) Bit 0 . . . . . . . . 6-23

6.6.1.2 ICR Transmit Request Enable (TREQ) Bit 1. . . . . . . . 6-23

6.6.1.3 ICR Double Host Request (HDRQ) Bit 2. . . . . . . . . . . 6-23

6.6.1.4 ICR Host Flag 0 (HF0) Bit 3 . . . . . . . . . . . . . . . . . . . . 6-24

6.6.1.5 ICR Host Flag 1 (HF1) Bit 4 . . . . . . . . . . . . . . . . . . . . 6-24

6.6.1.6 ICR Host Little Endian (HLEND) Bit 5 . . . . . . . . . . . . . 6-24

6.6.1.7 ICR Reserved Bit 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-24

6.6.1.8 ICR Initialize Bit (INIT) Bit 7 . . . . . . . . . . . . . . . . . . . . 6-24

6.6.2 Command Vector Register (CVR) . . . . . . . . . . . . . . . . . . 6-25

6.6.2.1 CVR Host Vector (HV[6:0]) Bits 0Ð6 . . . . . . . . . . . . . . 6-25

6.6.2.2 CVR Host Command Bit (HC) Bit 7. . . . . . . . . . . . . . . 6-26

6.6.3 Interface Status Register (ISR) . . . . . . . . . . . . . . . . . . . . 6-26

6.6.3.1 ISR Receive Data Register Full (RXDF) Bit 0 . . . . . . . 6-26

6.6.3.2 ISR Transmit Data Register Empty (TXDE) Bit 1 . . . . 6-27

6.6.3.3 ISR Transmitter Ready (TRDY) Bit 2 . . . . . . . . . . . . . 6-27

6.6.3.4 ISR Host Flag 2 (HF2) Bit 3 . . . . . . . . . . . . . . . . . . . . 6-27

6.6.3.5 ISR Host Flag 3 (HF3) Bit 4 . . . . . . . . . . . . . . . . . . . . 6-27

6.6.3.6 ISR Reserved Bits 5, 6 . . . . . . . . . . . . . . . . . . . . . . . . 6-27

6.6.3.7 ISR Host Request (HREQ) Bit 7 . . . . . . . . . . . . . . . . . 6-27

6.6.4 Interrupt Vector Register (IVR) . . . . . . . . . . . . . . . . . . . . 6-28

6.6.5 Receive Byte Registers (RXH: RXM: RXL) . . . . . . . . . . . 6-28

6.6.6 Transmit Byte Registers (TXH:TXM:TXL) . . . . . . . . . . . . 6-29