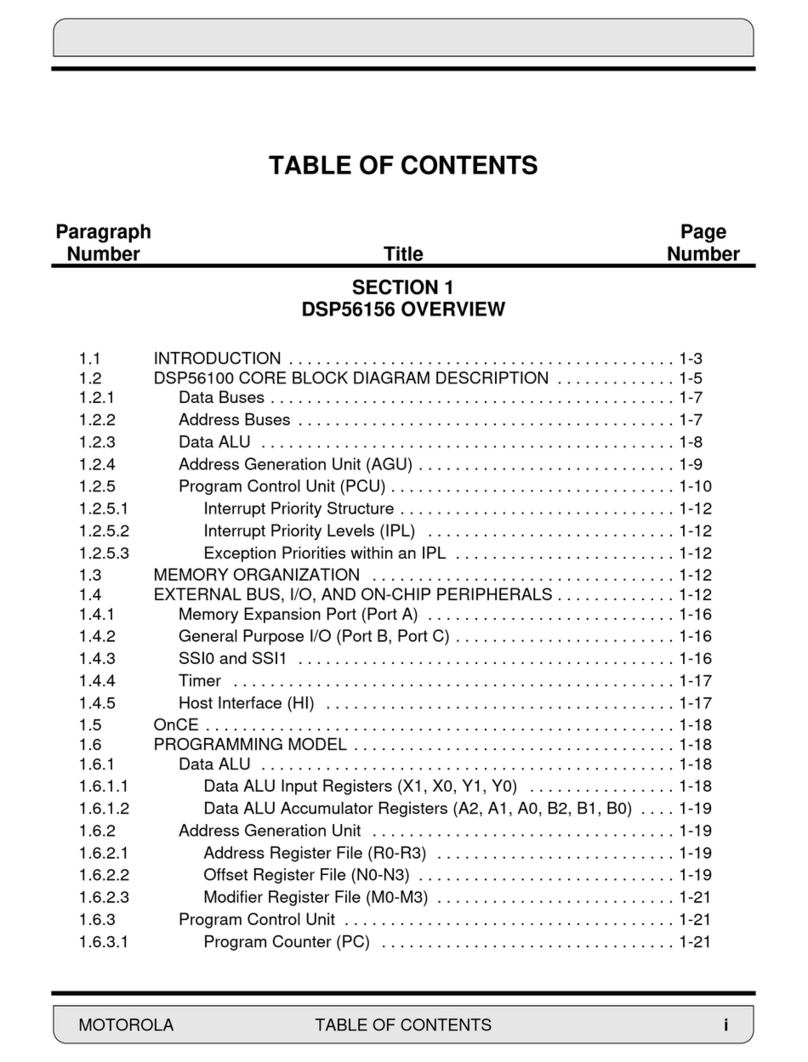

viii DSP56303 User’s Manual

6.6.6 Host Port Control Register (HPCR)..................................................................................... 6-18

6.6.7 Host Transmit (HTX) Register ............................................................................................ 6-21

6.6.8 Host Receive (HRX) Register.............................................................................................. 6-22

6.6.9 DSP-Side Registers After Reset ..........................................................................................6-22

6.7 Host Programmer Model .....................................................................................................6-23

6.7.1 Interface Control Register (ICR) ......................................................................................... 6-24

6.7.2 Command Vector Register (CVR)....................................................................................... 6-26

6.7.3 Interface Status Register (ISR) ............................................................................................6-27

6.7.4 Interrupt Vector Register (IVR)...........................................................................................6-29

6.7.5 Receive Data Registers (RXH:RXM:RXL)......................................................................... 6-30

6.7.6 Transmit Data Registers (TXH:TXM:TXL)........................................................................6-30

6.7.7 Host-Side Registers After Reset .......................................................................................... 6-31

6.8 Programming Model Quick Reference................................................................................ 6-32

Chapter 7

Enhanced Synchronous Serial Interface (ESSI)

7.1 ESSI Enhancements............................................................................................................... 7-2

7.2 ESSI Data and Control Signals..............................................................................................7-3

7.2.1 Serial Transmit Data Signal (STD)........................................................................................ 7-3

7.2.2 Serial Receive Data Signal (SRD)......................................................................................... 7-3

7.2.3 Serial Clock (SCK)................................................................................................................7-3

7.2.4 Serial Control Signal (SC0)................................................................................................... 7-4

7.2.5 Serial Control Signal (SC1)................................................................................................... 7-4

7.2.6 Serial Control Signal (SC2)................................................................................................... 7-6

7.3 Operation ............................................................................................................................... 7-6

7.3.1 ESSI After Reset....................................................................................................................7-6

7.3.2 Initialization........................................................................................................................... 7-6

7.3.3 Exceptions.............................................................................................................................. 7-7

7.4 Operating Modes: Normal, Network, and On-Demand....................................................... 7-10

7.4.1 Normal/Network/On-Demand Mode Selection................................................................... 7-10

7.4.2 Synchronous/Asynchronous Operating Modes ...................................................................7-11

7.4.3 Frame Sync Selection .......................................................................................................... 7-11

7.4.4 Frame Sync Signal Format ..................................................................................................7-11

7.4.5 Frame Sync Length for Multiple Devices............................................................................ 7-12

7.4.6 Word Length Frame Sync and Data Word Timing.............................................................. 7-12

7.4.7 Frame Sync Polarity............................................................................................................. 7-12

7.4.8 Byte Format (LSB/MSB) for the Transmitter...................................................................... 7-13

7.4.9 Flags..................................................................................................................................... 7-13

7.5 ESSI Programming Model...................................................................................................7-14

7.5.1 ESSI Control Register A (CRA).......................................................................................... 7-14

7.5.2 ESSI Control Register B (CRB) .......................................................................................... 7-18

7.5.3 ESSI Status Register (SSISR).............................................................................................. 7-28

7.5.4 ESSI Receive Shift Register ................................................................................................7-29

7.5.5 ESSI Receive Data Register (RX) ....................................................................................... 7-30

7.5.6 ESSI Transmit Shift Registers.............................................................................................7-30