©National Instruments Corporation 7 NI sbRIO-960x OEM Instructions and Specifications

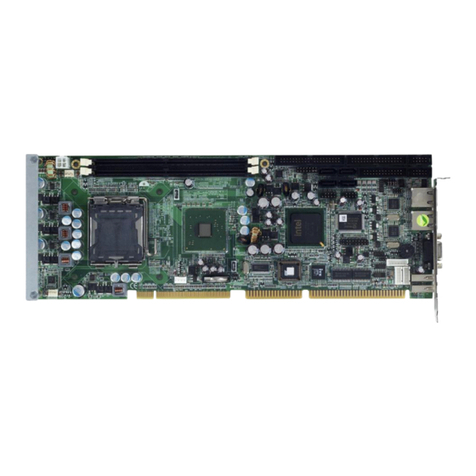

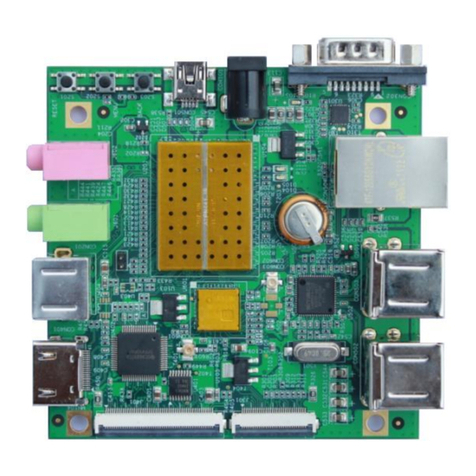

Figure 5 shows the dimensions of the front of the NI sbRIO-960x.

Figure 5. NI sbRIO-960x Front Dimensions in Millimeters (Inches)

Note For more information about the dimensions of the NI sbRIO-960x, including

detailed dimensional drawings, go to ni.com/dimensions.

Maximum Component Heights

The primary side of the NI sbRIO-960x is the top side of the PCB where

the power connector and Ethernet connector are populated. The maximum

component height on the primary side of the PCB is split into two regions,

with the maximum component height of 17.27 mm (0.680 in.) on the front

edge and 4.06 mm (0.160 in.) on the remaining primary side. The

maximum component height on the secondary side of the PCB is 6.15 mm

(0.242 in.), excluding the RIO Mezzanine Card (RMC) Connector.

NI recommends that adjacent PCBs and surfaces observe a minimum

keepaway distance of 19.05 mm (0.75 in.) from the primary-side surface

and 7.62 mm (0.360 in.) from the secondary-side surface. For more

information refer to Figure 6, Figure 7, and Figure 8.

1 Minimum Clearance for Latch on Mating Power Connector

2 Maximum Height of RIO Mezzanine Card Components

3 4-40 threads, Maximum Torque of 3.6 in.-lbs

0 (.000)

Ø 3(.118)

18.16 (.715)

16 (.630)

6.16 (.242)

0 (.000)

2.16 (.085)

5.34 (.210)

2.54 (.100)

5.08(.200)

7.62 (.300)

10.16 (.400)

33.8(1.331)

49.93(1.966)

57.51 (2.264)

70.01 (2.756)

89.81 (3.536)

95.21 (3.748)

8.76 (.345)

3.66 (.144)

6.32 (.249)

6.15 (.242)

19.48(.767)

76.84 (3.025)

4x Ø 2.8(.071)

1

2

3