Platform Adaptation and Bring-Up

Jetson Nano Platform Adaptation and Bring-Up Guide DA_09361-002 | iii

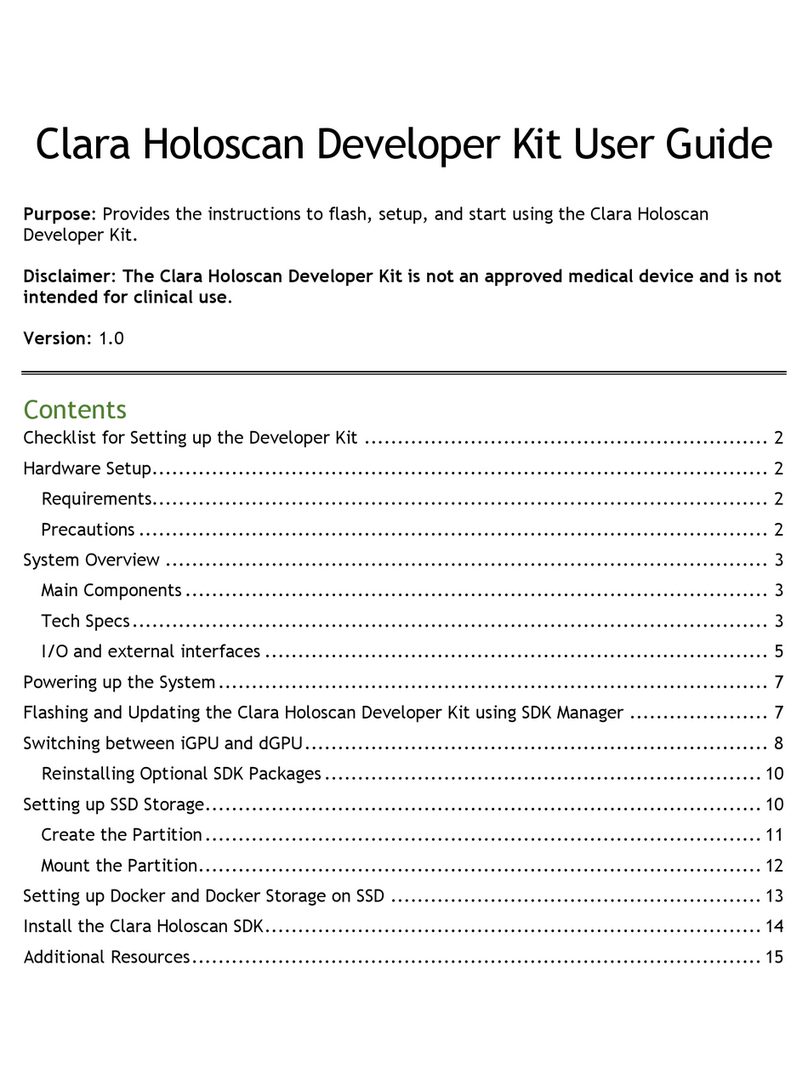

Table of Contents

Platform Adaptation and Bring-Up.................................................1

Board Configuration............................................................................. 1

Board Naming.................................................................................... 2

Placeholders in the Porting Instructions...................................................... 2

Root Filesystem Configuration................................................................. 3

Pinmux Changes................................................................................. 3

Exporting Pinmux for U-Boot .................................................................. 4

Accessing GPIOs via “gpio” Device Labels ................................................... 6

Exporting Pinmux for the L4T Linux Kernel.................................................. 6

Porting U-Boot................................................................................... 6

Porting the Linux Kernel........................................................................ 7

Porting USB ...................................................................................... 9

USB Structure................................................................................. 9

UPHY Lane Assignment...................................................................... 9

Required Device Tree Changes............................................................12

For a Host-Only Port..................................................................... 12

For an OTG (On-The-Go) Port..........................................................16

Fan speed control mapping table ............................................................25

Other Considerations When Porting ......................................................... 26

Boot Time Reduction...........................................................................26

Root Filesystem..............................................................................26

Kernel .........................................................................................27

Hardware Bring-Up Checklist .................................................................27

Before Power-On ............................................................................28

Initial Power-On .............................................................................28

Initial Software Flashing....................................................................28

Power .........................................................................................29

Power Optimization ......................................................................... 29

USB 2.0 PHY .................................................................................29

USB 3.0 .......................................................................................30

HDMI..........................................................................................30

Audio..........................................................................................30

UART..........................................................................................30

SD Card (SDMMC1) .........................................................................31

Fan ............................................................................................31

Sensors I2C: General .......................................................................31

Sensors I2C: Touch Screen (Optional)....................................................31