SPI interface loop-back demo on a single RT Box

1 Overview

The Serial Peripheral Interface (SPI) is a synchronous serial communication interface specification

used for short-distance communication, primarily with peripheral devices. SPI devices communicate

in full duplex mode using a master-slave architecture between a single master and multiple slaves.

The SPI Master block from the RT Box Target Support Library implements SPI communication via

digital outputs/inputs. There are 2 SPI modules available on the RT Box. Each SPI module can output

data on up to 4 paralleled data channels (using a common clock and chip select signal).

This demo model shows:

• a simple loop-back scenario that wires the SPI module digital output channel with the digital input

channel,

• how to configure the parameters inside the SPI Master block,

• SPI transmission within a single or multiple RT Box model steps.

One additional model shows the use case of the RT Box as SPI Master connected to an external ADC

device as the SPI slave. This additional model is explained in Appendix, and can be accessed by open-

ing the demo model folder.

1.1 Requirements

• One PLECS RT Box and one PLECS Coder license.

• The RT Box Target Support Package (minimum version 2.1.1).

• Follow the step-by-step instructions on configuring PLECS and the RT Box in the Quick Start guide

of the RT Box User Manual.

• One wire to connect the digital output channel 2 and digital input channel 2 on the front panel of

the RT Box.

2 Model

This demo model uses the SPI Master data output and data input on the same SPI module inside the

same subsystem. With the wiring between the SPI Master data output and input channel, a loop-back

of the SPI data is formed.

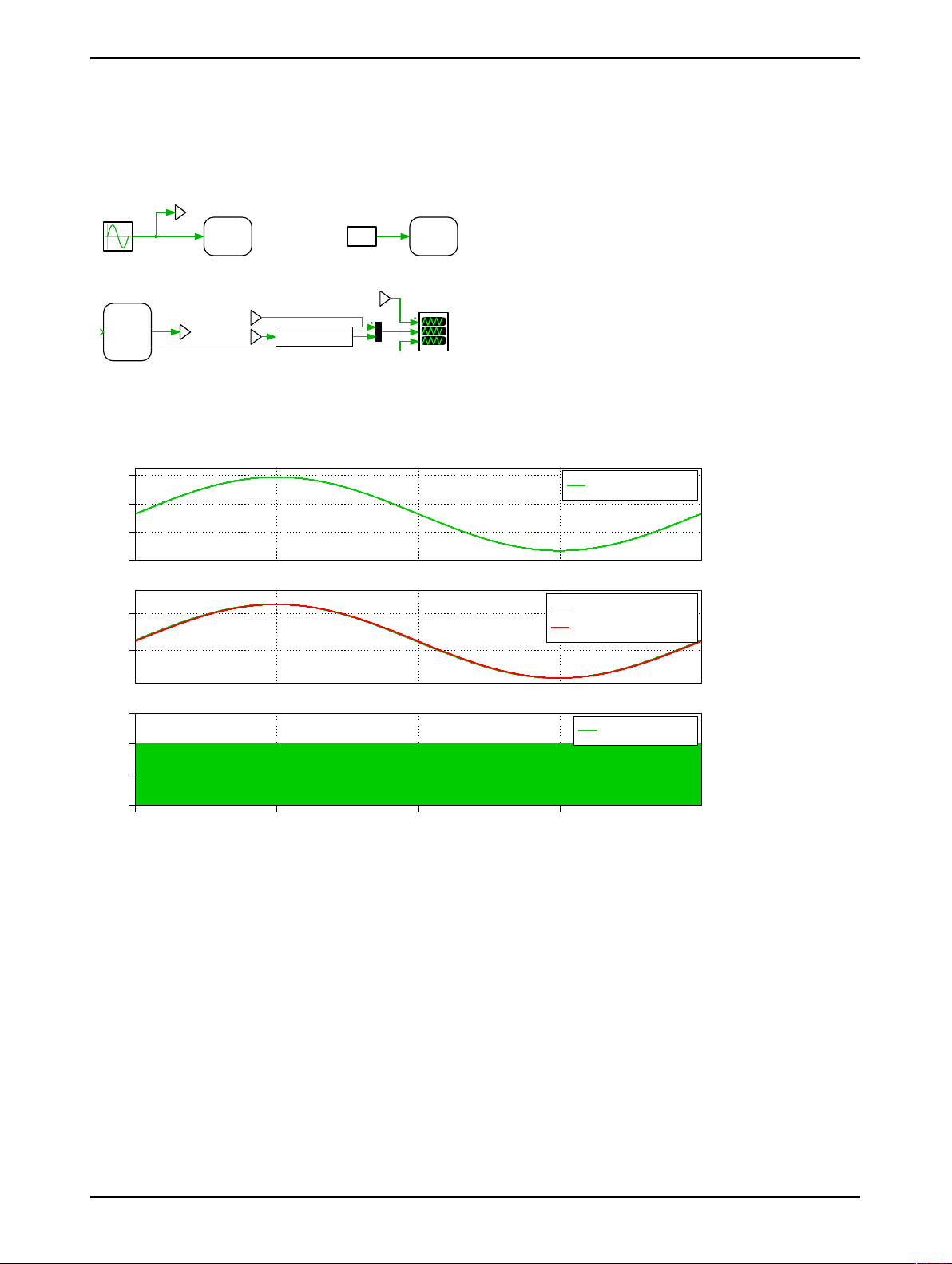

The circuit schematic is shown in Fig. 1. A Sine wave and a Pulse wave are packed into two 16-bit

words and transmitted out from the SPI Master data output channel. Through the loop-back wire, it

is received at the SPI Master data input channel, and then displayed in the Scope in Fig. 1 for com-

parison.

Figure 1: Subsystem circuit schematic for SPI loop-back demo

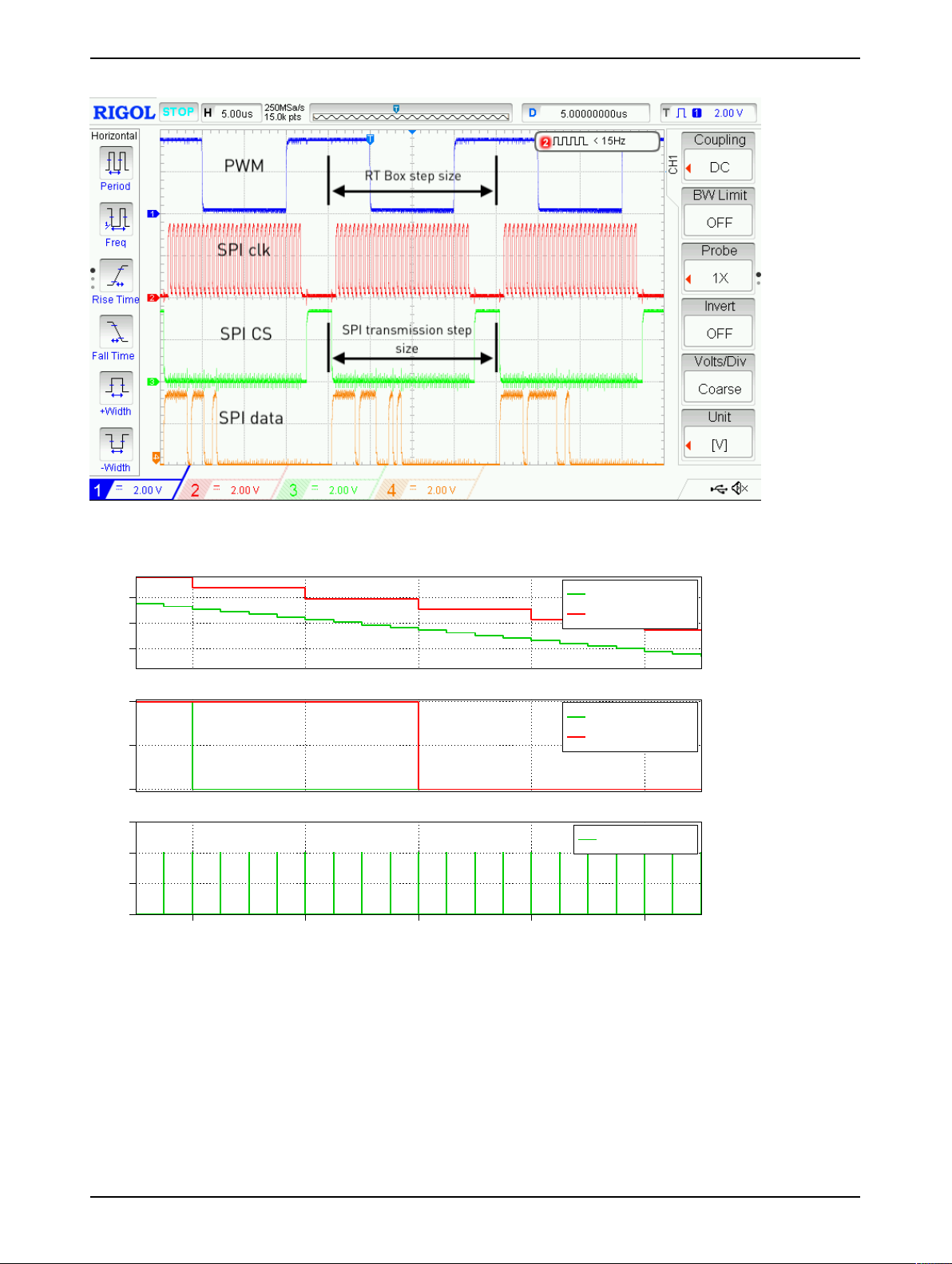

Additionally, a PWM Out block generates a PWM signal with 0.5 duty cycle synchronized with the RT

Box model step size by configuring its Synchronization with model step option as Enabled. This

PWM signal can be used as a reference to observe the different behaviors of SPI transmission within a

single or multiple RT Box model steps.

Fig. 2 shows the mask content of the SPI Master block. For the fields not mentioned in the following

explanation, please refer to the Help page of the SPI Master block.

www.plexim.com 1