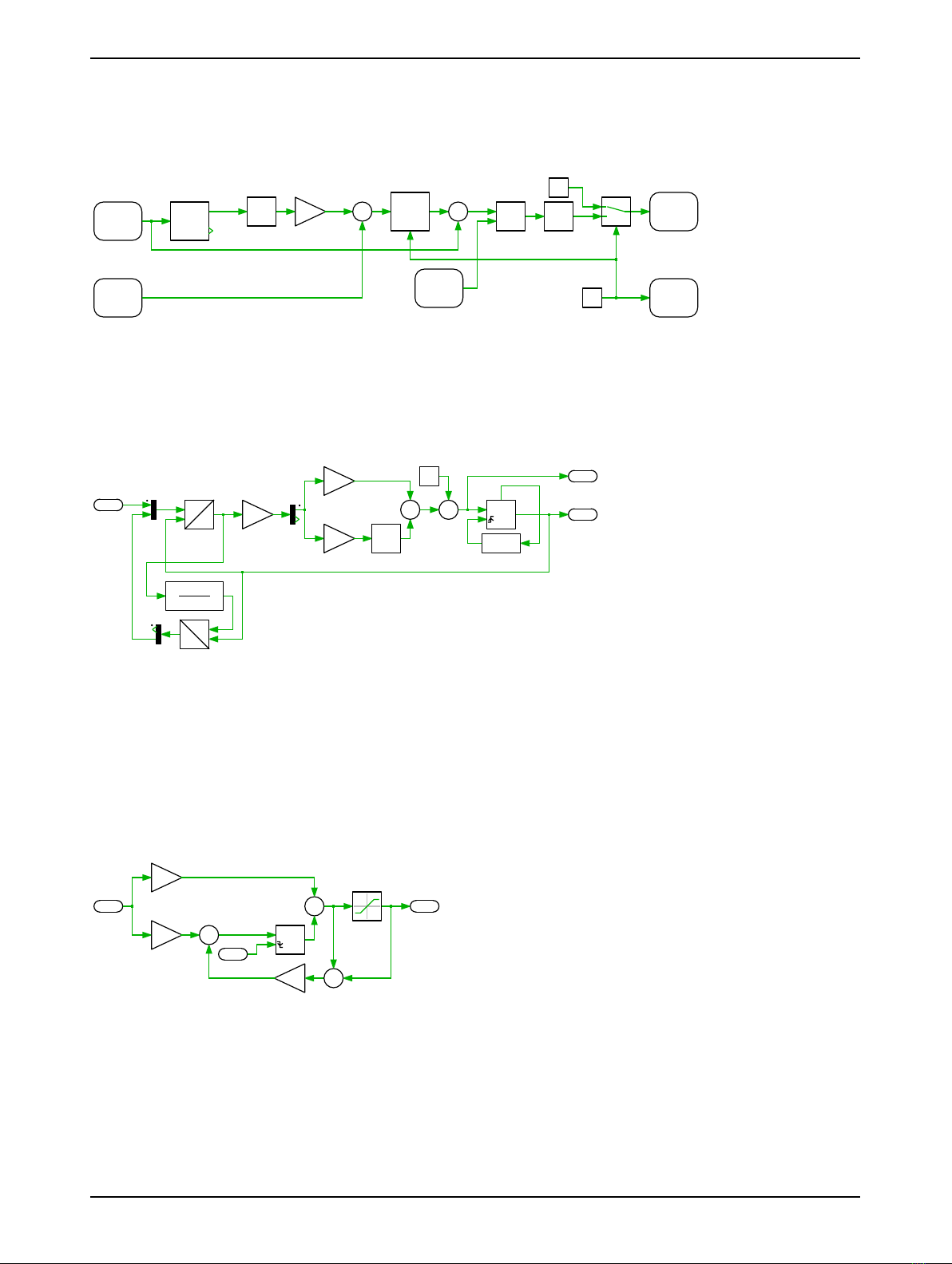

Single-Phase Inverter

1 Overview

This demo model features a single-phase grid-connected inverter operating at 50 kW and unity power

factor. This document describes the implementation of the power stage and controls using the PLECS

electrical and control domains.

The plant and the controller models are split into two distinct subsystems. The subsystem represent-

ing the plant is deployed on one RT Box and the subsystem representing the controller is deployed on

a second RT Box. The two RT Boxes are connected front-to-front in a virtual prototyping configuration

with two 37 pin Sub-D cables to exchange digital PWM signals and analog current measurements. Vir-

tual prototyping is a potential first step when developing real-time models for Hardware-in-the-loop

(HIL) or rapid control prototyping (RCP) applications.

The chosen discretization step sizes and average execution times for each subsystem in the single-

phase inverter model are shown in Tab. 1. Real-time execution on the RT Box requires the model to

execute using a fixed-step solver. The discretization step size parameter specifies the base sample

time of the generated code and is used to discretize the physical model and control domain state-space

equations. The execution time represents the actual time it takes to execute one discrete step of the

PLECS model on the RT Box hardware. The processor loading is the ratio of the execution time to the

discretization step size.

Table 1: Discretization step size and average execution time of real-time models with two RT Box 1

Subsystem Discretization Step Size Average Execution Time

Plant 2 µs1.05 µs

Controller 62.5 µs(fsw = 16 kHz) 1.1 µs

1.1 Requirements

To run this demo model, the following items are needed (available at www.plexim.com):

• Two PLECS RT Boxes and one PLECS and PLECS Coder license

• The RT Box Target Support Library

• Follow the step-by-step instructions on configuring PLECS and the RT Box in the Quick Start guide

of the RT Box User Manual.

• Two 37 pin Sub-D cables to connect the boxes front-to-front.

Note that this demo model is targeted at two RT Boxes application, with one running the Plant and

the other running the Controller. In this way, the execution time of each real-time target is minimized.

Besides, the setup can easily transition to a HIL or RCP test later on.

However if the user has only one RT Box available, please check the corresponding models targeted

for one RT Box application. In this case, two 37 pin Sub-D cables are still needed to connect in front

Analog Out interface with Analog In interface, and Digital Out interface with Digital In interface.

• For RT Box 2 and 3, by default the multi-tasking feature is enabled in this demo. “Controller” part

is circled with a Task frame block, and runs in one core. The rest of the circuit on the schematic be-

longs to the “Base task”, and runs in another core. In this way the computational effort is split onto

different cores. Please check the default setting under Scheduling tab of the Coder options... win-

dow.

• For RT Box 1, multi-tasking is disabled since there is only one CPU core available for calculating

the model, which includes both Plant and the Controller.

www.plexim.com 1