Modular Multilevel Converter

1 Overview

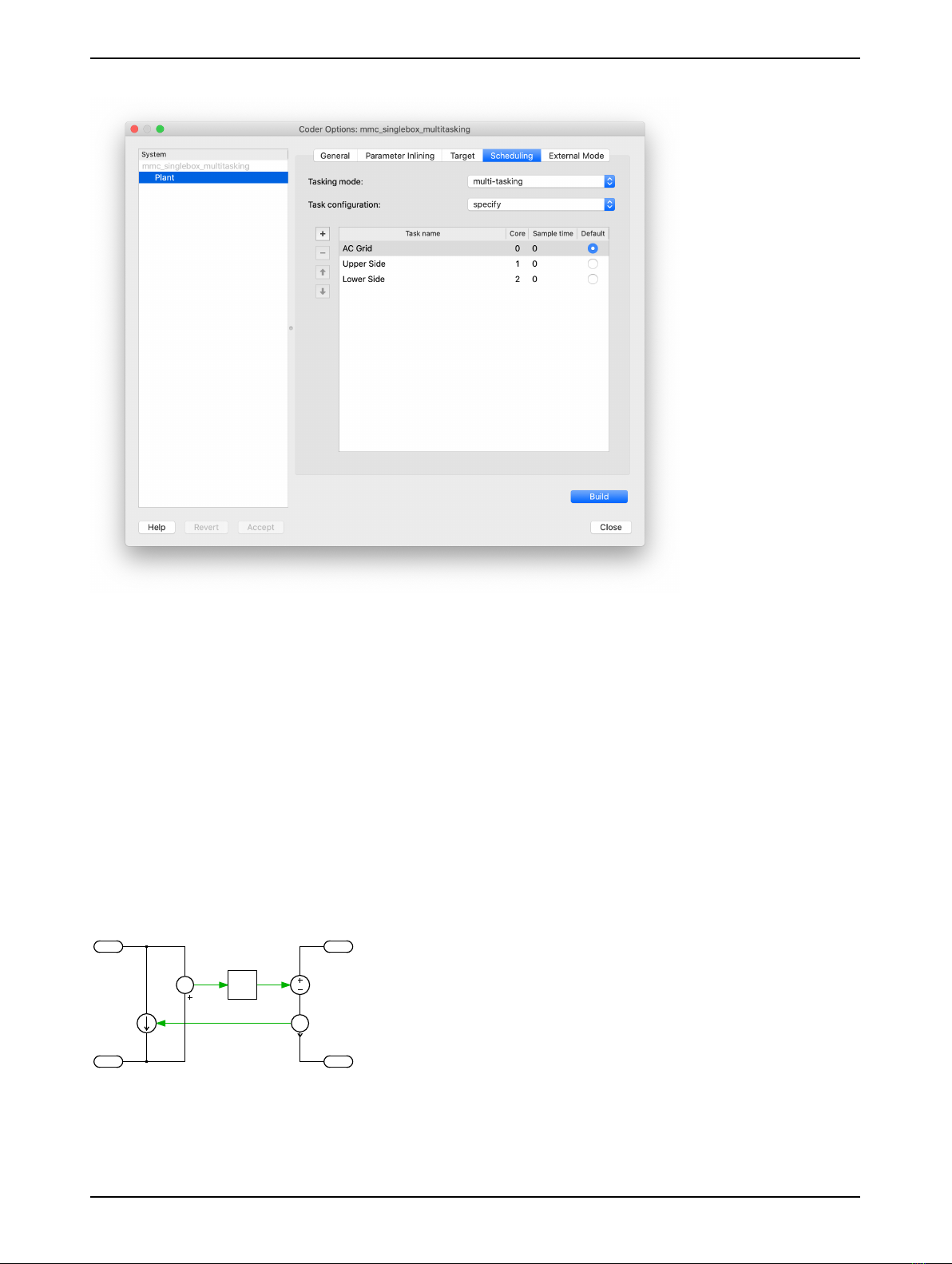

This RT Box demo model features a grid-connected modular multilevel converter (MMC) with open-

loop controls. The demo model can be simulated either in single-tasking or multi-tasking mode. To al-

low multi-tasking mode, the physical model has to be split into different parts. This can be done with

the Task Frame component from the PLECS library. This block associates the enclosed components

with a specified task in a multi-tasking environment. For real-time simulation on the RT Box 2 or RT

Box 3 each specified task is then executed on a different CPU core to reduce the overall discretization

step size. For the PLECS RT Box 1 only single-tasking mode is available. The chosen discretization

step size and average execution times for the two different tasking modes are shown in Tab. 1.

Table 1: Discretization step size and average execution time of real-time models with both tasking

modes for 5 submodules per arm on RT Box 2

Discretization Step Size Average Execution Time Single-Tasking Average Execution Time Multi-Tasking

6µs3.7 µs2.0 µs

1.1 Requirements

To run this demo model, the following items are needed (available at www.plexim.com):

• One PLECS RT Box 1, 2 or 3 and one PLECS Coder license

• One 37 pin Sub-D cable to connect the digital I/Os of the box front-to-front

• The RT Box Target Support Library

• Follow the step-by-step instructions on configuring PLECS and the RT Box in the Quick Start guide

of the RT Box User Manual.

Note This model contains model initialization commands that are accessible from:

PLECS Standalone: The menu Simulation + Simulation Parameters... + Initializations

PLECS Blockset: Right click in the Simulink model window + Model Properties + Callbacks +

InitFcn*

2 Model

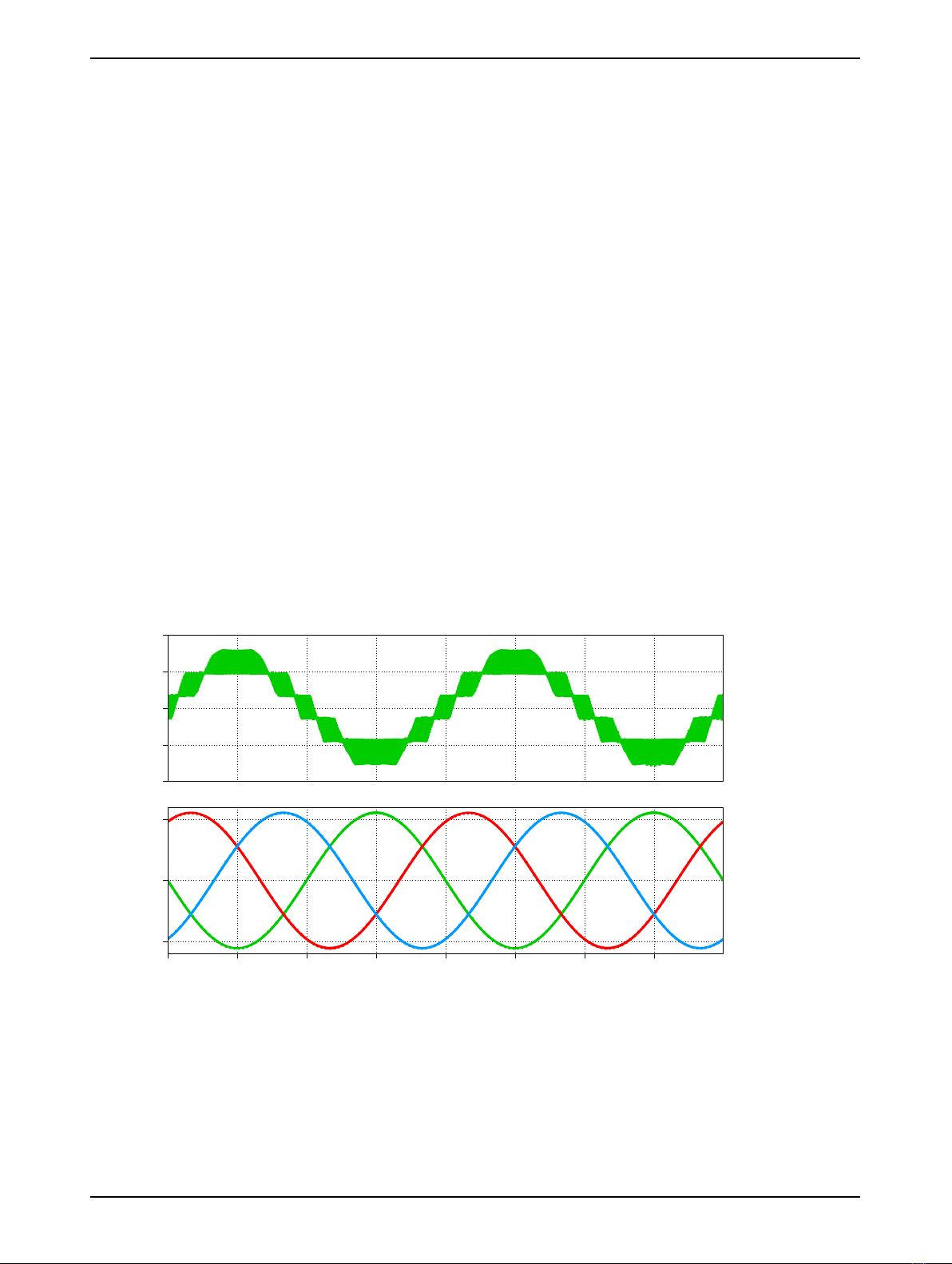

The top level schematic of the demo model is depicted in Fig. 1. Since the demo model runs in open-

loop, the PWM generation and the power circuit run on the same RT Box. To run the subsystem on

an RT Box, the subsystem has to be configured as atomic and enabled for code generation by right-

clicking on the subsystem and choosing Subsystem +Execution settings....

Plant+OpenloopControls

Figure 1: Top level schematic of MMC demo model

www.plexim.com 1