RTL8201(L)

2002-01-18 Rev.1.04

1

REALTEK SINGLE CHIP

SINGLE PORT 10/100MBPS

FAST ETHERNET PHYCEIVER

RTL8201(L)

1. Features........................................................................ 2

2. General Description .................................................... 2

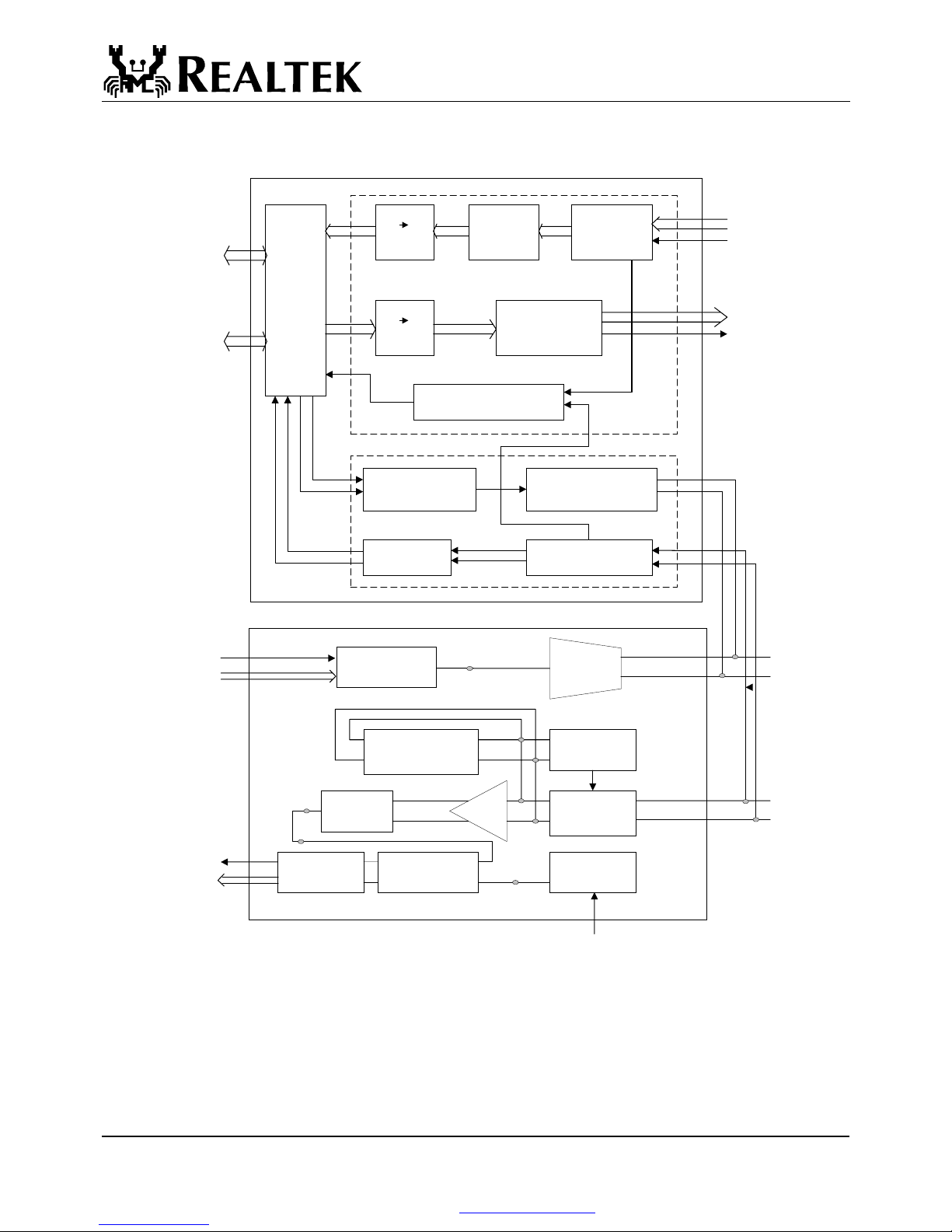

3. Block Diagram............................................................. 3

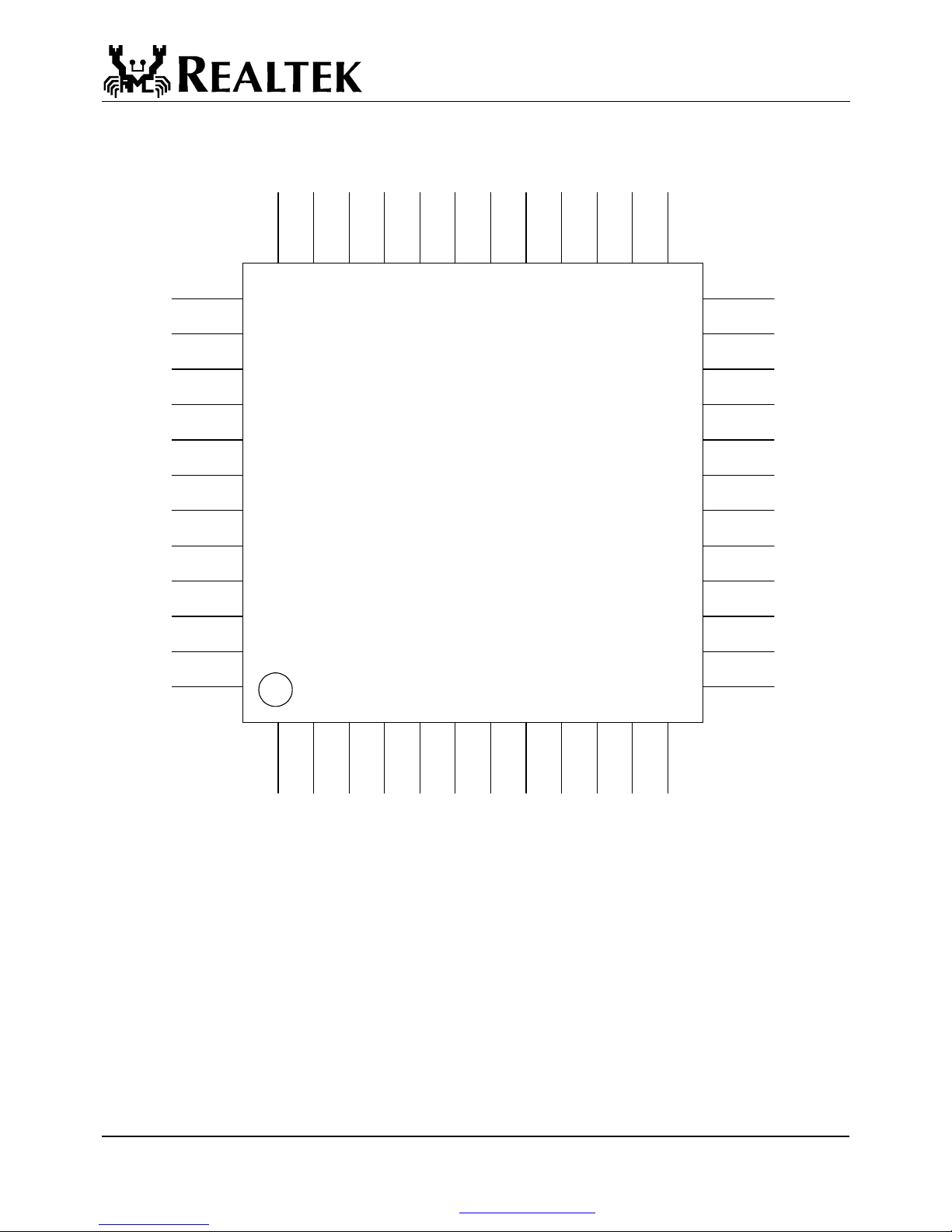

4. Pin Assignments .......................................................... 4

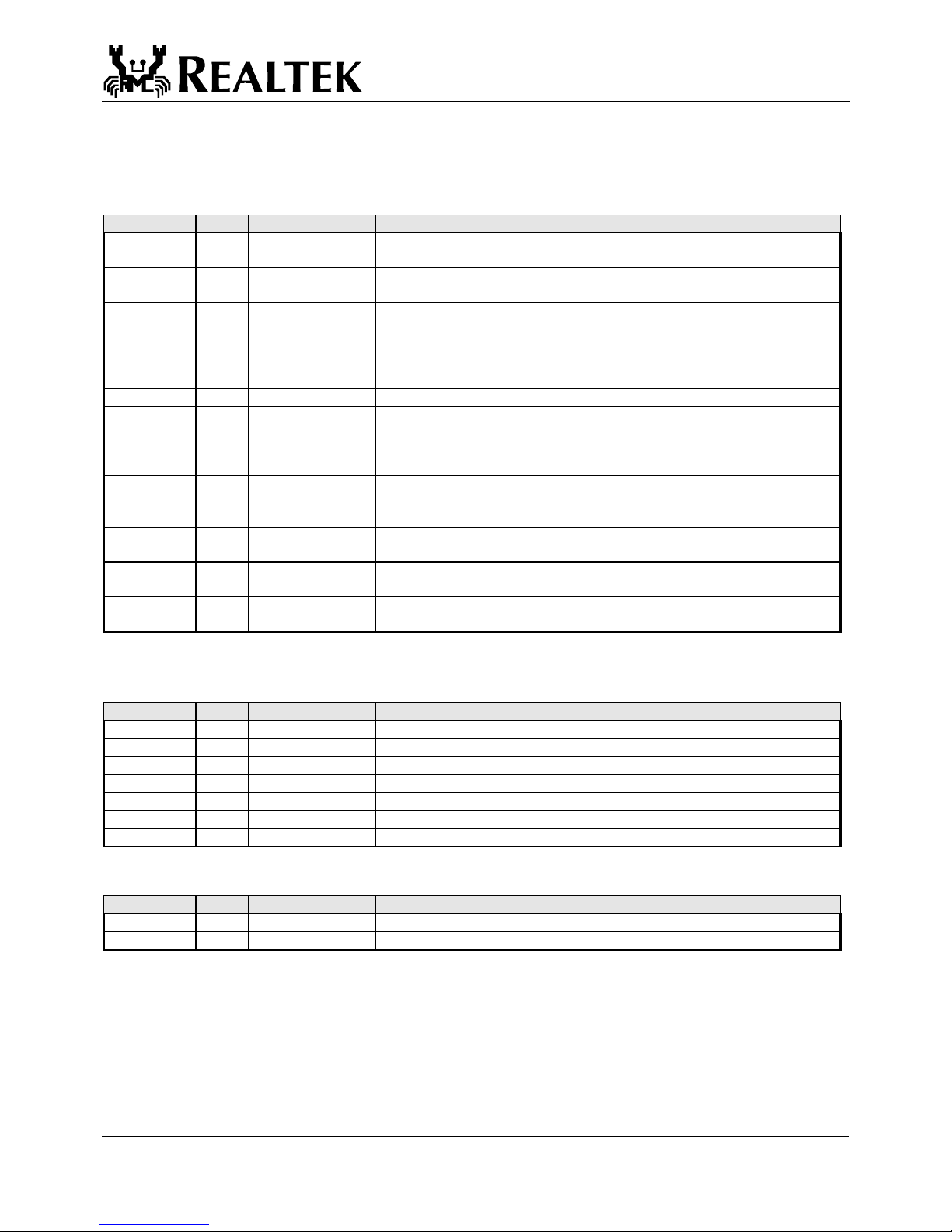

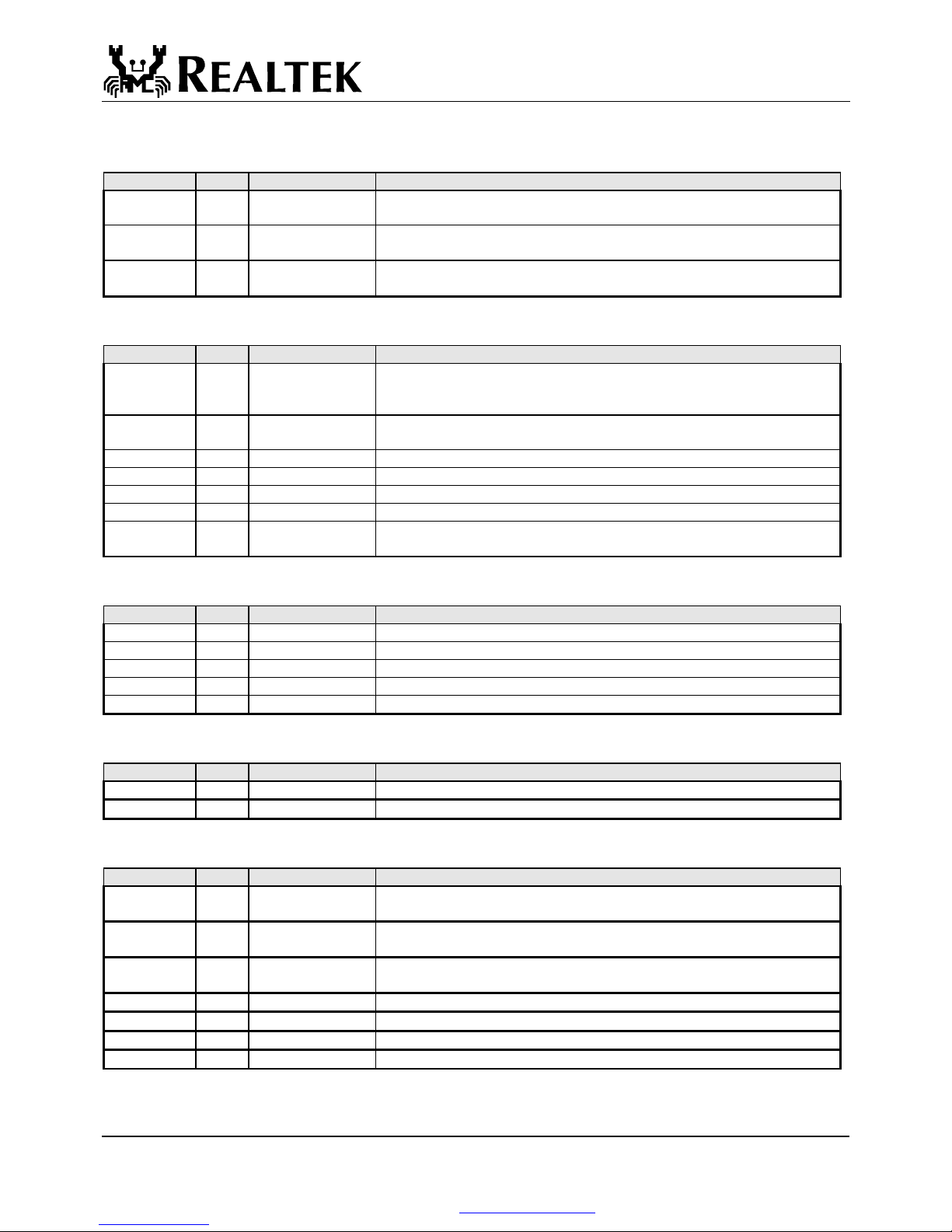

5. Pin Description ............................................................ 5

5.1 100 Mbps MII & PCS Interface ............................. 5

5.2 Serial Network Interface (SNI) .............................. 5

5.3 Clock Interface ....................................................... 5

5.4 100Mbps Network Interface................................... 6

5.5 Device Configuration Interface .............................. 6

5.6 LED Interface/PHY Address Config...................... 6

5.7 Reset and Test pins................................................. 6

5.8 Power and Ground pins.......................................... 6

6. Register Descriptions .................................................. 7

6.1 Register 0 Basic Mode Control .............................. 7

6.2 Register 1 Basic Mode Status................................. 9

6.3. Register 2 PHY Identifier 1................................. 10

6.4. Register 3 PHY Identifier 2................................. 10

6.5. Register 4 Auto-negotiation Advertisement................ 11

6.6 Register5Auto-NegotiationLinkPartnerAbility.................. 12

6.7 Register 6 Auto-negotiation Expansion (ANER) . 14

6.8 Register16NwaySetup(NSR)....................................... 14

6 . 9 Register 17 Loopback, Bypass, Receiver Error Mask (LBREMR).... 15

6.10 Register 18 RX_ER Counter (REC)................... 15

6.11 Register1910MbpsNetworkInterfaceConfiguration.......... 15

6.12 Register 20 PHY 1_1.......................................... 15

6.13 Register 21 PHY 1_2.......................................... 16

6.13 Register 22 PHY 2 ............................................. 16

6.14 Register 23 Twister_1 ........................................ 16

6.15 Register 24 Twister_2 ........................................ 16

7. Functional Description ............................................. 17

7.1 MII and Management Interface............................ 17

7.2 Auto-negotiation and Parallel Detection .............. 18

7.3 Flow control support ............................................ 18

7.4 Hardware Configuration and Auto-negotiation.............. 19

7.5 LED and PHY Address Configuration................. 20

7.6 Serial Network Interface ...................................... 20

7.7 Power Down, Link Down, Power Saving, and Isolation Modes 21

7.8 Media Interface .................................................... 21

7.8.1 100Base Tx/Rx ............................................. 21

7.8.2 10Base Tx/Rx ............................................... 22

7.9 Repeater Mode Operation .................................... 22

7.10 Reset, Power, and Transmit Bias........................ 22

8. Electrical Characteristics ......................................... 23

8.1 D.C. Characteristics ............................................. 23

8.1.1. Absolute Maximum Ratings........................ 23

8.1.2. Operating Conditions................................... 23

8.1.3. Power Dissipation........................................ 23

8.1.4 Supply Voltage: Vcc ..................................... 23

8.2 A.C. Characteristics ............................................. 24

8.2.1 Transmission Without Collision ................... 24

8.2.2 Reception Without Error............................... 24

9. Mechanical Dimensions ............................................ 25

Tel:

+49(0)234-9351135

·

Fax:

+49(0)234-9351137

E-MAIL:[email protected] http://www.cornelius-consult.de