AN1455 Rev. 2.00 Page 3 of 14

Jan 31, 2011

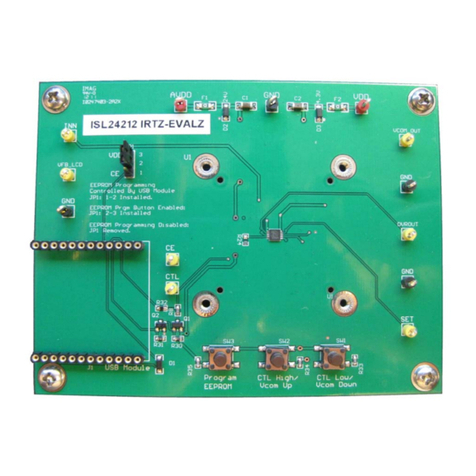

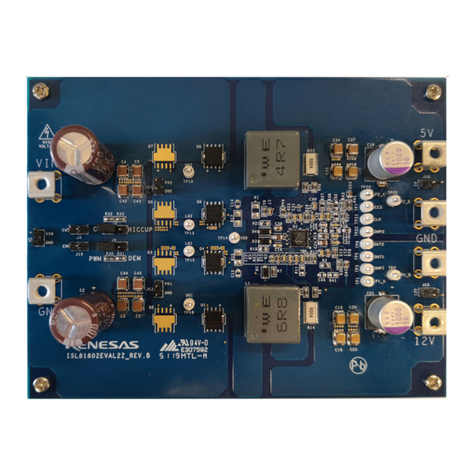

ISL34341KIT1Z, ISL76321ARZ-EVAL1Z

Nomenclature

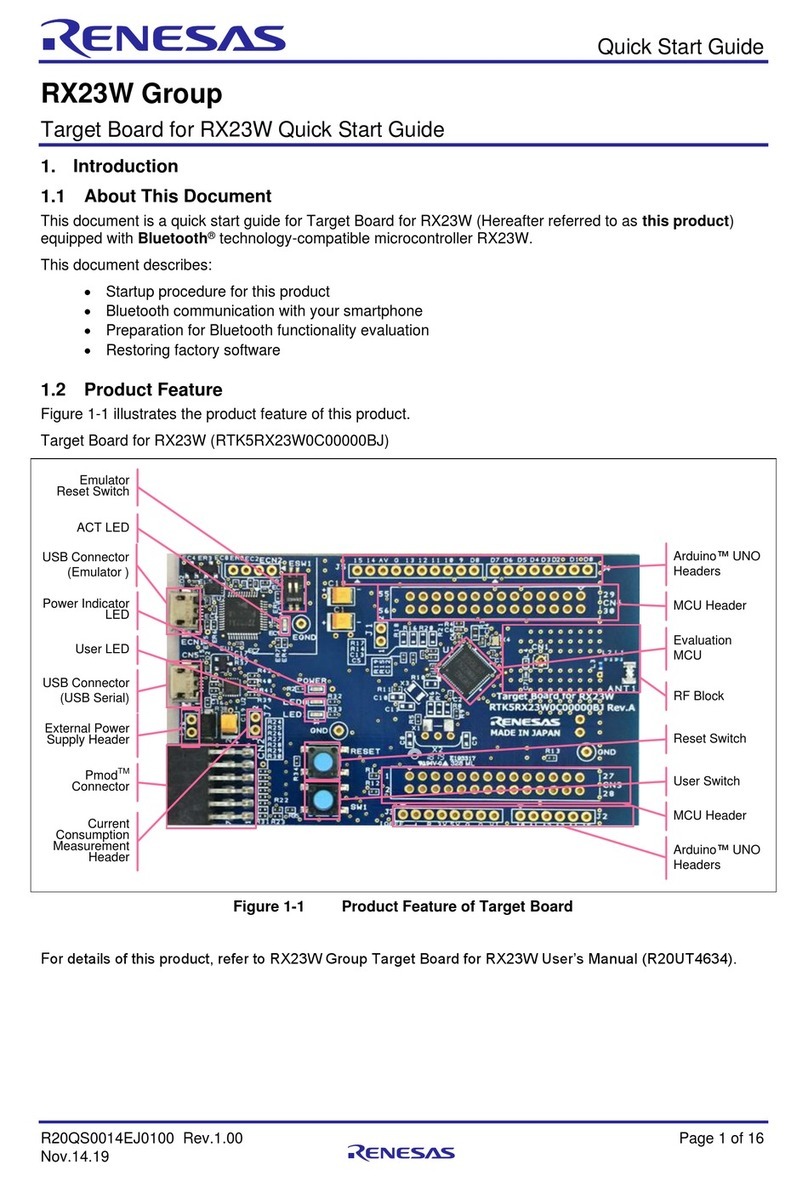

For user convenience, many connectors and switches on the

evaluation board are labeled with the device pin name. However,

occasions arise when we need to distinguish between the

connector and the device pin. The nomenclature in Table 1 is

adopted when specificity is needed.

The evaluation boards also have provisions for user

customization. Unless otherwise indicated, all discussion of

functions and settings assume the evaluation boards are in the

factory shipped state. Any reference to the ISL34340 should be

treated as the ISL34341. The ISL34340 is an older device that

has a subset of the ISL34341 functionality and is no longer

available.

Evaluation Kit Usage

The ISL34341 Evaluation Kit is designed to be flexible in order to

allow for examination of our chip in several different ways. The

ISL34341 device has built in patterns that can be activated

through I2C write to the appropriate register. There are built in

patterns that are designed for scoping the serial data as well as a

built in PRBS generator and detector. It should be noted that

these features are always available even in a completed system

for testing or debug.

The user also has the ability of injecting video of the same type

as the target application. By using these two methods, we believe

that evaluation of the ISL34341 can be done both quickly and

effectively.

USER SUPPLIED VIDEO SIGNALS

The serializer needs video of valid format to function and must

match the PCLK frequency of the ISL343xx device; see the device

datasheet for details. Such signals may be provided by either

attaching a raw RGB driver to J20 using a ribbon cable or by

driving VSYNC, HSYNC, and PCLK pins on J20 (not BNCs) using

additional function generators. If DATAEN is not supplied, it

needs to be strapped to VDD33. The BNC connectors on the

serializer board are sense “outputs” only (to hook up to scopes).

An LCD panel may be connected to J20 to view the deserializer

video output.

Video data is not required as the 8b/10b encoding will create the

necessary transitions for the link to operate properly. The side

channel and I2C master mode can both be evaluated in this

state.

TEST MODE SIGNALS

There are 4 built in test patterns that can be accessed by the user

through the I2C interface. Three patterns are fixed repeating

high, low and mixed frequency patterns. These are most useful

for direct observation on an oscilloscope through the SMAs at

either end of the cable. In addition, there is a build in PRBS

generator and PRBS detector. These can be conveniently used

together to evaluate different lengths or types qualities of cables

at different frequencies. This is initiated in the Tx chip in register

0x06. There is an 8-bit error counter that records PRBS errors

register 0x07, which is read from the Rx board. This register self

clears upon reading. “PRBS GUI Setups” on page 12 shows the

setups for the Tx and Rx chips for running the PRBS.

REQUIRED EQUIPMENT

1. 3.3V Power Supply, 1A – applied to the I2C hub

2. 50MHz function generator – supply PCLK_IN to both boards

3. Windows PC with USB– configure the device through the I2C bus

4. 500MHz oscilloscope– minimum for signal observation

TABLE 1. NOMENCLATURE

SHORTHAND REFERS TO: WHY SO SPECIFIC?

ser.PCLK_IN PCLK_IN device pin.

SerDes is in video serializer mode.

We are referring to the device pin specifically and not the

BNC connector. There are several paths on the EVB to the

device pin.

serEVB.PCLK_IN BNC connector labeled PCLK_IN.

SerDes is in video serializer mode.

This BNC is factory configured to be a sense output.

des.PCLK_IN PCLK_IN device pin.

SerDes is in video deserializer mode.

We are referring to the device pin specifically and not the

BNC connector. There are several paths on the EVB to the

device pin.

desEVB.PCLK_IN BNC connector labeled PCLK_IN.

SerDes is in video deserializer mode.

This BNC is factory configured to be a high impedance input.