Sharp PA-W1400 User manual

Other Sharp Computer Hardware manuals

Sharp

Sharp CE-E User manual

Sharp

Sharp JW-20FL5 User manual

Sharp

Sharp MZ1F10 User manual

Sharp

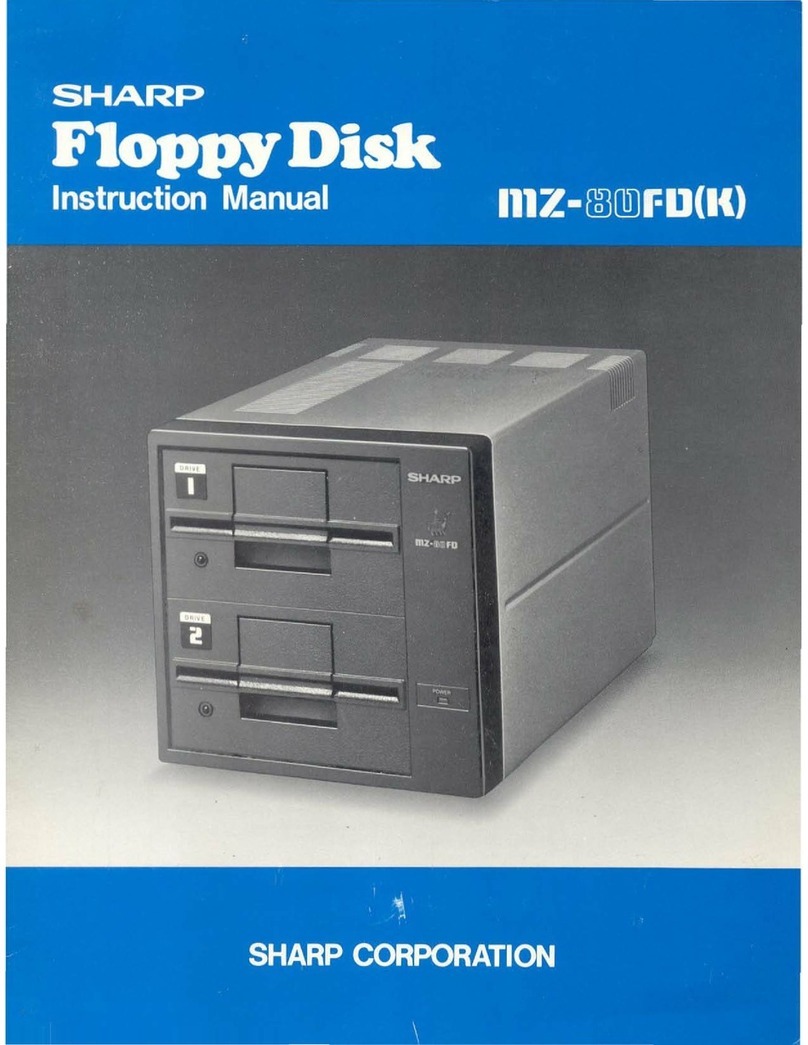

Sharp MZ-80FD(K) User manual

Sharp

Sharp MZ-801/0 User manual

Sharp

Sharp MZ1F10 User manual

Sharp

Sharp PN-ZB02 User manual

Sharp

Sharp AN-WC11B User manual

Sharp

Sharp MZ-8BI03 User manual

Sharp

Sharp CE-340R User manual

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual