SiFive E3* Core IP Series User manual

SiFive Core IP FPGA Eval Kit User Guide

v3p0

© SiFive, Inc.

2SiFive Core IP FPGA Eval Kit User Guide v3p0

SiFive Core IP FPGA Eval Kit User

Guide

Proprietary Notice

Copyright © 2016-2019, SiFive Inc. All rights reserved.

Information in this document is provided “as is”, with all faults.

SiFive expressly disclaims all warranties, representations and conditions of any kind, whether

express or implied, including, but not limited to, the implied warranties or conditions of

merchantability, fitness for a particular purpose and non-infringement.

SiFive does not assume any liability rising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation indirect, incidental, special,

exemplary, or consequential damages.

SiFive reserves the right to make changes without further notice to any products herein.

Release Information

Version Date Changes

v3p0 Feb 28, 2019 Updated for 19.02 Core IP Release

• Supports v19.02 Core IP Package

• Added descriptions for Arty-100T

• Added Chapters for E2, E3/S5, E7/S7 MCS

Images

v2p0 Feb 2, 2018 Updated to match v2p0 of the Evaluation MCS:

• FPGA Eval includes ITIM

• DTIM size increased to 64kiB

• Number of HWBP increased to 8

• Added User Mode Support

• Updated various links

v1p0 May 4, 2017 First release

i

ii SiFive Core IP FPGA Eval Kit User Guide v3p0

Contents

SiFive Core IP FPGA Eval Kit User Guide i

List of Figures v

1 Introduction 1

1.1 About this Document .................................. 1

1.2 About this Release ................................... 1

1.3 Evaluation Version Limitations ............................. 1

2 Required Hardware 3

2.1 Xilinx Arty A7 Artix-7 FPGA Evaluation Kit ...................... 3

2.2 USB A to Micro-B Cable ................................ 3

2.3 Olimex ARM-USB-TINY-H Debugger ......................... 3

2.4 USB A to B Cable .................................... 3

2.5 Male-To-Female Jumper Cables (10) ......................... 4

3 Board Setup 5

3.1 Connecting the USB Interface ............................. 5

3.2 Connecting the Debugger ............................... 5

4 FPGA Flash Programming File 9

4.1 Programming the Arty 35T SPI Flash ......................... 9

4.2 Programming the Arty 100T SPI Flash ........................ 10

5 Boot and Run 11

5.1 Serial Setup ....................................... 11

5.1.1 Reset and boot ................................ 13

5.1.2 Load a Program ............................... 13

iii

iv SiFive Core IP FPGA Eval Kit User Guide v3p0

5.2 Default Demo Program ................................. 13

5.2.1 Terminal Log ................................. 13

6 Software Development Flow 15

6.1 Supported Platforms .................................. 15

6.2 Software Development Using Freedom Studio IDE .................. 15

6.3 Software Development Using Freedom E SDK Command Line Tools ....... 15

6.3.1 Setting Up Freedom-E-SDK ......................... 16

6.3.2 Cloning the Repository ............................ 16

6.4 Freedom E SDK Arty BSP ............................... 17

6.5 Example Programs ................................... 17

6.6 Using the Freedom E SDK ............................... 18

6.6.1 Building an Example ............................. 18

6.6.2 Uploading to the Target Board ........................ 18

6.6.3 Debugging a Target Program ........................ 19

6.6.4 Cleaning a Target Program Build Directory ................. 19

6.6.5 Create a Standalone Project ......................... 19

7 E2 Core IP FPGA Eval Kit MCS Image Contents 21

7.1 Core IP FPGA Eval Kit Memory Map ......................... 21

7.2 Core IP FPGA Eval Kit Clock and Reset ....................... 21

7.3 Core IP FPGA Eval Kit Pinout ............................. 21

8 E3 / S5 Core IP FPGA Eval Kit MCS Image Contents 25

8.1 Core IP FPGA Eval Kit Memory Map ......................... 25

8.2 Core IP FPGA Eval Kit Clock and Reset ....................... 25

8.3 Core IP FPGA Eval Kit Pinout ............................. 25

9 E7 / S7 MCS Image Contents 29

9.1 Core IP FPGA Eval Kit Memory Map ......................... 29

9.2 Core IP FPGA Eval Kit Clock and Reset ....................... 29

9.3 Core IP FPGA Eval Kit Pinout ............................. 29

10 For More Information 33

List of Figures

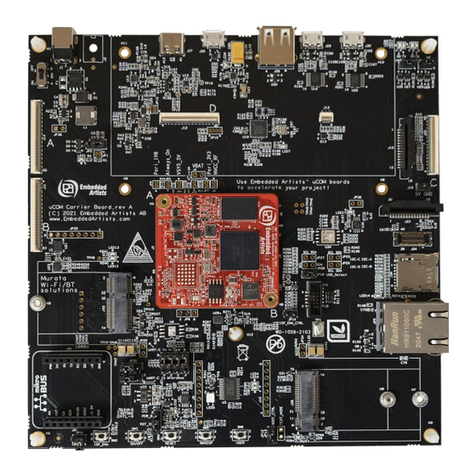

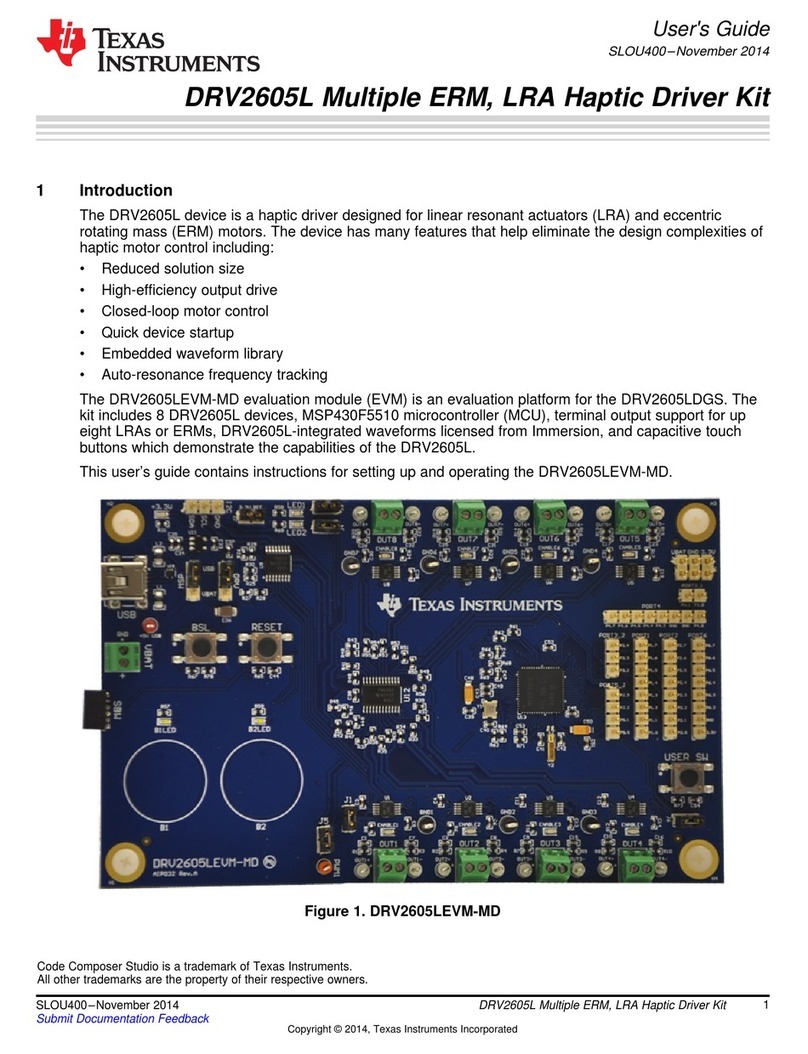

3.1 Debugging Connections between Olimex ARM-USB-TINY-H and Arty Board’s

PMOD header JD ..................................... 6

3.2 Debug Connections To the Olimex ARM-USB-TINY-H ................. 6

3.3 Debug Connections to the Arty Board JD PMOD Header ................ 6

3.4 Photo of the Arty Board showing USB and Debug Connections ............ 7

7.1 E2 Core IP FPGA Eval Kit Block Diagram ........................ 22

8.1 E3 / S5 Core IP FPGA Eval Kit Block Diagram ..................... 26

9.1 E7 / S7 Core IP FPGA Eval Kit Block Diagram ..................... 30

v

vi SiFive Core IP FPGA Eval Kit User Guide v3p0

Chapter 1

Introduction

1.1 About this Document

This document gives necessary information for a user of the SiFive Core IP FPGA Eval Kit. To

learn more about the functionality of your specific Core IP please read the appropriate Core IP

Manual.

This guide will help you download and flash the Core IP FPGA Eval Kit image to an FPGA

development board. It will help you install software tools to allow you to write, upload, and debug

code on the Eval Kit. It also contains information about what is contained in the MCS file for the

Core IP FPGA Eval Kit.

1.2 About this Release

This Eval Kit allows you to prototype and benchmark your target RISC-V software without

modifying, integrating, or synthesizing any Verilog code.

This release is intended for evaluation purposes only.

1.3 Evaluation Version Limitations

Version v19.02 of the Core IP FPGA Eval Kit has the following limitations compared with the fully

functional Core IP:

• DTIM is limited in size to 64kB.

• Peripheral Bus, System Bus, and Front Bus are not exported for additional user connections.

The evaluation can utilize the peripherals included on the FPGA.

• Not all Local and Global interrupts are exported at the top level.

To target a different FPGA platform or perform synthesis or simulation, you may obtain an

Evaluation Version of the Core IP RTL from sifive.com.

1

2SiFive Core IP FPGA Eval Kit User Guide v3p0

Chapter 2

Required Hardware

The Core IP FPGA Eval Kit requires the following hardware:

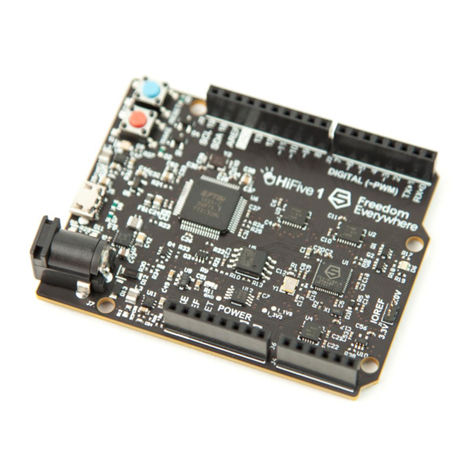

2.1 Xilinx Arty A7 Artix-7 FPGA Evaluation Kit

The Arty A7 is a Xilinx FPGA development board for makers and hobbyists. The Arty A7 comes

in two FPGA variants: The Arty A7-35T features Xilinx XC7A35TICSG324-1L. The Arty A7-100T

features the larger Xilinx XC7A100TCSG324-1. Both can be purchased from Digilent or Avnet.

http://www.xilinx.com/products/boards-and-kits/arty.html

https://store.digilentinc.com/

2.2 USB A to Micro-B Cable

Any standard USB Type A Male to Micro-B Male cable can be used to interface with the Arty. Note

that the Arty kit does not include one.

http://store.digilentinc.com/usb-a-to-micro-b-cable/

2.3 Olimex ARM-USB-TINY-H Debugger

The Olimex ARM-USB-TINY-H is a hardware JTAG debugger. The Core IP Arty FPGA Dev Kit has

a standard JTAG debugging interface, and the tools included with the Core IP FPGA Eval Kit have

been tested using the Olimex ARM-USB-TINY-H. It can be purchased from Olimex or Digi-Key.

https://www.olimex.com/Products/ARM/JTAG/ARM-USB-TINY-H/

http://www.digikey.com/

2.4 USB A to B Cable

Any standard USB Type A Male to B Male cable can be used to interface to the Olimex ARM-USB-

TINY-H Debugger. Note that the package does not include one. These are available from a variety

of sources, including Digi-Key.

http://www.digikey.com/product-detail/en/assmann-wsw-components/AK672-2-1/AE1462-

ND/930247

3

4SiFive Core IP FPGA Eval Kit User Guide v3p0

2.5 Male-To-Female Jumper Cables (10)

The connection between the Olimex ARM-USB-TINY-H and Core IP FPGA Eval Kit requires 10

connections. These can be made with Male-to-Female jumper cables. These cables are available

from Adafruit in convenient rip-apart ribbon cables:

https://www.adafruit.com/products/826

Chapter 3

Board Setup

3.1 Connecting the USB Interface

Connect the USB Type A to Micro-B cable between the USB-JTAG port (J10) of the Arty and

the host machine. This provides UART console access to the Core IP FPGA Eval Kit as well

as a 5V power source for the board. This is also the interface by which the FPGA fabric will be

programmed.

3.2 Connecting the Debugger

The debugger is essential for downloading and debugging code with your SDK. The software will

be downloaded to SPI Flash, so it will be retained. Without the debugger you can only flash

the FPGA image and run the included demo program, you cannot change the software which

executes.

Connect the Olimex ARM-USB-TINY-H with the USB Type A to B cable to the host machine. Then

connect the Olimex ARM-USB-TINY-H debugger to PMOD header JD using the 10 jumper cables.

The pinout is as shown in Figure 3.1. Note that the Olimex ARM-USB-TINY-H and the PMOD

header on the Arty Board have different numbering schemes. Figures 3.2 and 3.3 clarify the

different pinouts for the two connectors.

Figure 3.4 shows what the board looks like with all the debug connections in place.

Note: It is important to connect to PMOD header JD (not JA, JB, or JC). JD was selected over the

other PMOD headers to avoid damage to the Arty board in the event of mismatched connections.

5

6SiFive Core IP FPGA Eval Kit User Guide v3p0

Signal

Name

ARM-USB-

TINY-H Pin

Number

Suggested

Jumper

Color

Freedom E310 Arty

Dev Kit JD Pin Number

VREF 1 red 12

VREF 2 brown 6 (“VCC”)

nTRST 3 orange 2

TDI 5 yellow 7

TMS 7 green 8

TCK 9 blue 3

TDO 13 purple 1

GND 14 black 5 (“GND”)

nRST 15 grey 9

GND 16 white 11

Figure 3.1: Debugging Connections between Olimex ARM-USB-TINY-H and Arty Board’s PMOD header

JD

1 : VREF (red) 2 : VREF (brown)

3 : nTRST (orange) 4

5 : TDI (yellow) 6

7 : TMS (green) 8

NOTCH 9 : TCK (blue) 10

NOTCH 11 12

13 : TDO (purple) 14 : GND (black)

15 : nRST (grey) 16 : GND (white)

17 18

19 20

LED

Figure 3.2: Debug Connections To the Olimex ARM-USB-TINY-H

square pad 1 : TDO (purple) 7 : TDI (yellow)

2 : nTRST (orange) 8 : TMS (green)

3 : TCK (blue) 9 : nRST (grey)

4 10

“GND” 5 : GND (black) 11 : GND (white)

“VCC” 6 : VREF (brown) 12 : VREF (red)

Figure 3.3: Debug Connections to the Arty Board JD PMOD Header

Copyright © 2016-2019, SiFive Inc. All rights reserved. 7

Figure 3.4: Photo of the Arty Board showing USB and Debug Connections

8SiFive Core IP FPGA Eval Kit User Guide v3p0

Chapter 4

FPGA Flash Programming File

The Xilinx Artix-7 35T or 100T FPGA configures on power-on from an on-board 16MB QuadSPI

Flash.

To program the Arty Board, locate the desired MCS file within your Core IP package. For example,

sifive_coreip_[XX]_FPGA_Evaluation_Arty_[35|100]T_v[XXX]_rc[xx].mcs

The Xilinx Vivado Design Suite is used for flash programming. Both the Vivado Lab Edition and

WebPACK Edition 2018.2 support Artix-7 devices free of charge.

4.1 Programming the Arty 35T SPI Flash

To program the Arty 35T SPI Flash with Vivado take the following steps:

1. Launch Vivado

2. Open Hardware Manager

3. Open target board

4. Right click on the FPGA device and select ”Add Configuration Memory Device”

5. Select the following SPI flash parameters:

Part m25ql128

Manufacturer Micron

Alias n25q1283˙

3vspi-x1 x2 x4

Family mt25ql

Type spi

Density 128

Width x1 x2 x4

6. Click OK to “Do you want to program the configuration memory device now?”

7. Add the MCS file

9

10 SiFive Core IP FPGA Eval Kit User Guide v3p0

8. Select OK

9. Once the programming completes in Vivado, press the “PROG” Button on the Arty Board to

load the image into the FPGA.

4.2 Programming the Arty 100T SPI Flash

To program the Arty 100T SPI Flash with Vivado take the following steps:

1. Launch Vivado

2. Open Hardware Manager

3. Open target board

4. Right click on the FPGA device and select ”Add Configuration Memory Device”

5. Select the following SPI flash parameters:

Part s25fl128sxxxxxx0

Manufacturer Spansion

Alias s25fl127s

Family s25flxxxs

Type spi

Density 128

Width x1 x2 x4

6. Click OK to “Do you want to program the configuration memory device now?”

7. Add the MCS file

8. Select OK

9. Once the programming completes in Vivado, press the “PROG” Button on the Arty Board to

load the image into the FPGA.

Chapter 5

Boot and Run

5.1 Serial Setup

Using a terminal emulator such as GNU screen on Linux or a terminal on Windows, open a console

connection from the host computer to the Core IP FPGA Eval Kit.

Set the following parameters:

Speed 115200

Parity None

Data bits 8

Stop bits 1

Hardware Flow None

For example, on Linux using GNU Screen:

sudo screen /dev/ttyUSB2 115200

You can use Ctrl-a k to “kill” (exit) the running screen session.

Depending on your setup, you may need additional drivers or permissions to communicate over

the USB port.

If you are running on Ubuntu-style Linux, the below is an example of steps you may need to follow

to access your dev kit without sudo permissions:

1. With your board’s debug interface connected, make sure your device shows up with the

lsusb command:

> lsusb

...

Bus XXX Device XXX: ID 0403:6010 Future Technology Devices

International, Ltd FT2232C Dual USB-UART/FIFO IC

2. Set the udev rules to allow the device to be accessed by the plugdev group:

11

12 SiFive Core IP FPGA Eval Kit User Guide v3p0

> sudo vi /etc/udev/rules.d/99-openocd.rules

Add the following lines and save the file (if they are not already there):

# These are for the HiFive1 Board

SUBSYSTEM=="usb", ATTR{idVendor}=="0403",

ATTR{idProduct}=="6011", MODE="664", GROUP="plugdev"

SUBSYSTEM=="tty", ATTRS{idVendor}=="0403",

ATTRS{idProduct}=="6011", MODE="664", GROUP="plugdev"

# These are for the Olimex Debugger for use with E310 Arty Dev Kit

SUBSYSTEM=="usb", ATTR{idVendor}=="15ba",

ATTR{idProduct}=="002a", MODE="664", GROUP="plugdev"

SUBSYSTEM=="tty", ATTRS{idVendor}=="15ba",

ATTRS{idProduct}=="002a", MODE="664", GROUP="plugdev"

3. See if your board shows up as a serial device belonging to the plugdev group:

> ls /dev/ttyUSB*

/dev/ttyUSB0 /dev/ttyUSB1 /dev/tty/USB2 /dev/tty/USB3

(If you have other serial devices or multiple boards attached, you may have more devices

listed). For serial communication with the UART, you will always want to select the higher

number of the pair, in this example /dev/ttyUSB2.

> ls -l /dev/ttyUSB2

crw-rw-r-- 1 root plugdev 188, 1 Nov 28 00:00 /dev/ttyUSB1

4. Add yourself to the plugdev group to eliminate the need to sudo for access to the device.

You can use the whoami command to determine your user name.

> whoami your user name > sudo usermod -a -G plugdev your user name

5. Log out and log back in, then check that you’re now a member of the plugdev group:

> groups

... plugdev ...

Now you should be able to access the serial (UART) and debug interface without sudo

permissions.

This manual suits for next models

4

Table of contents

Other SiFive Microcontroller manuals