SiFive FE310-G000 User manual

SiFive FE310-G000 Manual

v3p1

© SiFive, Inc.

SiFive FE310-G000 Manual

Proprietary Notice

Copyright © 2016–2019, SiFive Inc. All rights reserved.

Information in this document is provided “as is,” with all faults.

SiFive expressly disclaims all warranties, representations, and conditions of any kind, whether

express or implied, including, but not limited to, the implied warranties or conditions of mer-

chantability, fitness for a particular purpose and non-infringement.

SiFive does not assume any liability rising out of the application or use of any product or circuit,

and specifically disclaims any and all liability, including without limitation indirect, incidental, spe-

cial, exemplary, or consequential damages.

SiFive reserves the right to make changes without further notice to any products herein.

Release Information

Version Date Changes

v3p1 August 22, 2019 • Fixed minor error in memory map table

v3p0 January 21, 2019

• Updated formatting and chapter organization to

match newer documents

• Fixed minor error in PLIC interrupt priorities

memory map table

• Added section on performance monitoring

• Removed chapter on Config String, which is

now a deprecated standard

v2p3 October 11, 2017 Core Complex branding

v2p2 September 28, 2017

• Clarify PLIC, PMU, RTC, WDT reset values.

• Add “empty” bit to UART rxdata register map.

• General Formatting.

v2p1 September 21, 2017 Correct the location of the config string pointer

v2p0 September 15, 2017 Fold in relevant E31 Core Complex and E300 Plat-

form information

1.0.3 July 24, 2017 Correct DWAKEUP_N and AON_PMU_OUT_0 pin

assignments

1.0.2 June 12, 2017 Clarify that QFN48 is the 6x6 Standard format

1.0.1 December 20, 2016

• Add QFN48 Package Pinout

• Add Configuration String

• Rename chip to FE310-G000

1.0 November 29, 2016 HiFive1 release

Contents

1 Introduction .............................................................................................................. 8

1.1 F 310-G000 Overview ................................................................................................ 8

1.2 31 RISC‑V Core ..................................................................................................... 10

1.3 Interrupts ................................................................................................................. 10

1.4 On-Chip Memory System...........................................................................................11

1.5 Always-On (AON) Block ............................................................................................11

1.6 GPIO Complex ......................................................................................................... 11

1.7 Universal Asynchronous Receiver/Transmitter.............................................................11

1.8 Hardware Serial Peripheral Interface (SPI) ..................................................................11

1.9 Pulse Width Modulation.............................................................................................12

1.10 Debug Support ....................................................................................................... 12

2 List of Abbreviations and Terms .................................................................13

3 E31 RISC-V Core .................................................................................................. 15

3.1 Instruction Memory System........................................................................................15

3.2 Instruction Fetch Unit ................................................................................................16

3.3 xecution Pipeline .................................................................................................... 16

3.4 Data Memory System................................................................................................17

3.5 Atomic Memory Operations........................................................................................17

3.6 Hardware Performance Monitor..................................................................................17

4 Memory Map ........................................................................................................... 18

5 Boot Process.......................................................................................................... 20

5.1 Non-volatile Code Options .........................................................................................20

5.1.1 Gate ROM (GROM)..........................................................................................20

5.1.2 Mask ROM (MROM)......................................................................................... 20

5.1.3 One-Time Programmable (OTP) Memory ...........................................................21

1

5.1.4 Quad SPI Flash Controller (QSPI)......................................................................21

5.2 Reset and Trap Vectors ............................................................................................. 21

6 Clock Generation .................................................................................................22

6.1 Clock Generation Overview .......................................................................................22

6.2 PRCI Address Space Usage ......................................................................................23

6.3 Internal Trimmable Programmable 72 MHz Oscillator (HFROSC) ..................................23

6.4 xternal 16 MHz Crystal Oscillator (HFXOSC).............................................................24

6.5 Internal High-Frequency PLL (HFPLL) ........................................................................25

6.6 PLL Output Divider.................................................................................................... 27

6.7 Internal Programmable Low-Frequency Ring Oscillator (LFROSC) ................................28

6.8 Alternate Low-Frequency Clock (LFALTCLK)...............................................................29

6.9 Clock Summary ........................................................................................................ 29

7 Power Modes.......................................................................................................... 30

7.1 Run Mode ................................................................................................................ 30

7.2 Wait Mode................................................................................................................ 30

7.3 Sleep Mode.............................................................................................................. 30

8 Interrupts.................................................................................................................. 32

8.1 Interrupt Concepts .................................................................................................... 32

8.2 Interrupt Operation.................................................................................................... 33

8.2.1 Interrupt ntry and xit .....................................................................................33

8.3 Interrupt Control Status Registers...............................................................................34

8.3.1 Machine Status Register (mstatus)..................................................................34

8.3.2 Machine Trap Vector (mtvec)............................................................................34

8.3.3 Machine Interrupt nable (mie).........................................................................35

8.3.4 Machine Interrupt Pending (mip).......................................................................36

8.3.5 Machine Cause (mcause).................................................................................36

8.4 Interrupt Priorities ..................................................................................................... 37

8.5 Interrupt Latency....................................................................................................... 37

9 Core-Local Interruptor (CLI T).....................................................................38

2

9.1 CLINT Memory Map.................................................................................................. 38

9.2 MSIP Registers......................................................................................................... 38

9.3 Timer Registers ........................................................................................................ 39

10 Platform-Level Interrupt Controller (PLIC)...........................................40

10.1 Memory Map .......................................................................................................... 40

10.2 Interrupt Sources .................................................................................................... 41

10.3 Interrupt Priorities.................................................................................................... 42

10.4 Interrupt Pending Bits .............................................................................................. 42

10.5 Interrupt nables..................................................................................................... 43

10.6 Priority Thresholds .................................................................................................. 44

10.7 Interrupt Claim Process ...........................................................................................44

10.8 Interrupt Completion................................................................................................45

11 One-Time Programmable Memory (OTP) Peripheral......................47

11.1 Memory Map .......................................................................................................... 47

11.2 Programmed-I/O lock register (otp_lock)................................................................48

11.3 Programmed-I/O Sequencing...................................................................................49

11.4 Read sequencer control register (otp_rsctrl)........................................................49

11.5 OTP Programming Warnings....................................................................................49

11.6 OTP Programming Procedure ..................................................................................50

12 Always-On (AO ) Domain ............................................................................51

12.1 AON Power Source.................................................................................................52

12.2 AON Clocking......................................................................................................... 52

12.3 AON Reset Unit ...................................................................................................... 52

12.4 xternal Reset Circuit..............................................................................................52

12.5 Reset Cause........................................................................................................... 53

12.6 Watchdog Timer (WDT) ...........................................................................................53

12.7 Real-Time Clock (RTC)............................................................................................53

12.8 Backup Registers.................................................................................................... 53

12.9 Power-Management Unit (PMU)...............................................................................53

12.10 AON Memory Map.................................................................................................53

3

13 Watchdog Timer (WDT) ..................................................................................56

13.1 Watchdog Count Register (wdogcount)...................................................................56

13.2 Watchdog Clock Selection ....................................................................................... 57

13.3 Watchdog Configuration Register (wdogcfg).............................................................57

13.4 Watchdog Compare Register (wdogcmp)...................................................................58

13.5 Watchdog Key Register (wdogkey)..........................................................................58

13.6 Watchdog Feed Address (wdogfeed).......................................................................59

13.7 Watchdog Configuration ..........................................................................................59

13.8 Watchdog Resets.................................................................................................... 59

13.9 Watchdog Interrupts (wdogip0)...............................................................................59

14 Power-Management Unit (PMU).................................................................60

14.1 PMU Overview........................................................................................................ 61

14.2 Memory Map .......................................................................................................... 61

14.3 PMU Key Register (pmukey)....................................................................................62

14.4 PMU Program......................................................................................................... 62

14.5 Initiate Sleep Sequence Register (pmusleep)...........................................................63

14.6 Wakeup Signal Conditioning ....................................................................................63

14.7 PMU Interrupt nables (pmuie) and Wakeup Cause (pmucause)...............................64

15 Real-Time Clock (RTC) ...................................................................................66

15.1 RTC Count Registers (rtccounthi/rtccountlo)...................................................66

15.2 RTC Configuration Register (rtccfg)......................................................................67

15.3 RTC Compare Register (rtccmp)............................................................................67

16 General Purpose Input/Output Controller (GPIO) ............................69

16.1 GPIO Instance in F 310-G000.................................................................................71

16.2 Memory Map .......................................................................................................... 71

16.3 Input / Output Values ............................................................................................... 71

16.4 Interrupts................................................................................................................ 72

16.5 Internal Pull-Ups ..................................................................................................... 72

16.6 Drive Strength......................................................................................................... 72

16.7 Output Inversion ..................................................................................................... 72

4

16.8 HW I/O Functions (IOF) ...........................................................................................72

17 Universal Asynchronous Receiver/Transmitter (UART)...............73

17.1 UART Overview ...................................................................................................... 73

17.2 UART Instances in F 310-G000...............................................................................73

17.3 Memory Map .......................................................................................................... 74

17.4 Transmit Data Register (txdata).............................................................................74

17.5 Receive Data Register (rxdata)..............................................................................74

17.6 Transmit Control Register (txctrl).........................................................................75

17.7 Receive Control Register (rxctrl)..........................................................................75

17.8 Interrupt Registers (ip and ie)................................................................................76

17.9 Baud Rate Divisor Register (div).............................................................................76

18 Serial Peripheral Interface (SPI) ................................................................78

18.1 SPI Overview.......................................................................................................... 78

18.2 SPI Instances in F 310-G000 ..................................................................................78

18.3 Memory Map .......................................................................................................... 79

18.4 Serial Clock Divisor Register (sckdiv).....................................................................80

18.5 Serial Clock Mode Register (sckmode).....................................................................81

18.6 Chip Select ID Register (csid)................................................................................81

18.7 Chip Select Default Register (csdef).......................................................................82

18.8 Chip Select Mode Register (csmode)........................................................................82

18.9 Delay Control Registers (delay0 and delay1).........................................................83

18.10 Frame Format Register (fmt).................................................................................83

18.11 Transmit Data Register (txdata)...........................................................................84

18.12 Receive Data Register (rxdata)............................................................................85

18.13 Transmit Watermark Register (txmark)..................................................................85

18.14 Receive Watermark Register (rxmark)...................................................................86

18.15 SPI Interrupt Registers (ie and ip)........................................................................86

18.16 SPI Flash Interface Control Register (fctrl)..........................................................87

18.17 SPI Flash Instruction Format Register (ffmt)..........................................................87

19 Pulse Width Modulator (PWM) ...................................................................88

5

19.1 PWM Overview ....................................................................................................... 88

19.2 PWM Instances in F 310-G000 ...............................................................................89

19.3 PWM Memory Map .................................................................................................89

19.4 PWM Count Register (pwmcount)............................................................................90

19.5 PWM Configuration Register (pwmcfg).....................................................................91

19.6 Scaled PWM Count Register (pwms).........................................................................92

19.7 PWM Compare Registers (pwmcmp0–pwmcmp3)........................................................92

19.8 Deglitch and Sticky Circuitry.....................................................................................93

19.9 Generating Left- or Right-Aligned PWM Waveforms ...................................................94

19.10 Generating Center-Aligned (Phase-Correct) PWM Waveforms ..................................94

19.11 Generating Arbitrary PWM Waveforms using Ganging ..............................................95

19.12 Generating One-Shot Waveforms ...........................................................................96

19.13 PWM Interrupts..................................................................................................... 96

20 Debug ...................................................................................................................... 97

20.1 Debug CSRs .......................................................................................................... 97

20.1.1 Trace and Debug Register Select (tselect)....................................................97

20.1.2 Trace and Debug Data Registers (tdata1-3)..................................................98

20.1.3 Debug Control and Status Register (dcsr).......................................................99

20.1.4 Debug PC dpc ...............................................................................................99

20.1.5 Debug Scratch dscratch...............................................................................99

20.2 Breakpoints ............................................................................................................ 99

20.2.1 Breakpoint Match Control Register mcontrol ..................................................99

20.2.2 Breakpoint Match Address Register (maddress).............................................101

20.2.3 Breakpoint xecution ....................................................................................101

20.2.4 Sharing Breakpoints Between Debug and Machine Mode ................................102

20.3 Debug Memory Map..............................................................................................102

20.3.1 Component Signal Registers (0x100–0x1FF).................................................102

20.3.2 Debug RAM (0x400–0x43f)........................................................................103

20.3.3 Debug ROM (0x800–0xFFF)........................................................................103

21 Debug Interface................................................................................................ 104

21.1 JTAG TAPC State Machine ....................................................................................104

6

21.2 Resetting JTAG Logic............................................................................................105

21.3 JTAG Clocking...................................................................................................... 105

21.4 JTAG Standard Instructions ...................................................................................106

21.5 JTAG Debug Commands .......................................................................................106

22 References.......................................................................................................... 107

7

Chapter 1

Introduction

The F 310-G000 is the first Freedom 300 SoC, and forms the basis of the HiFive1 develop-

ment board for the Freedom 300 family. The F 310-G000 is built around the 31 Core Com-

plex instantiated in the Freedom 300 platform and fabricated in the TSMC CL018G 180nm

process. This manual serves as an architectural reference and integration guide for the

F 310-G000.

The F 310-G000 is compatible with all applicable RISC‑V standards, and this document should

be read together with the official RISC‑V user-level, privileged, and external debug architecture

specifications.

1.1 FE310-G000 Overview

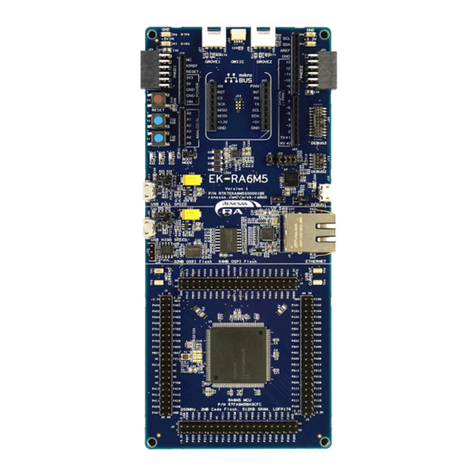

Figure 1 shows the overall block diagram of the F 310-G000.

A feature summary table can be found in Table 1.

8

F 310G-0000

31 Core Complex

GPIO Complex

Always-On Domain

P-Bus: TileLink B32 D32

QSPI0

Real-Time Clock

Platform-Level

Interrupt Control

TAPC

Debug Module

Debug RAM (28B)

Instruction Fetch

RV32IMAC

Branch Prediction

Inst. Decompressor

Instruction Buffer

M

MLoad/Store

dip

eip

sip

Instruction Cache

(16KiB, 2-way)

Instruction Cache Ref ll M

OTP (8KiB)

Data SRAM (16KiB)

UART0

QSPI1

M

JTAG

1.8V AON Core

erst_n

QSPI Flash

GPIO

Multiplier/Divider

Watchdog

Core-Local Interrupt

Control

Real-Time Clock Ticks

Backup Registers

PMU

Reset Unit

dwakeup_n

1.8V AON Pads

pmu_out_0

LFROSC

Mask ROM (8KiB)

Clock Generation

HFXOSC

PLL

HFROSC

vddpll

vsspll

hfxoscin

hfxoscout

UART1

PWM0 (8-bit)

PWM1 (16-bit)

QSPI2

C-Bus: TileLink B32 D32

A-Bus: TileLink B4 D32

M

hfclkrst

rtccmpip

wdogcmpip

Global

Interrupts

1.8V MOFF Core

3.3V MOFF Pads

Core Reset Sync corerst

pmu_out_1

psdlfaltclk

psdlfaltclksel

PWM2 (16-bit)

Figure 1: F 310-G000 top-level block diagram.

Copyrig t © 2016–2019, SiFive Inc. All rig ts reserved. 9

Feature Description Available in

QF 48

RISC-V Core

1× 31 RISC‑V cores with machine mode only, 16 KiB

2-way L1 I-cache, and 16 KiB data tightly integrated mem-

ory (DTIM).

✔

Interrupts Software and timer interrupts, 51 peripheral interrupts con-

nected to the PLIC with 7 levels of priority. ✔

UART 0 Universal Asynchronous/Synchronous Transmitters for

serial communication. ✔

UART 1 Universal Asynchronous/Synchronous Transmitters for

serial communication.

QSPI 0 Control Serial Peripheral Interface. QSPI 0 Control has 1 chip

select signal. ✔

QSPI 1 Serial Peripheral Interface. QSPI 1 has 4 chip select sig-

nals.

✔

(3 CS lines)

(2 DQ lines)

QSPI 2 Serial Peripheral Interface. QSPI 2 has 1 chip select sig-

nal.

PWM 0 8-bit Pulse-width modulator with 4 comparators. ✔

PWM 1 16-bit Pulse-width modulator with 4 comparators. ✔

PWM 2 16-bit Pulse-width modulator with 4 comparators. ✔

GPIO 32 General Purpose I/O pins. ✔

(19 pins)

Always On

Domain Supports low-power operation and wakeup. ✔

Table 1: F 310-G000 Feature Summary.

1.2 E31 RISC‑V Core

The F 310-G000 includes a 32-bit 31 RISC‑V core, which has a high-performance single-

issue in-order execution pipeline, with a peak sustainable execution rate of one instruction per

clock cycle. The 31 core supports Machine mode only as well as standard Multiply, Atomic,

and Compressed RISC‑V extensions (RV32IMAC).

The core is described in more detail in Chapter 3.

1.3 Interrupts

The F 310-G000 includes a RISC-V standard platform-level interrupt controller (PLIC), which

supports 51 global interrupts with 7 priority levels. The F 310-G000 also provides the standard

RISC‑V machine-mode timer and software interrupts via the Core-Local Interruptor (CLINT).

Interrupts are described in Chapter 8. The CLINT is described in Chapter 9. The PLIC is

described in Chapter 10.

Copyrig t © 2016–2019, SiFive Inc. All rig ts reserved. 10

1.4 On-Chip Memory System

The 31 core has a(n) 2-way set-associative 16 KiB L1 instruction cache and a(n) 16 KiB L1

DTIM.

The Level 1 memories are described in Chapter 3.

1.5 Always-On (AO ) Block

The AON block contains the reset logic for the chip, an on-chip low-frequency oscillator, a

watchdog timer, connections for an off-chip low-frequency oscillator, the real-time clock, a pro-

grammable power-management unit, and 16×32-bit backup registers that retain state while the

rest of the chip is in a low-power mode.

The AON can be instructed to put the system to sleep. The AON can be programmed to exit

sleep mode on a real-time clock interrupt or when the external digital wakeup pin, dwakeup_n, is

pulled low. The dwakeup_n input supports wired-OR connections of multiple wakeup sources.

The Always-On block is described in Chapter 12.

1.6 GPIO Complex

The GPIO complex manages the connection of digital I/O pads to digital peripherals, including

SPI, UART, and PWM controllers, as well as for regular programmed I/O operations.

The GPIO complex is described in more detail in Chapter 16.

1.7 Universal Asynchronous Receiver/Transmitter

Multiple universal asynchronous receiver/transmitter (UARTs) are available and provide a

means for serial communication between the F 310-G000 and off-chip devices.

The UART peripherals are described in Chapter 17.

1.8 Hardware Serial Peripheral Interface (SPI)

There are 3 serial peripheral interface (SPI) controllers. ach controller provides a means for

serial communication between the F 310-G000 and off-chip devices, like quad-SPI Flash mem-

ory. ach controller supports master-only operation over single-lane, dual-lane, and quad-lane

protocols. ach controller supports burst reads of 32 bytes over TileLink to accelerate instruc-

tion cache refills. 1 SPI controller can be programmed to support eXecute-In-Place (XIP) modes

to reduce SPI command overhead on instruction cache refills.

The SPI interface is described in more detail in Chapter 18.

Copyrig t © 2016–2019, SiFive Inc. All rig ts reserved. 11

1.9 Pulse Width Modulation

The pulse width modulation (PWM) peripheral can generate multiple types of waveforms on

GPIO output pins and can also be used to generate several forms of internal timer interrupt.

The PWM peripherals are described in Chapter 19.

1.10 Debug Support

The F 310-G000 provides external debugger support over an industry-standard JTAG port,

including 2 hardware-programmable breakpoints per hart.

Debug support is described in detail in Chapter 20, and the debug interface is described in

Chapter 21.

Copyrig t © 2016–2019, SiFive Inc. All rig ts reserved. 12

Term Definition

BHT Branch History Table

BTB Branch Target Buffer

RAS Return-Address Stack

CLI T Core-Local Interruptor. Generates per-hart software interrupts and timer

interrupts.

CLIC Core-Local Interrupt Controller. Configures priorities and levels for core

local interrupts.

hart HARdware Thread

DTIM Data Tightly Integrated Memory

ITIM Instruction Tightly Integrated Memory

JTAG Joint Test Action Group

LIM Loosely Integrated Memory. Used to describe memory space delivered in

a SiFive Core Complex but not tightly integrated to a CPU core.

PMP Physical Memory Protection

PLIC Platform-Level Interrupt Controller. The global interrupt controller in a

RISC-V system.

TileLink A free and open interconnect standard originally developed at UC Berke-

ley.

RO Used to describe a Read Only register field.

RW Used to describe a Read/Write register field.

WO Used to describe a Write Only registers field.

WARL Write-Any Read-Legal field. A register field that can be written with any

value, but returns only supported values when read.

WIRI Writes-Ignored, Reads-Ignore field. A read-only register field reserved for

future use. Writes to the field are ignored, and reads should ignore the

value returned.

WLRL Write-Legal, Read-Legal field. A register field that should only be written

with legal values and that only returns legal value if last written with a

legal value.

WPRI Writes-Preserve Reads-Ignore field. A register field that might contain

unknown information. Reads should ignore the value returned, but writes

to the whole register should preserve the original value.

Copyrig t © 2016–2019, SiFive Inc. All rig ts reserved. 14

Chapter 3

E31 RISC-V Core

This chapter describes the 32-bit 31 RISC‑V processor core used in the F 310-G000. The

31 processor core comprises an instruction memory system, an instruction fetch unit, an exe-

cution pipeline, a data memory system, and support for global, software, and timer interrupts.

The 31 feature set is summarized in Table 2.

Feature Description

ISA RV32IMAC.

Instruction Cache 16 KiB 2-way instruction cache.

Data Tightly Integrated Memory 16 KiB DTIM.

Modes The 31 supports the following modes:

Machine

Table 2: 31 Feature Set

3.1 Instruction Memory System

The instruction memory system consists of a dedicated 16 KiB 2-way set-associative instruction

cache. The access latency of all blocks in the instruction memory system is one clock cycle. The

instruction cache is not kept coherent with the rest of the platform memory system. Writes to

instruction memory must be synchronized with the instruction fetch stream by executing a

F NC .I instruction.

The instruction cache has a line size of 32 bytes, and a cache line fill triggers a burst access.

The core caches instructions from executable addresses. See the F 310-G000 Memory Map in

Chapter 4 for a description of executable address regions that are denoted by the attribute X.

Trying to execute an instruction from a non-executable address results in a synchronous trap.

15

3.2 Instruction Fetch Unit

The 31 instruction fetch unit contains branch prediction hardware to improve performance of

the processor core. The branch predictor comprises a 40-entry branch target buffer (BTB) which

predicts the target of taken branches, a 128-entry branch history table (BHT), which predicts the

direction of conditional branches, and a 2-entry return-address stack (RAS) which predicts the

target of procedure returns. The branch predictor has a one-cycle latency, so that correctly pre-

dicted control-flow instructions result in no penalty. Mispredicted control-flow instructions incur a

three-cycle penalty.

The 31 implements the standard Compressed (C) extension to the RISC‑V architecture, which

allows for 16-bit RISC‑V instructions.

3.3 Execution Pipeline

The 31 execution unit is a single-issue, in-order pipeline. The pipeline comprises five stages:

instruction fetch, instruction decode and register fetch, execute, data memory access, and regis-

ter writeback.

The pipeline has a peak execution rate of one instruction per clock cycle, and is fully bypassed

so that most instructions have a one-cycle result latency. There are several exceptions:

• LW has a two-cycle result latency, assuming a cache hit.

• LH, LHU, LB, and LBU have a three-cycle result latency, assuming a cache hit.

• CSR reads have a three-cycle result latency.

• MUL, MULH, MULHU, and MULHSU have a 5-cycle result latency.

• DIV, DIVU, R M, and R MU have between a 2-cycle and 33-cycle result latency, depending

on the operand values.

The pipeline only interlocks on read-after-write and write-after-write hazards, so instructions

may be scheduled to avoid stalls.

The 31 implements the standard Multiply (M) extension to the RISC‑V architecture for integer

multiplication and division. The 31 has a 8-bit per cycle hardware multiply and a 1-bit per cycle

hardware divide. The multiplier can only execute one operation at a time and will block until the

previous operation completes.

The hart will not abandon a Divide instruction in flight. This means if an interrupt handler tries to

use a register that is the destination register of a divide instruction the pipeline stalls until the

divide is complete.

Branch and jump instructions transfer control from the memory access pipeline stage. Correctly-

predicted branches and jumps incur no penalty, whereas mispredicted branches and jumps

incur a three-cycle penalty.

Copyrig t © 2016–2019, SiFive Inc. All rig ts reserved. 16

Most CSR writes result in a pipeline flush with a five-cycle penalty.

3.4 Data Memory System

The 31 data memory system consists of a DTIM. The access latency from a core to its own

DTIM is two clock cycles for full words and three clock cycles for smaller quantities. Misaligned

accesses are not supported in hardware and result in a trap to allow software emulation.

Stores are pipelined and commit on cycles where the data memory system is otherwise idle.

Loads to addresses currently in the store pipeline result in a five-cycle penalty.

3.5 Atomic Memory Operations

The 31 core supports the RISC‑V standard Atomic (A) extension on the DTIM and the periph-

eral memory region. Atomic memory operations to regions that do not support them generate an

access exception precisely at the core.

The load-reserved and store-conditional instructions are only supported on cached regions,

hence generate an access exception on DTIM and other uncached memory regions.

See T e RISC‑V Instruction Set Manual, Volume I: User-Level ISA, Version 2.1 for more infor-

mation on the instructions added by this extension.

3.6 Hardware Performance Monitor

The F 310-G000 supports a basic hardware performance monitoring facility compliant with T e

RISC‑V Instruction Set Manual, Volume II: Privileged Arc itecture, Version 1.10. The mcycle

CSR holds a count of the number of clock cycles the hart has executed since some arbitrary

time in the past. The minstret CSR holds a count of the number of instructions the hart has

retired since some arbitrary time in the past. Both are 64-bit counters. The mcycle and

minstret CSRs hold the 32 least-significant bits of the corresponding counter, and the mcycleh

and minstreth CSRs hold the most-significant 32 bits.

Copyrig t © 2016–2019, SiFive Inc. All rig ts reserved. 17

Other manuals for FE310-G000

2

Table of contents

Other SiFive Microcontroller manuals

Popular Microcontroller manuals by other brands

Texas Instruments

Texas Instruments MSP430G2955 manual

Cypress Semiconductor

Cypress Semiconductor GX3 EEPROM Programming & user guide

Parallax

Parallax 28016 manual

Geehy SEMICONDUCTOR

Geehy SEMICONDUCTOR APM32F405/415 G Series user manual

GigaDevice Semiconductor

GigaDevice Semiconductor GD32F10 Series user manual

NEC

NEC mPD780973 Series Preliminary user's manual