12 SiFive FE310-G000 Manual, Version 1.0.1

Quad SPI Flash Controller (QSPI)

The dedicated QSPI flash controller connects to external SPI flash parts that are used for execute-

in-place code. SPI flash is not available in certain scenarios such as package testing or board

designs not using SPI flash (e.g., just using on-chip OTP).

Off-chip SPI parts can vary in number of supported I/O bits (1, 2, or 4). SPI flash bits contain all

1s prior to programming.

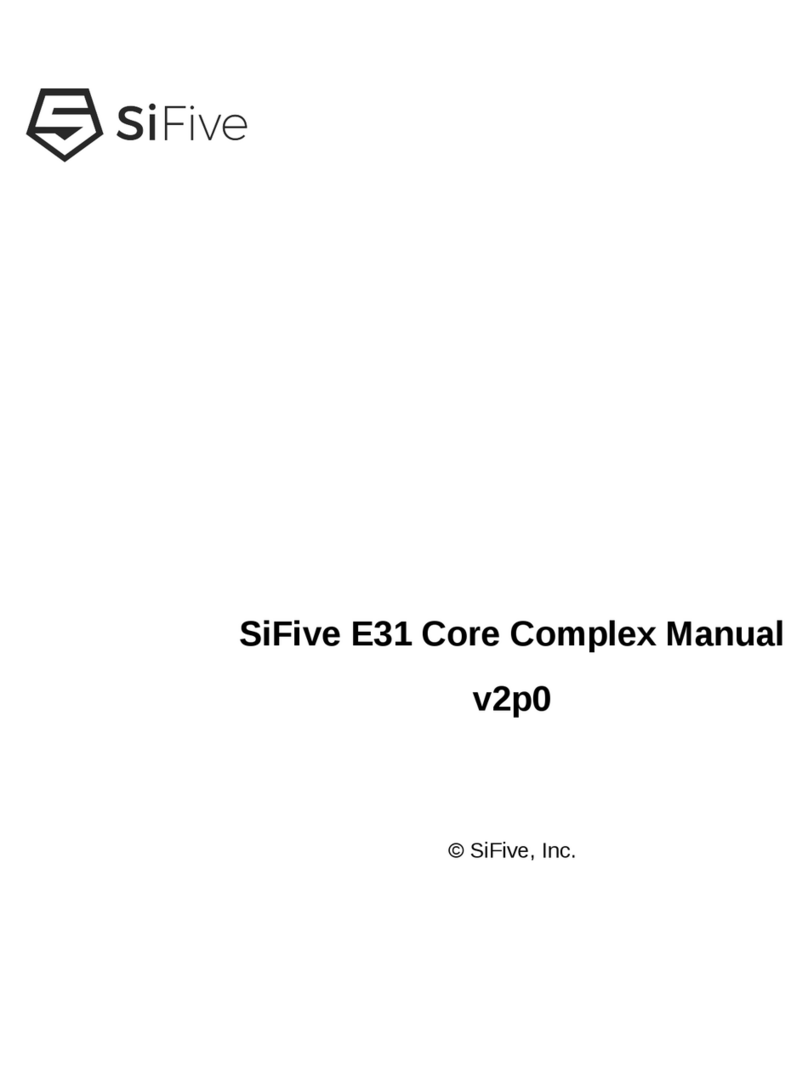

Boot Scenarios

Table 5.1 outlines the possible scenarios under which the system will be booted.

MROM OTP QSPI Boot strategy

N N N Spin and wait for debugger to download code into SRAM. Can only

execute code from SRAM.

N N U Spin and wait for debugger to download SPI flash programming code

into SRAM, and program flash from SRAM-based code.

N N P Jump to SPI code and execute-in-place through I-cache.

N U X Spin and wait for debugger to download OTP programming code into

SRAM, and program OTP from SRAM-based code.

N P X Jump to OTP code and execute using I-cache.

P N N Spin and wait for debugger to download application code into SRAM.

Can use ROM library routines.

P N U Spin and wait for debugger to download SPI flash programming code

into SRAM, but can use ROM library routines.

P N P Jump to SPI code and execute-in-place through I-cache. Code can use

ROM library routines.

P U X Spin and wait for debugger to download OTP flash programming code

into SRAM, but can use ROM library routines.

P P X Jump to OTP code and execute using I-cache.

Table 5.1: Boot process for various non-volatile code storage scenarios. The letter N indicates

not available (either not present or not functioning), U indicates present but unprogrammed, P

indicates present and programmed, X indicates don’t care.

The three distinct possible boot actions are “spin and wait”, “jump to OTP”, and “jump to SPI”. The

logic to select one of these actions depends on both the supported/working hardware on the chip

and the dynamic state of the system.

Reset and Trap Vectors

The reset PC value is affected by the IP enable pads, as shown below:

When reset is directed to start fetching from 0x0000 0000, the core will enter a trap loop, repeatedly

fetching 0 (illegal instruction) from address 0x0.

When reset is directed to start fetching from the QSPI, if the first word in the external QSPI flash

has not been programmed it will contain all 1s, which is an illegal instruction. The core will then