SiFive E31 User manual

SiFive E31 Core Complex Manual

v2p0

© SiFive, Inc.

SiFive E31 Core Complex Manual

Proprietary Notice

Copyright © 2017–2018, SiFive Inc. All rights reserved.

Information in this document is provided “as is,” with all faults.

SiFive expressly disclaims all warranties, representations, and conditions of any kind, whether

express or implied, including, but not limited to, the implied warranties or conditions of mer-

chantability, fitness for a particular purpose and non-infringement.

SiFive does not assume any liability rising out of the application or use of any product or circuit,

and specifically disclaims any and all liability, including without limitation indirect, incidental, spe-

cial, exemplary, or consequential damages.

SiFive reserves the right to make changes without further notice to any products herein.

Release Information

Version Date Changes

v2p0 June 01, 2018

• Updated E31 Core Complex definition; 4 hw

breakpoints and 127 Global interrupts.

• Moved Interface and Debug Interface chapters

to User Guide.

v1p2 October 11, 2017

• Core Complex branding

• Added references

• Updated interrupt chapter

v1p1 August 25, 2017

• Updated text descriptions

• Updated register and memory map tables for

consistency

v1p0 May 04, 2017

• Initial release

• Describes the functionality of the SiFive E31

Core Complex

Contents

1 Introduction .............................................................................................................. 4

1.1 E31 Core Complex Overview .......................................................................................4

1.2 E31 R SC‑V Core ....................................................................................................... 5

1.3 Debug Support ........................................................................................................... 5

1.4 nterrupts ................................................................................................................... 6

1.5 Memory System.......................................................................................................... 6

2 List of Abbreviations and Terms ...................................................................7

3 E31 RISC-V Core .................................................................................................... 8

3.1 nstruction Memory System..........................................................................................8

3.1.1 -Cache Reconfigurability ....................................................................................9

3.2 nstruction Fetch Unit .................................................................................................. 9

3.3 Execution Pipeline ...................................................................................................... 9

3.4 Data Memory System................................................................................................10

3.5 Atomic Memory Operations........................................................................................10

3.6 Local nterrupts......................................................................................................... 10

3.7 Supported Modes ..................................................................................................... 11

3.8 Physical Memory Protection (PMP).............................................................................11

3.8.1 Functional Description ......................................................................................11

3.8.2 Region Locking ................................................................................................11

3.9 Hardware Performance Monitor..................................................................................12

4 Memory Map ........................................................................................................... 14

5 Interrupts.................................................................................................................. 15

5.1 nterrupt Concepts .................................................................................................... 15

5.2 nterrupt Entry and Exit..............................................................................................16

5.3 nterrupt Control Status Registers...............................................................................17

1

5.3.1 Machine Status Register (mstatus)..................................................................17

5.3.2 Machine nterrupt Enable Register (mie)............................................................17

5.3.3 Machine nterrupt Pending (mip).......................................................................18

5.3.4 Machine Cause Register (mcause)....................................................................18

5.3.5 Machine Trap Vector (mtvec)............................................................................20

5.4 nterrupt Priorities ..................................................................................................... 21

5.5 nterrupt Latency....................................................................................................... 21

6 Core Local Interruptor (CLINT).....................................................................22

6.1 CL NT Memory Map.................................................................................................. 22

6.2 MS P Registers......................................................................................................... 22

6.3 Timer Registers ........................................................................................................ 23

7 Platform-Level Interrupt Controller (PLIC) .............................................24

7.1 Memory Map ............................................................................................................ 24

7.2 nterrupt Sources ...................................................................................................... 25

7.3 nterrupt Priorities ..................................................................................................... 26

7.4 nterrupt Pending Bits................................................................................................26

7.5 nterrupt Enables ...................................................................................................... 27

7.6 Priority Thresholds .................................................................................................... 28

7.7 nterrupt Claim Process .............................................................................................28

7.8 nterrupt Completion.................................................................................................. 28

8 Debug......................................................................................................................... 30

8.1 Debug CSRs ............................................................................................................ 30

8.1.1 Trace and Debug Register Select (tselect)......................................................30

8.1.2 Trace and Debug Data Registers (tdata1-3)....................................................31

8.1.3 Debug Control and Status Register (dcsr).........................................................32

8.1.4 Debug PC dpc.................................................................................................32

8.1.5 Debug Scratch dscratch ................................................................................32

8.2 Breakpoints .............................................................................................................. 32

8.2.1 Breakpoint Match Control Register mcontrol ....................................................32

8.2.2 Breakpoint Match Address Register (maddress)................................................34

2

8.2.3 Breakpoint Execution........................................................................................34

8.2.4 Sharing Breakpoints Between Debug and Machine Mode ....................................35

8.3 Debug Memory Map.................................................................................................. 35

8.3.1 Debug RAM and Program Buffer (0x300–0x3FF)...............................................35

8.3.2 Debug ROM (0x800–0xFFF)............................................................................35

8.3.3 Debug Flags (0x100–0x110,0x400–0x7FF)....................................................36

8.3.4 Safe Zero Address ...........................................................................................36

9 References .............................................................................................................. 37

3

Chapter 1

Introduction

SiFive’s E31 Core Complex is a high performance implementation of the R SC‑V RV32 MAC

architecture. The SiFive E31 Core Complex is guaranteed to be compatible with all applicable

R SC‑V standards, and this document should be read together with the official R SC‑V user-

level, privileged, and external debug architecture specifications.

A summary of features in the E31 Core Complex can be found in Table 1.

E31 Core Complex Feature Set

Feature Description

Number of Harts 1 Hart.

E31 Core 1× E31 R SC‑V core.

Local nterrupts 16 Local nterrupt signals per hart which can be connected to

off core complex devices.

PL C nterrupts 127 nterrupt signals which can be connected to off core

complex devices.

PL C Priority Levels The PL C supports 7 priority levels.

Hardware Breakpoints 4 hardware breakpoints.

Physical Memory Protection

Unit

PMP with 8 x regions and a minimum granularity of 4 bytes.

Table 1: E31 Core Complex Feature Set

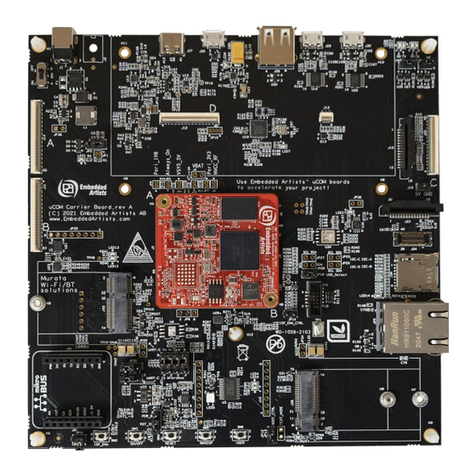

1.1 E31 Core Complex verview

An overview of the SiFive E31 Core Complex is shown in Figure 1. This R SC-V Core P

includes a 32-bit R SC‑V microcontroller core, memory interfaces including an instruction cache

as well as instruction and data tightly integrated memory, local and global interrupt support,

physical memory protection, a debug unit, outgoing external TileLink platform ports, and an

incoming TileLink master port.

4

Figure 1: E31 Core Complex Block Diagram

The E31 Core Complex memory map is detailed in Chapter 4, and the interfaces are described

in full in the E31 Core Complex User Guide.

1.2 E31 RISC‑V Core

The E31 Core Complex includes a 32-bit E31 R SC‑V core, which has a high-performance sin-

gle-issue in-order execution pipeline, with a peak sustainable execution rate of one instruction

per clock cycle. The E31 core supports Machine and User privilege modes as well as standard

Multiply, Atomic, and Compressed R SC‑V extensions (RV32 MAC).

The core is described in more detail in Chapter 3.

1.3 Debug Support

The E31 Core Complex provides external debugger support over an industry-standard JTAG

port, including 4 hardware-programmable breakpoints per hart.

Copyrig t © 2017–2018, SiFive Inc. All rig ts reserved. 5

Debug support is described in detail in Chapter 8, and the debug interface is described in the

E31 Core Complex User Guide.

1.4 Interrupts

The E31 Core Complex supports 16 high-priority, low-latency local vectored interrupts per-hart.

This Core Complex includes a R SC-V standard platform-level interrupt controller (PL C), which

supports 127 global interrupts with 7 priority levels. This Core Complex also provides the stan-

dard R SC‑V machine-mode timer and software interrupts via the Core Local nterruptor

(CL NT).

nterrupts are described in Chapter 5. The CL NT is described in Chapter 6. The PL C is

described in in Chapter 7.

1.5 Memory System

The E31 Core Complex memory system has Tightly ntegrated nstruction and Data Memory

sub-systems optimized for high performance. The instruction subsystem consists of a 16 KiB

2-way instruction cache with the ability to reconfigure a single way into a fixed-address tightly

integrated memory. The data subsystem allows for a maximum DT M size of 64 KiB.

The memory system is described in more detail in Chapter 3.

Copyrig t © 2017–2018, SiFive Inc. All rig ts reserved. 6

Chapter 2

List of Abbreviations and Terms

Term Definition

BHT Branch History Table

BTB Branch Target Buffer

RAS Return-Address Stack

CLINT Core Local nterruptor. Generates per-hart software interrupts and timer

interrupts.

hart HARdware Thread

DTIM Data Tightly ntegrated Memory

ITIM nstruction Tightly ntegrated Memory

JTAG Joint Test Action Group

LIM Loosely ntegrated Memory. Used to describe memory space delivered in

a SiFive Core Complex but not tightly integrated to a CPU core.

PMP Physical Memory Protection

PLIC Platform-Level nterrupt Controller. The global interrupt controller in a

R SC-V system.

TileLink A free and open interconnect standard originally developed at UC Berke-

ley.

R Used to describe a Read Only register field.

RW Used to describe a Read/Write register field.

W Used to describe a Write Only registers field.

WARL Write-Any Read-Legal field. A register field that can be written with any

value, but returns only supported values when read.

WIRI Writes- gnored, Reads- gnore field. A read-only register field reserved for

future use. Writes to the field are ignored, and reads should ignore the

value returned.

WLRL Write-Legal, Read-Legal field. A register field that should only be written

with legal values and that only returns legal value if last written with a

legal value.

WPRI Writes-Preserve Reads- gnore field. A register field that might contain

unknown information. Reads should ignore the value returned, but writes

to the whole register should preserve the original value.

7

Chapter 3

E31 RISC-V Core

This chapter describes the 32-bit E31 R SC‑V processor core used in the E31 Core Complex.

The E31 processor core comprises an instruction memory system, an instruction fetch unit, an

execution pipeline, a data memory system, and support for local interrupts.

The E31 feature set is summarized in Table 2.

Feature Description

SA RV32 MAC.

nstruction Cache 16 KiB 2-way instruction cache.

nstruction Tightly ntegrated Memory The E31 has support for an T M with a maxi-

mum size of 8 KiB.

Data Tightly ntegrated Memory 64 KiB DT M.

Modes The E31 supports the following modes:

Machine Mode, User Mode.

Table 2: E31 Feature Set

3.1 Instruction Memory System

The instruction memory system consists of a dedicated 16 KiB 2-way set-associative instruction

cache. The access latency of all blocks in the instruction memory system is one clock cycle. The

instruction cache is not kept coherent with the rest of the platform memory system. Writes to

instruction memory must be synchronized with the instruction fetch stream by executing a

FENCE. instruction.

The instruction cache has a line size of 64 bytes, and a cache line fill triggers a burst access

outside of the E31 Core Complex. The core caches instructions from executable addresses,

with the exception of the nstruction Tightly ntegrated Memory ( T M), which is further described

in Section 3.1.1. See the E31 Core Complex Memory Map in Chapter 4 for a description of exe-

cutable address regions that are denoted by the attribute X.

Trying to execute an instruction from a non-executable address results in a synchronous trap.

8

3.1.1 I-Cache Reconfigurability

The instruction cache can be partially reconfigured into T M, which occupies a fixed address

range in the memory map. T M provides high-performance, predictable instruction delivery.

Fetching an instruction from T M is as fast as an instruction-cache hit, with no possibility of a

cache miss. T M can hold data as well as instructions, though loads and stores from a core to

its T M are not as performant as loads and stores to its Data Tightly ntegrated Memory (DT M).

The instruction cache can be configured as T M for all ways except for 1 in units of cache lines

(64 bytes). A single instruction cache way must remain an instruction cache. T M is allocated

simply by storing to it. A store to the nth byte of the T M memory map reallocates the first n+1

bytes of instruction cache as T M, rounded up to the next cache line.

T M is deallocated by storing zero to the first byte after the T M region, that is, 8 KiB after the

base address of T M as indicated in the Memory Map in Chapter 4. The deallocated T M space

is automatically returned to the instruction cache.

For determinism, software must clear the contents of T M after allocating it. t is unpredictable

whether T M contents are preserved between deallocation and allocation.

3.2 Instruction Fetch Unit

The E31 instruction fetch unit contains branch prediction hardware to improve performance of

the processor core. The branch predictor comprises a 28-entry branch target buffer (BTB) which

predicts the target of taken branches, a 512-entry branch history table (BHT), which predicts the

direction of conditional branches, and a 6-entry return-address stack (RAS) which predicts the

target of procedure returns. The branch predictor has a one-cycle latency, so that correctly pre-

dicted control-flow instructions result in no penalty. Mispredicted control-flow instructions incur a

three-cycle penalty.

The E31 implements the standard Compressed (C) extension to the R SC‑V architecture, which

allows for 16-bit R SC‑V instructions.

3.3 Execution Pipeline

The E31 execution unit is a single-issue, in-order pipeline. The pipeline comprises five stages:

instruction fetch, instruction decode and register fetch, execute, data memory access, and regis-

ter writeback.

The pipeline has a peak execution rate of one instruction per clock cycle, and is fully bypassed

so that most instructions have a one-cycle result latency. There are several exceptions:

• LW has a two-cycle result latency, assuming a cache hit.

• LH, LHU, LB, and LBU have a three-cycle result latency, assuming a cache hit.

• CSR reads have a three-cycle result latency.

Copyrig t © 2017–2018, SiFive Inc. All rig ts reserved. 9

• MUL, MULH, MULHU, and MULHSU have a 2-cycle result latency.

• D V, D VU, REM, and REMU have between a 2-cycle and 33-cycle result latency, depending

on the operand values.

The pipeline only interlocks on read-after-write and write-after-write hazards, so instructions

may be scheduled to avoid stalls.

The E31 implements the standard Multiply (M) extension to the R SC‑V architecture for integer

multiplication and division. The E31 has a 32-bit per cycle hardware multiply and a 1-bit per

cycle hardware divide. The multiplier is fully pipelined and can begin a new operation on each

cycle, with a maximum throughput of one operation per cycle.

Branch and jump instructions transfer control from the memory access pipeline stage. Correctly-

predicted branches and jumps incur no penalty, whereas mispredicted branches and jumps

incur a three-cycle penalty.

Most CSR writes result in a pipeline flush with a five-cycle penalty.

3.4 Data Memory System

The E31 data memory system consists of a DT M interface, which supports up to 64 KiB. The

access latency from a core to its own DT M is two clock cycles for full words and three clock

cycles for smaller quantities. Misaligned accesses are not supported in hardware and result in a

trap to allow software emulation.

Stores are pipelined and commit on cycles where the data memory system is otherwise idle.

Loads to addresses currently in the store pipeline result in a five-cycle penalty.

3.5 Atomic Memory perations

The E31 core supports the R SC‑V standard Atomic (A) extension on the DT M and the Periph-

eral Port. Atomic memory operations to regions that do not support them generate an access

exception precisely at the core.

The load-reserved and store-conditional instructions are only supported on cached regions,

hence generate an access exception on DT M and other uncached memory regions.

See T e RISC‑V Instruction Set Manual, Volume I: User-Level ISA, Version 2.1 for more infor-

mation on the instructions added by this extension.

3.6 Local Interrupts

The E31 supports up to 16 local interrupt sources that are routed directly to the core. See Chap-

ter 5 for a detailed description of Local nterrupts.

Copyrig t © 2017–2018, SiFive Inc. All rig ts reserved. 10

3.7 Supported Modes

The E31 supports R SC‑V user mode, providing two levels of privilege: machine (M) and user

(U).

U-mode provides a mechanism to isolate application processes from each other and from

trusted code running in M-mode.

See T e RISC‑V Instruction Set Manual, Volume II: Privileged Arc itecture, Version 1.10 for

more information on the privilege modes.

3.8 Physical Memory Protection (PMP)

The E31 includes a Physical Memory Protection (PMP) unit compliant with T e RISC‑V Instruc-

tion Set Manual, Volume II: Privileged Arc itecture, Version 1.10. PMP can be used to set mem-

ory access privileges (read, write, execute) for specified memory regions. The E31 PMP sup-

ports 8 regions with a minimum region size of 4 bytes.

This section describes how PMP concepts in the R SC‑V architecture apply to the E31. The

definitive resource for information about the R SC‑V PMP is T e RISC‑V Instruction Set Manual,

Volume II: Privileged Arc itecture, Version 1.10.

3.8.1 Functional Description

The E31 includes a PMP unit, which can be used to restrict access to memory and isolate

processes from each other.

The E31 PMP unit has 8 regions and a minimum granularity of 4 bytes. Overlapping regions are

permitted. The E31 PMP unit implements the architecturally defined pmpcfgX CSRs pmpcfg0

and pmpcfg1 supporting 8 regions. pmpcfg2 and pmpcfg3 are implemented but hardwired to

zero.

The PMP registers may only be programmed in M-mode. Ordinarily, the PMP unit enforces per-

missions on U-mode accesses. However, locked regions (see Section 3.8.2) additionally

enforce their permissions on M-mode.

3.8.2 Region Locking

The PMP allows for region locking whereby, once a region is locked, further writes to the config-

uration and address registers are ignored. Locked PMP entries may only be unlocked with a

system reset. A region may be locked by setting the Lbit in the pmpicfg register.

n addition to locking the PMP entry, the Lbit indicates whether the R/W/X permissions are

enforced on M-Mode accesses. When the Lbit is set, these permissions are enforced for all

privilege modes. When the Lbit is clear, the R/W/X permissions apply only to U-mode.

Copyrig t © 2017–2018, SiFive Inc. All rig ts reserved. 11

When implementing less than the maximum DT M RAM, a PMP region encompassing the unim-

plemented address space must be locked with no R/W/X permissions. Doing so forces all

access to the unimplemented address space to generate an exception.

For example, if implementing 32 KiB of DT M RAM, then setting pmp0cfg=0x98 and

pmpaddr0=0x2000_0FFF disables access to the unimplemented 32 KiB region above.

3.9 Hardware Performance Monitor

The E31 Core Complex supports a basic hardware performance monitoring facility compliant

with T e RISC‑V Instruction Set Manual, Volume II: Privileged Arc itecture, Version 1.10. The

mcycle CSR holds a count of the number of clock cycles the hart has executed since some

arbitrary time in the past. The minstret CSR holds a count of the number of instructions the

hart has retired since some arbitrary time in the past. Both are 64-bit counters. The mcycle and

minstret CSRs hold the 32 least-significant bits of the corresponding counter, and the mcycleh

and minstreth CSRs hold the most-significant 32 bits.

The hardware performance monitor includes two additional event counters, mhpmcounter3 and

mhpmcounter4. The event selector CSRs mhpmevent3 and mhpmevent4 are registers that con-

trol which event causes the corresponding counter to increment. The mhpmcounters are 40-bit

counters. The mhpmcounter_i CSR holds the 32 least-significant bits of the corresponding

counter, and the mhpmcounter_ih CSR holds the 8 most-significant bits.

The event selectors are partitioned into two fields, as shown in Table 3: the lower 8 bits select

an event class, and the upper bits form a mask of events in that class. The counter increments if

the event corresponding to any set mask bit occurs. For example, if mhpmevent3 is set to

0x4200, then mhpmcounter3 will increment when either a load instruction or a conditional

branch instruction retires. Note that an event selector of 0 means "count nothing."

Copyrig t © 2017–2018, SiFive Inc. All rig ts reserved. 12

Machine Hardware Performance Monitor Event Register

nstruction Commit Events, mhpeventX[7:0] = 0

Bits Meaning

8 Exception taken

9 nteger load instruction retired

10 nteger store instruction retired

11 Atomic memory operation retired

12 System instruction retired

13 nteger arithmetic instruction retired

14 Conditional branch retired

15 JAL instruction retired

16 JALR instruction retired

17 nteger multiplication instruction retired

18 nteger division instruction retired

Microarchitectural Events , mhpeventX[7:0] = 1

Bits Meaning

8 Load-use interlock

9 Long-latency interlock

10 CSR read interlock

11 nstruction cache/ T M busy

12 Data cache/DT M busy

13 Branch direction misprediction

14 Branch/jump target misprediction

15 Pipeline flush from CSR write

16 Pipeline flush from other event

17 nteger multiplication interlock

Memory System Events, mhpeventX[7:0] = 2

Bits Meaning

8 nstruction cache miss

9 Memory-mapped /O access

Table 3: mhpmevent Register Description

Copyrig t © 2017–2018, SiFive Inc. All rig ts reserved. 13

Chapter 4

Memory Map

The memory map of the E31 Core Complex is shown in Table 4.

Base Top Attr. Description Notes

0x0000_0000 0x0000_00FF Reserved

0x0000_0100 0x0000_0FFF RWX A Debug

0x0000_1000 0x01FF_FFFF Reserved

Debug Address Space

0x0200_0000 0x0200_FFFF RW A CL NT

0x0201_0000 0x07FF_FFFF Reserved

0x0800_0000 0x0800_1FFF RWX A T M (8 KiB)

0x0800_2000 0x0BFF_FFFF Reserved

0x0C00_0000 0x0FFF_FFFF RW A PL C

0x1000_0000 0x1FFF_FFFF Reserved

On Core Complex

Devices

0x2000_0000 0x3FFF_FFFF RWX A Peripheral Port

(512 MiB)

0x4000_0000 0x5FFF_FFFF RWX System Port (512 MiB)

0x6000_0000 0x7FFF_FFFF Reserved

Off Core Complex

Address Space for Exter-

nal /O

0x8000_0000 0x8000_FFFF RWX A Data Tightly ntegrated

Memory (DT M)

(64 KiB)

0x8001_0000 0xFFFF_FFFF Reserved

On Core Complex

Address Space

Table 4: E31 Core Complex Memory Map. Memory Attributes: R- Read, W- Write, X- Exe-

cute, C- Cacheable, A- Atomics

14

Chapter 5

Interrupts

This chapter describes how interrupt concepts in the R SC‑V architecture apply to the E31 Core

Complex. The definitive resource for information about the R SC‑V interrupt architecture is T e

RISC‑V Instruction Set Manual, Volume II: Privileged Arc itecture, Version 1.10.

5.1 Interrupt Concepts

E31 Core Complex has support for the following interrupts: local (including software and timer)

and global.

Local interrupts are signaled directly to an individual hart with a dedicated interrupt value. This

allows for reduced interrupt latency as no arbitration is required to determine which hart will ser-

vice a given request and no additional memory accesses are required to determine the cause of

the interrupt. Software and timer interrupts are local interrupts generated by the Core Local

nterruptor (CL NT).

Global interrupts, by contrast, are routed through a Platform-Level nterrupt Controller (PL C),

which can direct interrupts to any hart in the system via the external interrupt. Decoupling global

interrupts from the hart(s) allows the design of the PL C to be tailored to the platform, permitting

a broad range of attributes like the number of interrupts and the prioritization and routing

schemes.

This chapter describes the E31 Core Complex interrupt architecture. Chapter 6 describes the

Core Local nterruptor. Chapter 7 describes the global interrupt architecture and the PL C

design.

The E31 Core Complex interrupt architecture is depicted in Figure 2.

15

Figure 2: E31 Core Complex nterrupt Architecture Block Diagram.

5.2 Interrupt Entry and Exit

When a R SC‑V hart takes an interrupt, the following occurs:

• The value of mstatus.MIE is copied into mstatus.MPIE, and then mstatus.MIE is cleared,

effectively disabling interrupts.

• The current pc is copied into the mepc register, and then pc is set to the value of mtvec. n

the case where vectored interrupts are enabled, pc is set to mtvec.BASE + 4 × exception

code.

• The privilege mode prior to the interrupt is encoded in mstatus.MPP.

At this point, control is handed over to software in the interrupt handler with interrupts disabled.

nterrupts can be re-enabled by explicitly setting mstatus.MIE or by executing an MRET instruc-

tion to exit the handler. When an MRET instruction is executed, the following occurs:

• The privilege mode is set to the value encoded in mstatus.MPP.

• The value of mstatus.MPIE is copied into mstatus.MIE.

• The pc is set to the value of mepc.

At this point control is handed over to software.

The Control and Status Registers involved in handling R SC‑V interrupts are described in Sec-

tion 5.3

Copyrig t © 2017–2018, SiFive Inc. All rig ts reserved. 16

5.3 Interrupt Control Status Registers

The E31 Core Complex specific implementation of interrupt CSRs is described below. For a

complete description of R SC‑V interrupt behavior and how to access CSRs, please consult T e

RISC‑V Instruction Set Manual, Volume II: Privileged Arc itecture, Version 1.10.

5.3.1 Machine Status Register (mstatus)

The mstatus register keeps track of and controls the hart’s current operating state, including

whether or not interrupts are enabled. A summary of the mstatus fields related to interrupts in

the E31 Core Complex is provided in Table 5. Note that this is not a complete description of

mstatus as it contains fields unrelated to interrupts. For the full description of mstatus, please

consult the T e RISC‑V Instruction Set Manual, Volume II: Privileged Arc itecture, Version 1.10.

Machine Status Register

CSR mstatus

Bits Field Name Attr. Description

[2:0] Reserved WPR

3 M E RW Machine nterrupt Enable

[6:4] Reserved WPR

7 MP E RW Machine Previous nterrupt Enable

[10:8] Reserved WPR

[12:11] MPP RW Machine Previous Privilege Mode

Table 5: E31 Core Complex mstatus Register (partial)

nterrupts are enabled by setting the M E bit in mstatus and by enabling the desired individual

interrupt in the mie register, described in Section 5.3.2.

5.3.2 Machine Interrupt Enable Register (mie)

ndividual interrupts are enabled by setting the appropriate bit in the mie register. The mie regis-

ter is described in Table 6.

Copyrig t © 2017–2018, SiFive Inc. All rig ts reserved. 17

Machine Interrupt Enable Register

CSR mie

Bits Field Name Attr. Description

[2:0] Reserved WPR

3 MS E RW Machine Software nterrupt Enable

[6:4] Reserved WPR

7 MT E RW Machine Timer nterrupt Enable

[10:8] Reserved WPR

11 ME E RW Machine External nterrupt Enable

[15:12] Reserved WPR

16 L E0 RW Local nterrupt 0 Enable

17 L E1 RW Local nterrupt 1 Enable

18 L E2 RW Local nterrupt 2 Enable

…

31 L E15 RW Local nterrupt 15 Enable

Table 6: mie Register

5.3.3 Machine Interrupt Pending (mip)

The machine interrupt pending (mip) register indicates which interrupts are currently pending.

The mip register is described in Table 7.

Machine Interrupt Pending Register

CSR mip

Bits Field Name Attr. Description

[2:0] Reserved W R

3 MS P RO Machine Software nterrupt Pending

[6:4] Reserved W R

7 MT P RO Machine Timer nterrupt Pending

[10:8] Reserved W R

11 ME P RO Machine External nterrupt Pending

[15:12] Reserved W R

16 L P0 RO Local nterrupt 0 Pending

17 L P1 RO Local nterrupt 1 Pending

18 L P2 RO Local nterrupt 2 Pending

…

31 L P15 RO Local nterrupt 15 Pending

Table 7: mip Register

5.3.4 Machine Cause Register (mcause)

When a trap is taken in machine mode, mcause is written with a code indicating the event that

caused the trap. When the event that caused the trap is an interrupt, the most-significant bit of

mcause is set to 1, and the least-significant bits indicate the interrupt number, using the same

Copyrig t © 2017–2018, SiFive Inc. All rig ts reserved. 18

Table of contents

Other SiFive Microcontroller manuals