– 6 –

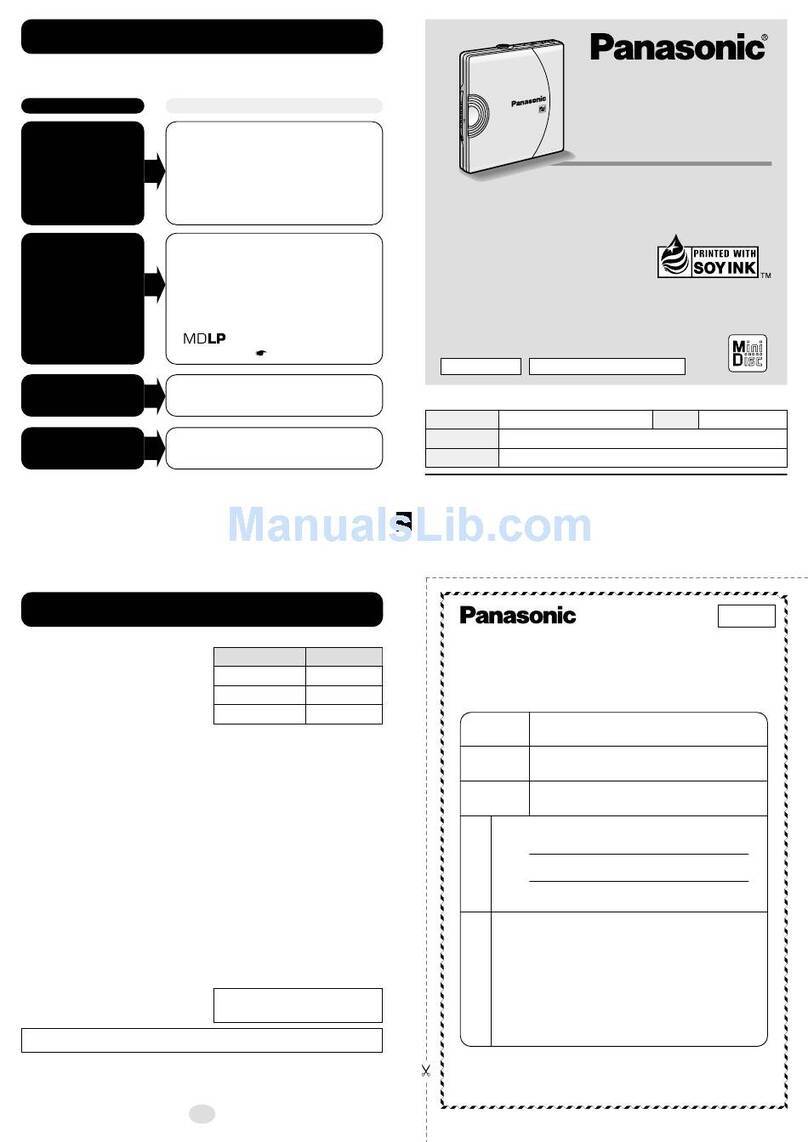

100 V1. 000

ROM version display

SHUF

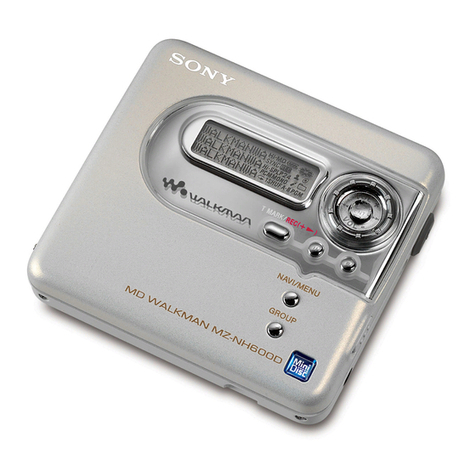

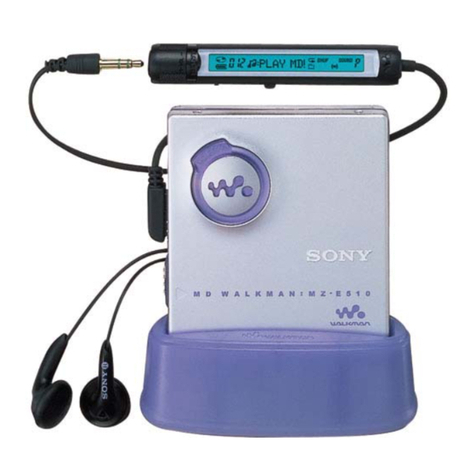

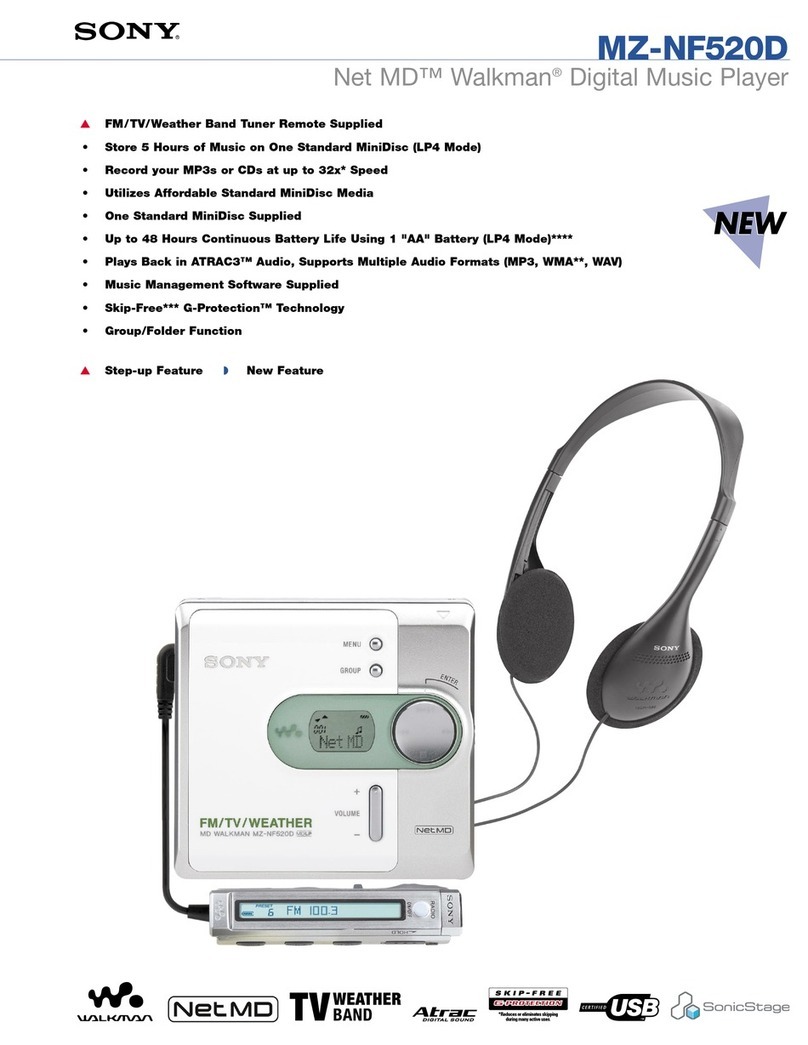

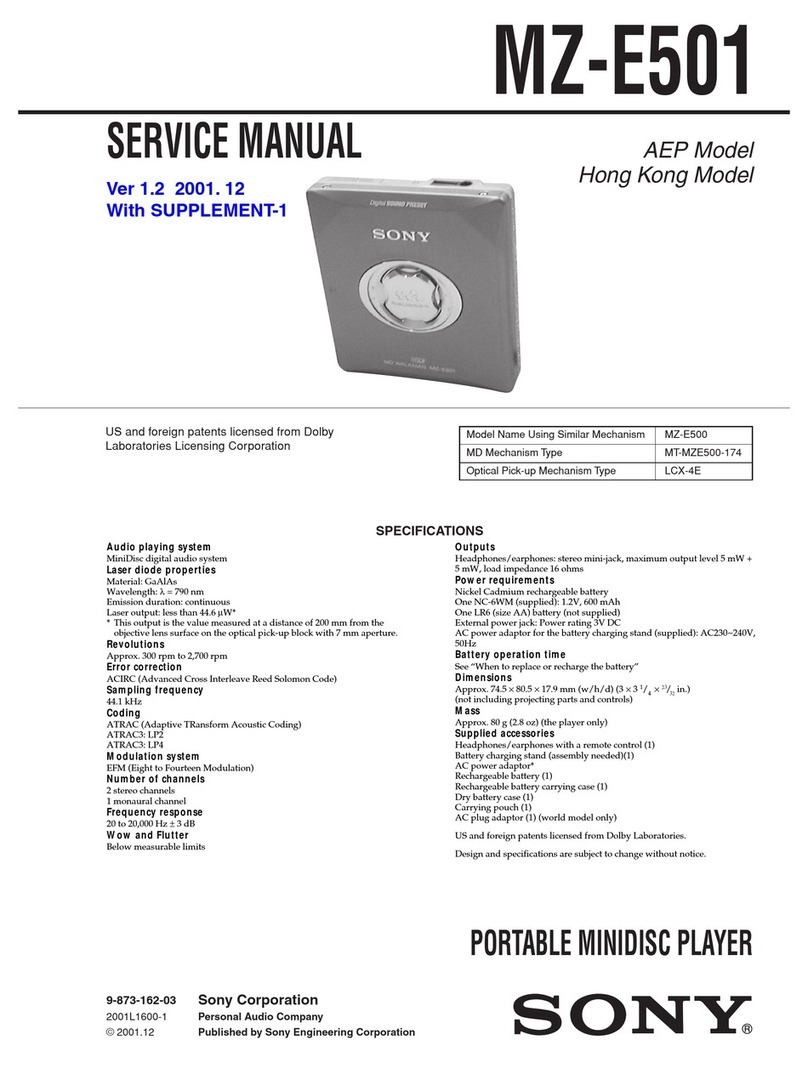

LCD on remote commander

SECTION 4

TEST MODE

Outline

• In this set, overall adjustment mode is made available by enter-

ing test mode to perform automatic adjustment of CD and MO.

In the overall adjustment mode, the disc is determined whether

it is CD or MO and adjustments are performed in sequence. If a

fault is found, the location of the fault is displayed. Also, in

servo mode, each adjustment can be automatically made.

• Operation in the test mode is performed with the remote com-

mander. A key having no particular description in the text, indi-

cates a remote commander key.

Setting theTest Mode

To enter the test mode, two methods are available :

1. Entering method with key input.

Turn on the HOLD switch on the set. While pressing the p

key on the set, press the following remote commander keys in

the following order :

”/+n”/+n=n=n”/+n=n

”/+n=nPnP

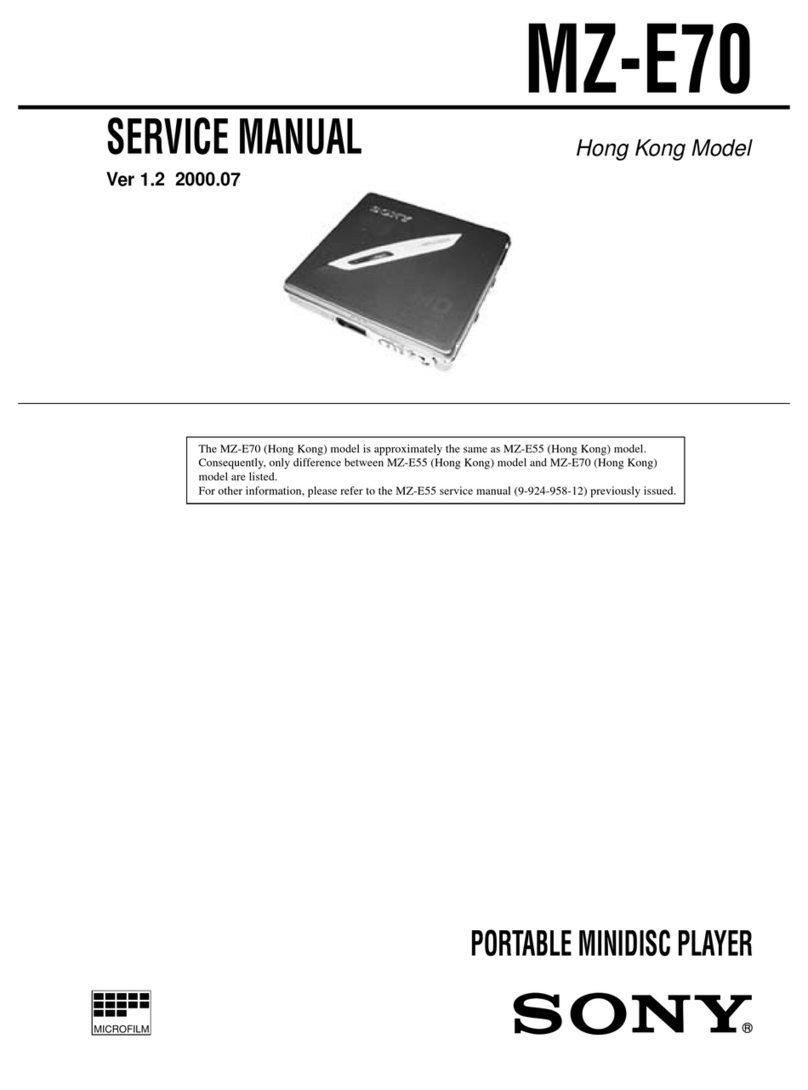

2. Entering method by shorting the test point

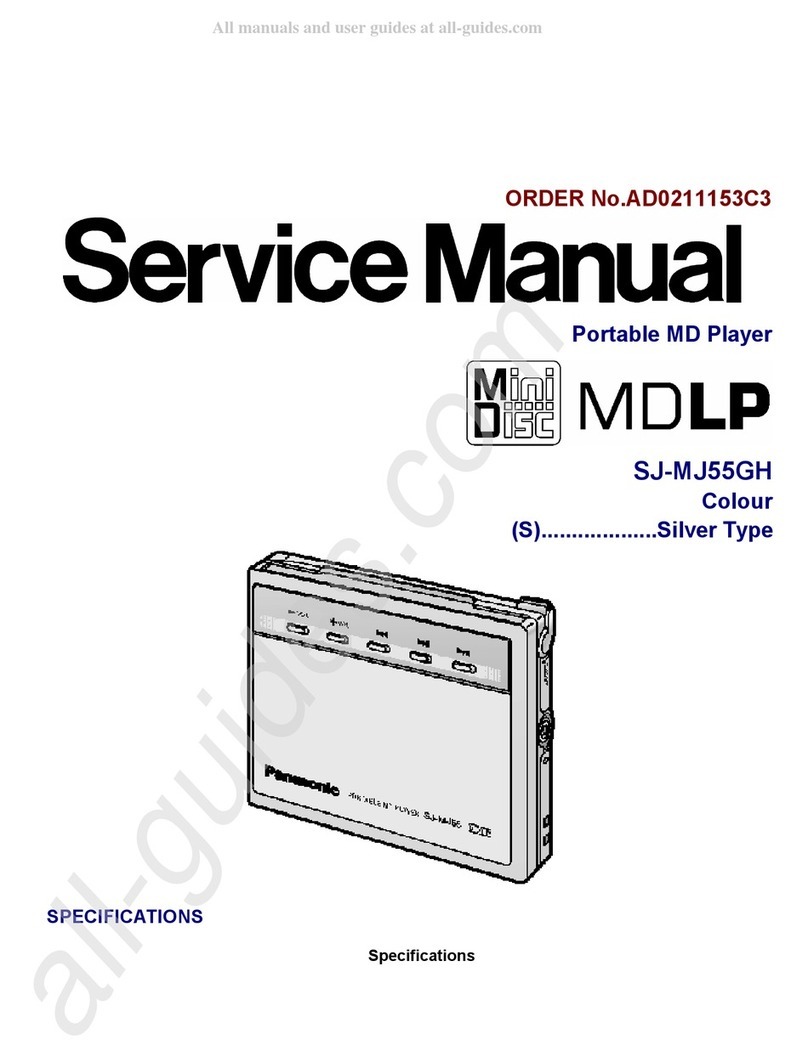

Solder bridge the test point TAP805 (TEST) on the MAIN

board (connect IC801 pin #£ to GND), and turn on the power.

– MAIN BOARD (Conductor side) –

Releasing theTest Mode

A test mode releasing method varies depending on the test mode

setting method.

1. When test mode was entered with key input, turn off the power.

2. When test mode was entered by shorting the test point, turn

off the power and open the solder bridge of TAP805 (TEST

MODE) on the MAIN board.

Operation of Setting onTest Mode

When the test mode is set, the LCD displays the following :

• The cycle - the above ROM version display nAll lit nAll

off - is repeated.

• When the PLAYMODE key is pressed and hold down, the dis-

play at that time is held so that display can be checked.

Test mode

Short:Test mode

Open: Normal mode

()

”

/

+

key

”

/

+

key

p

key

p

key

p

key

p

key

VOL

+ key

VOL

– key

(044 Start?)

Overall

adjustment

mode (044 Auto?)

Adjustment

mode

(044 Manu?) Servo mode

0 0 0

Audio mode

1 0 0

Power mode

3 0 0

VOL +/– keys

VOL

+/– keys

Display when test mode

is set

VOL

+/– keys

Displays of the LCD on the remote commander

are shown in parenthesis.

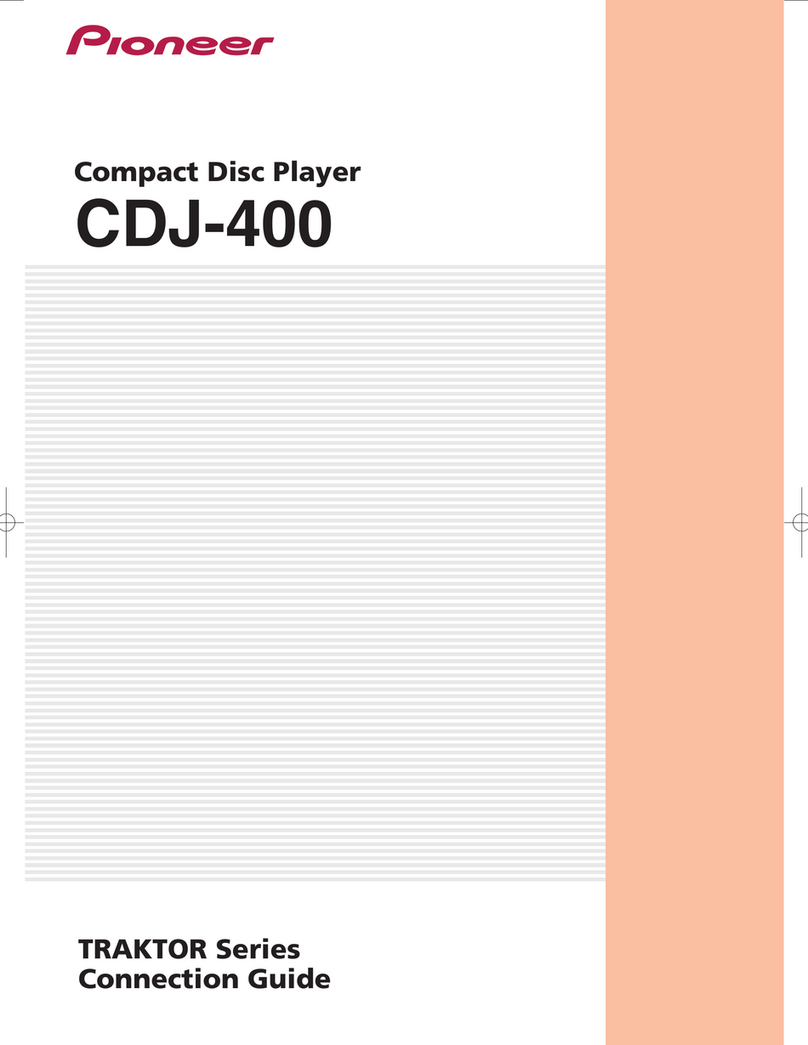

Configuration ofTest Mode

The test mode has the configuration given below.

Servo Mode

• Set the test mode, press the VOL – key and use the ”/+key

to set the servo mode.

• When the servo mode is set, use the +/”key and the =

key on the set to move the optical pick-up to the outer circum-

ference and to the inner circumference respectively.

• When entering another mode, refer to the configuration of test

mode.

1. Structure of Servo Mode

Servo mode

0 0 0

Offset adjustment

0 1 0

Laser power

adjustment

0 2 0

011

to

014

*

1

021

to

024

*

1

23

1

p

key

p

key

p

key

p

key

”

/

+

key

”

/

+

key

”

/

+

key

”

/

+

key

”

/

+

key

VOL

+/– keys

VOL

+/– keys

(See page 7.)

*

1 Repeatedly press

”

/

+

key

to change the mode.

(Refer to the following list

for a description of each

mode.)