Spectrum Digital TMS320F240 Use and care manual

TMS320F240

Evaluation Module

1998 DSP Development Systems

Reference

Technical

TMS320F240

Evaluation Module

Technical Reference

503279-0001 Rev. C

June 1998

SPECTRUM DIGITAL, INC.

10853 Rockley Road Houston, TX. 77099

Tel: 281/561-6952 Fax: 281/561-6037

[email protected] www.spectrumdigital.com

IMPORTANT NOTICE

Spectrum Digital, Inc. reserves the right to make changes to its products or to discontinue any

product or service without notice, and advises its customers to obtain the latest version of relevant

information to verify, before placing orders, that the information being relied on is current.

Spectrum Digital, Inc. warrants performance of its products and related software to current

specifications in accordance with Spectrum Digital’s standard warranty. Testing and other quality

control techniques are utilized to the extent deemed necessary to support this warranty.

Please be aware that the products described herein are not intended for use in life-support

appliances, devices, or systems. Spectrum Digital does not warrant nor is liable for the product

described herein to be used in other than a development environment.

Spectrum Digital, Inc. assumes no liability for applications assistance, customer product design,

software performance, or infringement of patents or services described herein. Nor does Spectrum

Digital warrant or represent any license, either express or implied, is granted under any patent right,

copyright, or other intellectual property right of Spectrum Digital, Inc. covering or relating to any

combination, machine, or process in which such Digital Signal Processing development products or

services might be or are used.

WARNING

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can

radiate radio frequency energy and has not been tested for compliance with the limits of computing

devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable

protection against radio frequency interference. Operation of this equipment in other environments

may cause interference with radio communications, in which case the user at his own expense will be

required to take whatever measures may be required to correct this interference.

TRADEMARKS

MS-DOS, MS-Windows, and Windows 95 are registered trademarks of Microsoft Corp.

Copyright © 1997,1998 Spectrum Digital, Inc.

Contents

1 Introduction to the TMS320F240 Evaluation Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

Provides you with a description of the TMS320F240 Evaluation Module, key features, and

board outline.

1.0 Overview of the TMS320F240 EVM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.1 Key Features of the TMS320F240 EVM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.2 Functional Overview of the TMS320F240 EVM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

2 TMS320F240 EVM Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Describes the operation of the EVM320F240. Information is

provided on the EVM’s various

interfaces.

2.0 The TMS320F240 EVM Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1 The TMS320F240 EVM Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1.1 Power Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.2 TMS320C2XX Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.2.1 Program Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.2.2 Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.2.3 I/O Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.3 Onboard UART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.4 Oscillator Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.5 Digital to Analog Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.6 Expansion Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.6.1 TMS320F240 EVM Expansion Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.6.1.1 Expansion I/O Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.6.1.2 Expansion Analog Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

2.6.1.3 Expansion Address and Data Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.6.1.4 Expansion Control Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.7 JTAG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.8 On-Chip Asychronous Serial Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2.9 Onboard Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

2.10 TMS320F240 EVM Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2.10.1 Jumper JP1, Enable/Disable Flash Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

2.10.2 Jumper JP2, Enable/Disable Internal ROM/FLASH . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

2.10.3 Jumper JP3, Oscillator Source Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

2.10.4 Jumper JP4, Enable/Disable RTS to BIO-/IOPC3 . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

2.10.5 Jumper JP5, Enable/Disable RXD to SCIRXD/IO . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.10.6 Jumper JP6, VREFHI Source Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.10.7 Jumper JP7, VREFLO Source Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.10.8 Jumper JP8, UART Interrupt Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.10.9 Jumper JP9, A15 Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

2.10.10 Jumper JP10, Not Used . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

2.10.11 Jumper JP11, Enable/Disable Host Reset via DTR- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

2.10.12 Jumper JP12, Enable/Disable Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

2.10.13 Jumper JP13, Not Used . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

2.10.14 Jumper JP14, Enable/Disable Onboard FLASH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

2.10.15 Jumper JP15, Onboard UART CTS Routing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2.11 LEDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2.12 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . 2-25

2.13 Test Point . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

A TMS320F240 EVM PAL Equations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Lists the PAL equations that are used on the TMS320F240 EVM

A.1 Memory Decode PAL Equations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

A.2 Decode PAL Equations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-8

A.3 UART Control PAL Equations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

B TMS320F240 Schematics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

Contains the schematics for the TMS320F240 EVM

C TL16C550 Data Sheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

Contains the technical information for the TL16C550

D MP7680 DAC Programming Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-1

Contains information regarding the programming of the MP7680 Digital-to-Analog Converter.

D.1 MP7680 Digital-to Analog Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-2

D.2 MP7680 Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-3

D.3 MP7680 Calibration Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-3

About This Manual

This document describes the board level operations of the TMS320F240 evaluation

module (EVM). The EVM is based on the Texas Instruments TMS320F240 Digital

Signal Processor.

The TMS320F240 EVM is a table top card to allow engineers and software developers

to evaluate certain characteristics of the TMS320F240 DSP to determine if the

processor meets the designers application requirements. Evaluators can create

software to execute onboard or expand the system in a variety of ways.

Notational Conventions

This document uses the following conventions.

The TMS320F240 will sometimes be referred to as the F240 or C24X.

Program listings, program examples, and interactive displays are shown is a special

italic typeface. Here is a sample program listing.

equations

!rd = XXXXXXXXXXX;

Information About Cautions

This book may contain cautions.

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software,

or hardware, or other equipment. The information in a caution is provided for your

protection. Please read each caution carefully.

Related Documents

Texas Instruments TMS320F240 Users Guide

Texas Instruments TMS320 Fixed Point Assembly Language Users Guide

Texas Instruments TMS320 Fixed Point C Language Users Guide

Texas Instruments TMS320 Fixed Point C Source Debugger Users Guide

1-1

Chapter 1

Introduction to the TMS320F240

Evaluation Module

This chapter provides you with a description of the TMS32F240 Evaluation

Module along with the key features and a block diagram of the circuit

board.

Topic Page

1.0 Overview of the TMS320F240 EVM 1-2

1.1 Key Features of the TMS320F240 EVM 1-2

1.2 Functional Overview of the TMS320F240 EVM 1-3

Spectrum Digital, Inc

1-2

TMS320F240 Evaluation Module Technical Reference

1.0 Overview of the TMS320F240 EVM

The TMS320F240 evaluation module(EVM) is a stand-alone card that lets evaluators

examine certain characteristics of the F240 digital signal processor(DSP) to determine

if this DSP meets their application requirements. Furthermore, the module is an

excellent platform to develop and run software on the F240 family of processors.

The F240 EVM is shipped with a TMS320F240 DSP however other family members

can be placed in the on board socket as they become available. The EVM allows full

speed verification of F240 code. With 544 words of onchip data memory, 128K words of

onboard memory, flash rom, on chip UART, on board UART, and an MP7680 Digital

to Analog Converter, the board can solve a variety of problems as shipped. Four

expansion connectors are provided to interface to any necessary evaluation circuitry

not provided on the as shipped configuration.

To simplify code develop and shorten debugging time a number of user interfaces are

available.

1.1 Key Features of the TMS320F240 EVM

The F240 EVM has the following features:

• F240 operating at 20 MIPS with 128K words of zero wait state memory

• MP7680 Four(4) Channel Digital to Analog converter

• On Chip UART with RS232 Drivers

• 32K words of onchip Flash ROM

• Second on board UART

• 32K words of on board Flash ROM

• 4 Expansion Connectors (data, address, I/O, and control)

• On board IEEE 1149.1 JTAG Connection for Optional Emulation

• 5 Volt Only Operation

Spectrum Digital, Inc

1-3

1.2 Functional Overview of the TMS320F240 EVM

Figure 1-1 shows a block diagram of the basic configuration for the F240 EVM. The

major interfaces of the EVM include the target ram and rom interface, target UART,

analog interface, and expansion interface.

The F240 interfaces to 128K Words of zero wait-state static memory. An external I/O

interface supports 65,000 parallel I/O ports and optional high speed synchronous serial

port. A Flash Boot Rom can be mapped into the memory interface.

JTAG UART

ANALOG

DATA

ADDRESS

CONTROL PWM/IO

I/O

TMS320F240

JTAG P5

TL16C550

UART

FLASH

EPROM

32K x 16

SRAM

128K x 16

MP7680

D/A

A

N

A

L

O

G

E

X

P

A

N

S

I

O

N

P

2

I

/

O

E

X

P

A

N

S

I

O

N

P

1

S

E

R

I

A

L

P

6

A

D

D

R

E

S

S

/

D

A

T

A

P

3

C

O

N

T

R

O

L

P

4

S

E

R

I

A

L

P

7

Figure 1-1 BLOCK DIAGRAM TMS320F240 EVM

Spectrum Digital, Inc

1-4

TMS320F240 Evaluation Module Technical Reference

2-1

Chapter 2

Operation of the TMS320F240

Evaluation Module

This chapter describes the operation of the TMS32F240 Evaluation

Module along with the key interfaces and an outline of the circuit board.

Topic Page

2.0 The TMS320F240 EVM Operation 2-3

2.1 The TMS320F240 EVM Board 2-3

2.1.1 Power Connector 2-4

2.2 TMS320F240 Memory Interface 2-4

2.2.1 Program Memory 2-5

2.2.2 Data Memory 2-8

2.2.3 I/O Space 2-9

2.3 Onboard UART 2-9

2.4 Oscillator Selection 2-9

2.5 Digital to Analog Conversion 2-10

2.6 Expansion Bus 2-10

2.6.1 TMS320F240 EVM Expansion Connector 2-10

2.6.1.1 Expansion I/O Connector 2-11

2.6.1.2 Expansion Analog Connector 2-12

2.6.1.3 Expansion Address and Data Connector 2-13

2.6.1.4 Expansion Control Connector 2-14

2.7 JTAG Interface 2-15

2.8 On-Chip Asynchronous Serial Port 2-16

2.9 Onboard Serial Interface 2-17

Spectrum Digital, Inc

2-2

TMS320F240 Evaluation Module Technical Reference

Topic Page

2.10 TMS320F240 EVM Jumpers 2-18

2.10.1 Jumper JP1, Enable/Disable Flash Programming 2-19

2.10.2 Jumper JP2, Enable/Disable Internal ROM/FLASH 2-19

2.10.3 Jumper JP3, Oscillator Source Select 2-20

2.10.4 Jumper JP4, Enable/Disable RTS to BIO-/IOPC3 2-20

2.10.5 Jumper JP5, Enable/Disable RXD to SCIRXD/IO 2-21

2.10.6 Jumper JP6, VREFHI Source Select 2-21

2.10.7 Jumper JP7, VREFLO Source Select 2-22

2.10.8 Jumper JP8, UART Interrupt Select 2-22

2.10.9 Jumper JP9, A15 Select 2-23

2.10.10 Jumper JP10, Not Used 2-23

2.10.11 Jumper JP11, Enable/Disable Host Reset via DTR- 2-23

2.10.12 Jumper JP12, Enable/Disable Memory Mapping 2-24

2.10.13 Jumper JP13, Not Used 2-24

2.10.14 Jumper JP14, Enable/Disable Onboard FLASH 2-24

2.10.15 Jumper JP15, Onboard UART CTS Routing Jumper 2-25

2.11 LEDS 2-25

2.12 Resets 2-25

2.13 Test Point 2-25

Spectrum Digital, Inc

2-3

2.0 The TMS320F240 EVM Operation

This chapter describes the F240 Evaluation module, its key components, and how they

operate. It also provides information on the EVM’s various interfaces.The F240 EVM

consists of six major blocks of logic.

• F240 external memory

• Analog Interface

• On Chip Serial Interface

• On board Serial I/O interface

• Expansion interface

• JTAG Interface

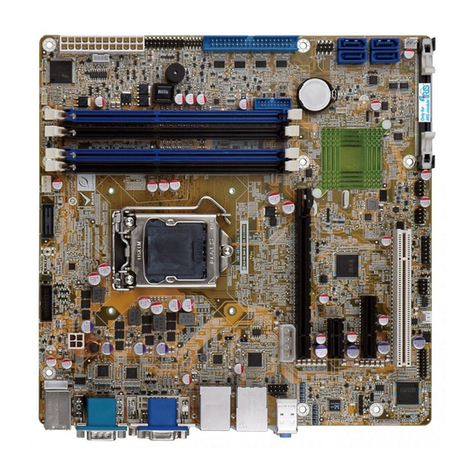

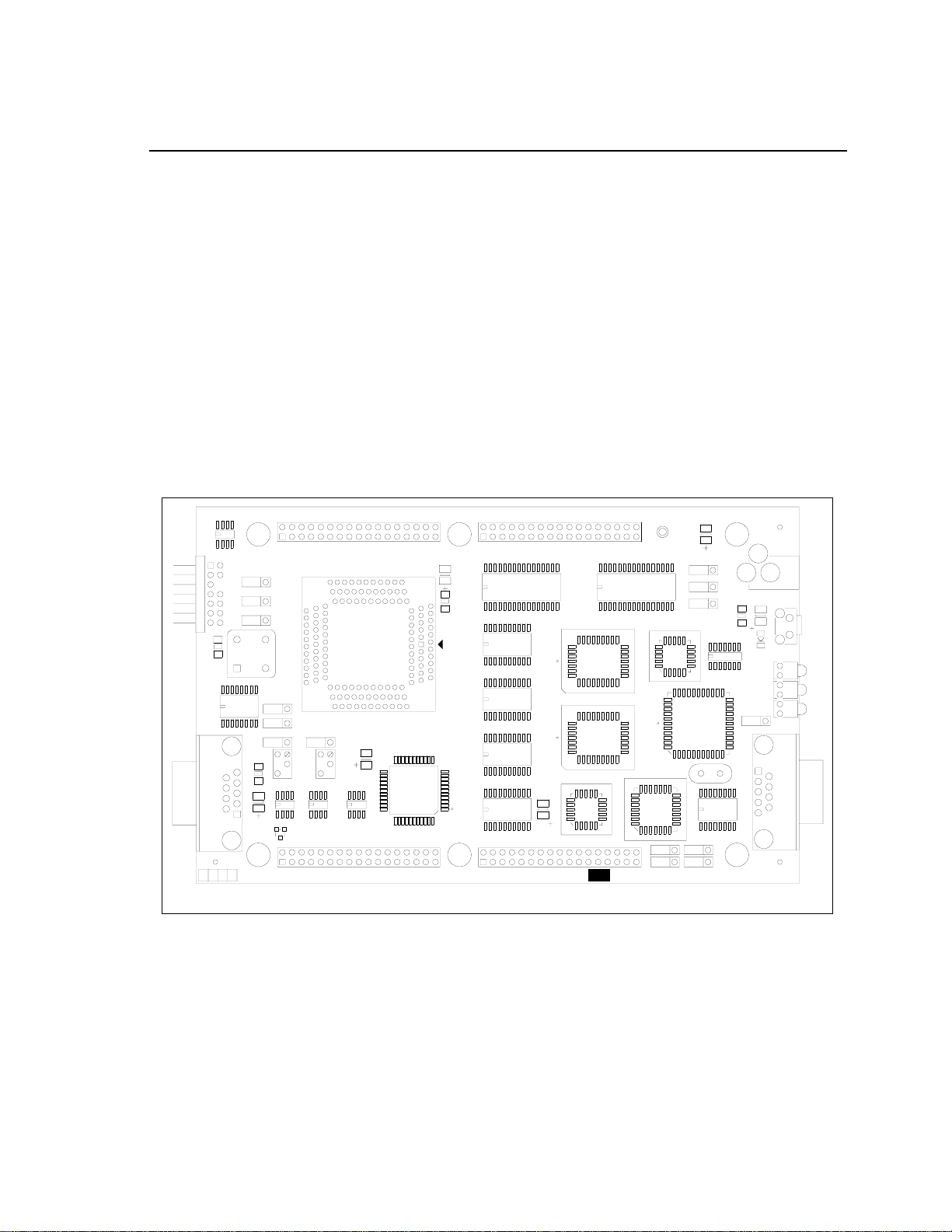

2.1 The TMS320F240 EVM Board

The F240 EVM is a 3U sized board which is powered by an external 5 Volt only power

supply. Figure 2-1 shows the layout of the F240 EVM.

Figure 2-1 TMS32F240 EVM

P5

11

11

1

1

1

1

1

1

TP1

D2

C6

JP4

JP5

C3 JP8

JP9

JP10

J1

L1 U2

P6

C4

C5

L2

L4

L3

U18

Y1

JP14

JP12

U12

U10

U20

U16

U19

U15

U22

R34

+5V

R23

C1

U3

P4P2

P1 P3

P7

I/O ADDRESS/DATA

ANALOG CONTROL

U5 U7

SW1

U4

U9 U14

U21

U8

11

11

1

ASSY 503270 REV

TMS320F240 EVM

C2

DS3

DS2

DS1

SPECTRUM DIGITAL

INCORPORATED

PWB 503271 REV B

U13 U17

U6

D1

JP7

JP6

U11

JP2

JP3

JP1

JP13

JP11

U1

1

JP15

Spectrum Digital, Inc

2-4

TMS320F240 Evaluation Module Technical Reference

2.1.1 Power Connector

The F240 is powered by a 5 Volt only power supply which is available with the module.

The board requires 750 milliamps. The power is supplied via 2 millimeter jack J1. If

expansion boards are connected to the module a higher amperage power supply may

be necessary.

2.2 TMS320F240 Memory Interface

The EVM includes 64k Words of zero wait-state program ram memory and 64k words

of zero wait-state data ram memory, providing a total of 128 k words of off chip static

ram. The board also features 2 sockets for flash rom.

It is important to remember that internal memory has a higher precedence than the

external memory. For more information on the memory in the device populated in your

EVM card please refer to Texas Instruments TMS320F240 Users Guide. Futhermore,

it is important to take into account that external memory is affected by wait-states. Wait

state generation for off-chip memory space (data, program, or I/O) is done with the

Wait State Generation Register(WSGR). To obtain zero waitstate off-chip memory

bits in the WSGR must be appropriately programmed. The board powers up with 1

wait-state. The EVM board does not generate wait states via the ready signal for

external program and data memory accesses.

External memory decode is done via U19 a GAL20V8. The generic array device selects

the RAM, FLASH ROM, or on board peripherals. The equations for the GAL are

included in Appendix A. The figure below shows a zero wait state program space

memory read followed by a data space memory write.

Spectrum Digital, Inc

2-5

The external Flash ROM is mapped into the program space. Note that this memory

requires multiple wait states. The main purpose of this memory is to allow for the boot

loading of programs without the need of programming the processors internal flash.

2.2.1 Program Memory

There are several configurations for program memory. The selection of these

configurations is done by the position of jumpers JP2 and JP14. If JP2 is in the 2-3

position then the DSP is in microcomputer mode and the internal memory is enabled

from 0x0000 to 0x3fff. If JP2 is in position 1-2 then the internal FLASH/ROM is disabled

and this address range is available to external memory.

External program memory is controlled by jumper JP14. When JP14 is configured in

the 1-2 position external RAM is enabled from 0x0000-0xffff. Remember internal

memory takes precedence over external memory. If JP14 is in position 2-3 the external

FLASH is enabled from 0x000-0x7fff. If enabled it is possible to select and deselect the

external FLASH memory by writing to bits D3 and D2 in the UART’S MCR register. For

instance you can set the configuration to Out2 = 0 and Out1 = 1 to copy the program

from FLASH to RAM at the same address.

CLKOUT

ADDRESS

DATA

R/W

PS-

DS-

STRB-

RAMOE-

Zero Wait State Memory Timing

READ WRITE

RAMWE-

Spectrum Digital, Inc

2-6

TMS320F240 Evaluation Module Technical Reference

* Power up configuration

Note: The bits in the MCR register are inverted from

what appears on the output pins.

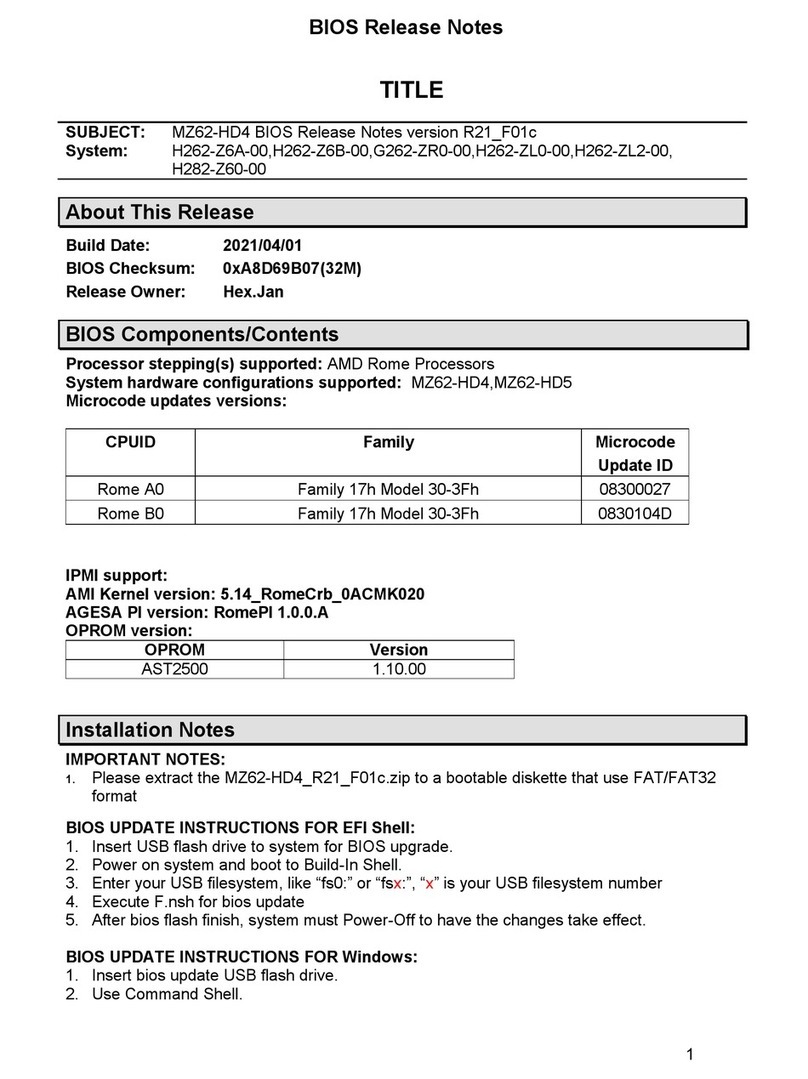

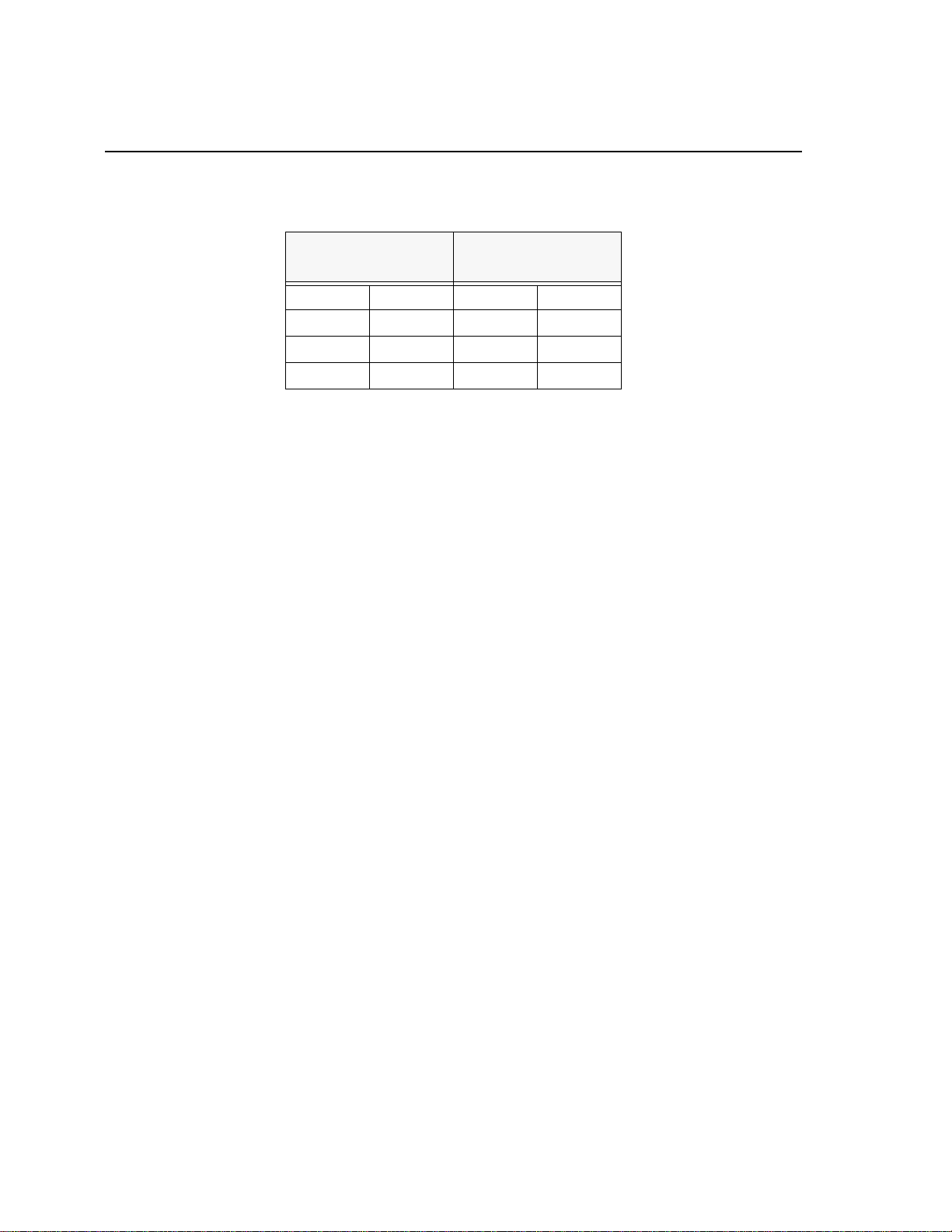

Table 1: FLASH/RAM CONFIGURATION

UART MCR BITs

D3(Out2) D2(Out1) FUNCTION

READ WRITE

00FLASH*

0 1 FLASH RAM

1 0 RAM FLASH

11RAMRAM

Spectrum Digital, Inc

2-7

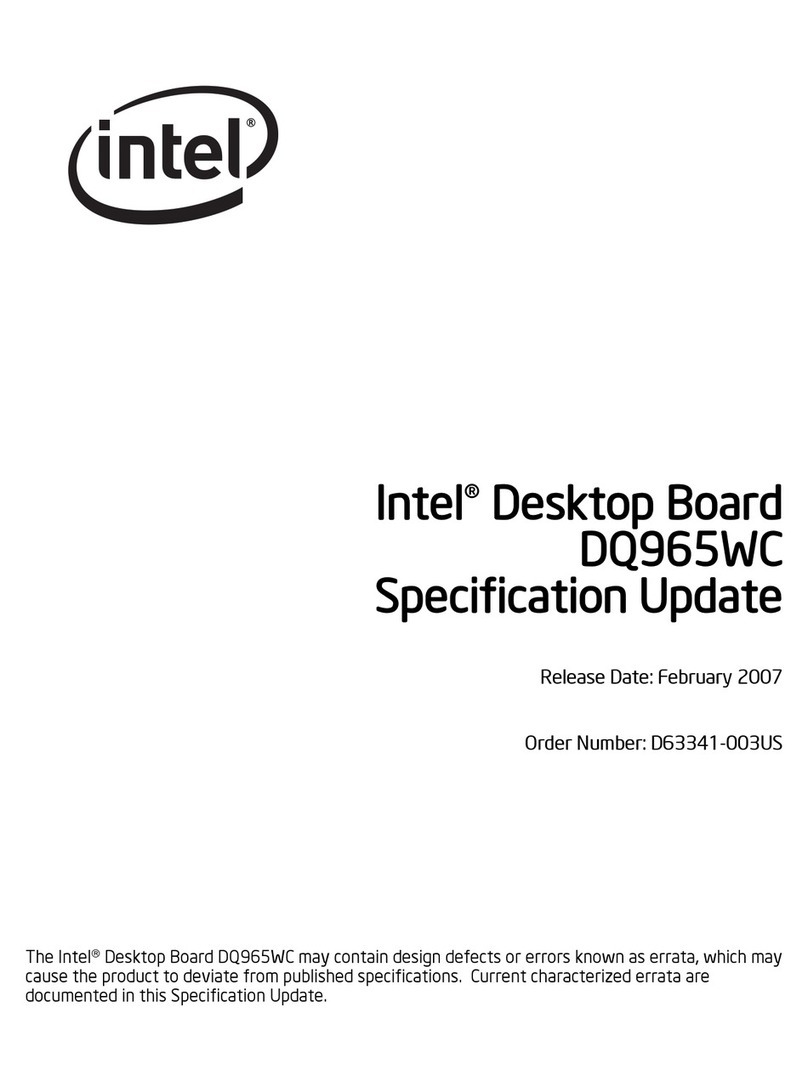

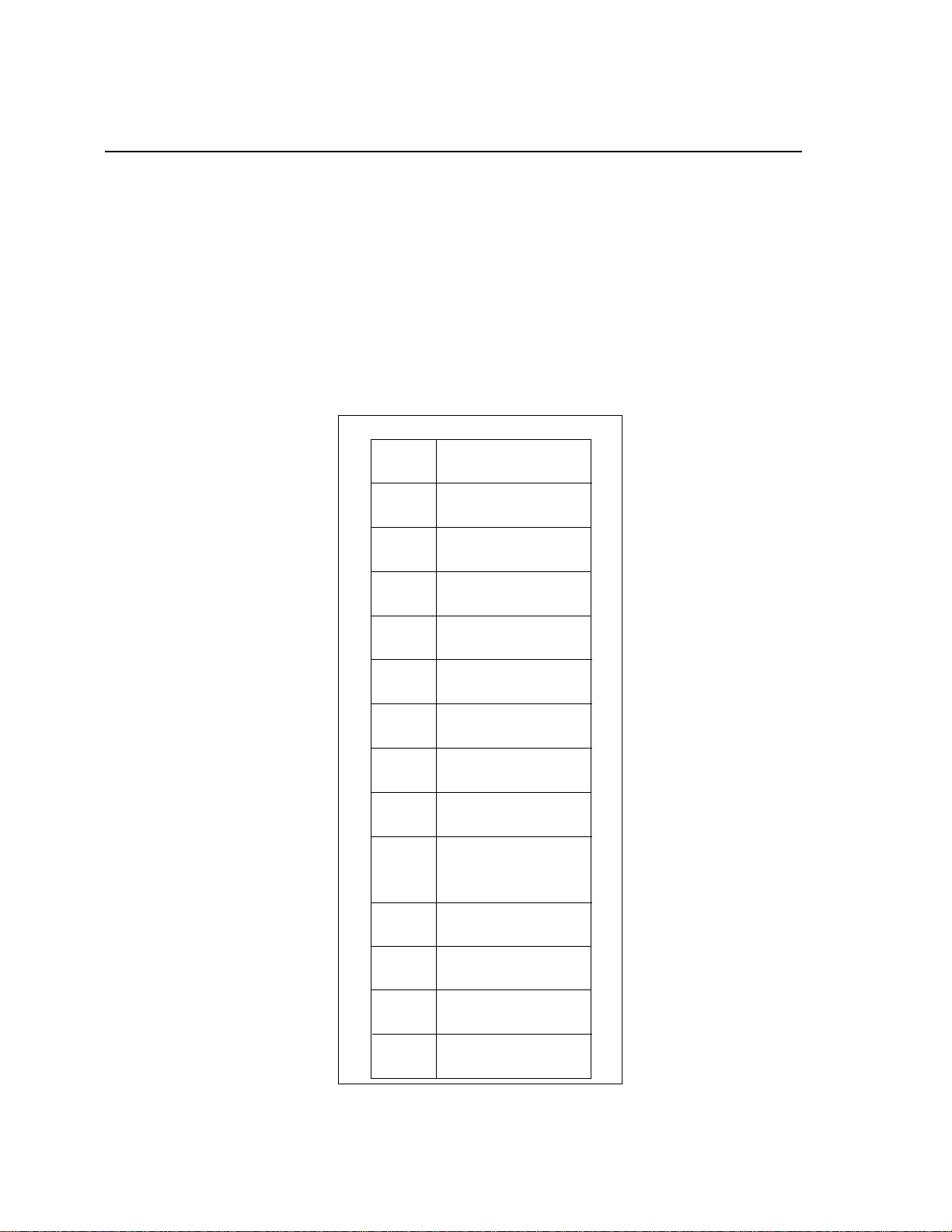

Shown below are the four program memory configurations:

Hex

Program Space

MP/MC- = 0, JP2(2-3)

Microcomputer Mode

External FLASH, JP14(2-3)

Program Space

Program Space

Program Space

MP/MC- = 1, JP2(1-2)

MP/MC- = 0, JP2(2-3)

MP/MC- = 1, JP2(1-2)

Microprocessor Mode

Microcomputer ModeMicroprocessor Mode

External FLASH, JP14(2-3)

No external FLASH, JP14(1-2) No external FLASH, JP14(1-2)

Hex

Hex 0000

003F

0040

3FFF

4000

7FFF

8000

FDFF

FE00

FEFF

FF00

FFFF

Interrupts

(On-chip)

On-chip ROM

(Flash EEPROM)

(8x2K Segments)

(Seg 0 = Boot Seg

@ 0h-07FFh by

BOOTPROT pin)

External FLASH

External RAM

On-Chip DARAM

B0 (CNF = 1)

External (CNF = 0)

External (CNF = 0)

B0’ (CNF = 1)

On-Chip DARAM

0000

003F

003F

0000

0040

0040

7FFF

FE00

FE00

FEFF

FEFF

FF00

FF00

FFFF

FFFF

Interrupts

(On-chip)

External FLASH

External RAM

On-Chip DARAM

B0 (CNF = 1)

External (CNF = 0)

On-Chip DARAM

B0’ (CNF = 1)

External (CNF = 0)

8000

FDFF

FDFF

Interrupts Interrupts

External (CNF = 0) External (CNF = 0)

B0’ (CNF = 1)

B0’ (CNF = 1)

On-Chip DARAM

On-Chip DARAMOn-Chip DARAM

On-Chip DARAM

External (CNF = 0) External (CNF = 0)

B0 (CNF = 1)

B0 (CNF = 1)

0000

003F

0040

FDFF

FE00

FEFF

FF00

FFFF

(On-chip)

(On-chip)

External RAM

External RAM

4000

3FFF BOOTPROT pin)

@ 0h-07FFh by

(Seg 0 = Boot Seg

(8x2K Segments)

(Flash EEPROM)

On-chip ROM

RAM

Spectrum Digital, Inc

2-8

TMS320F240 Evaluation Module Technical Reference

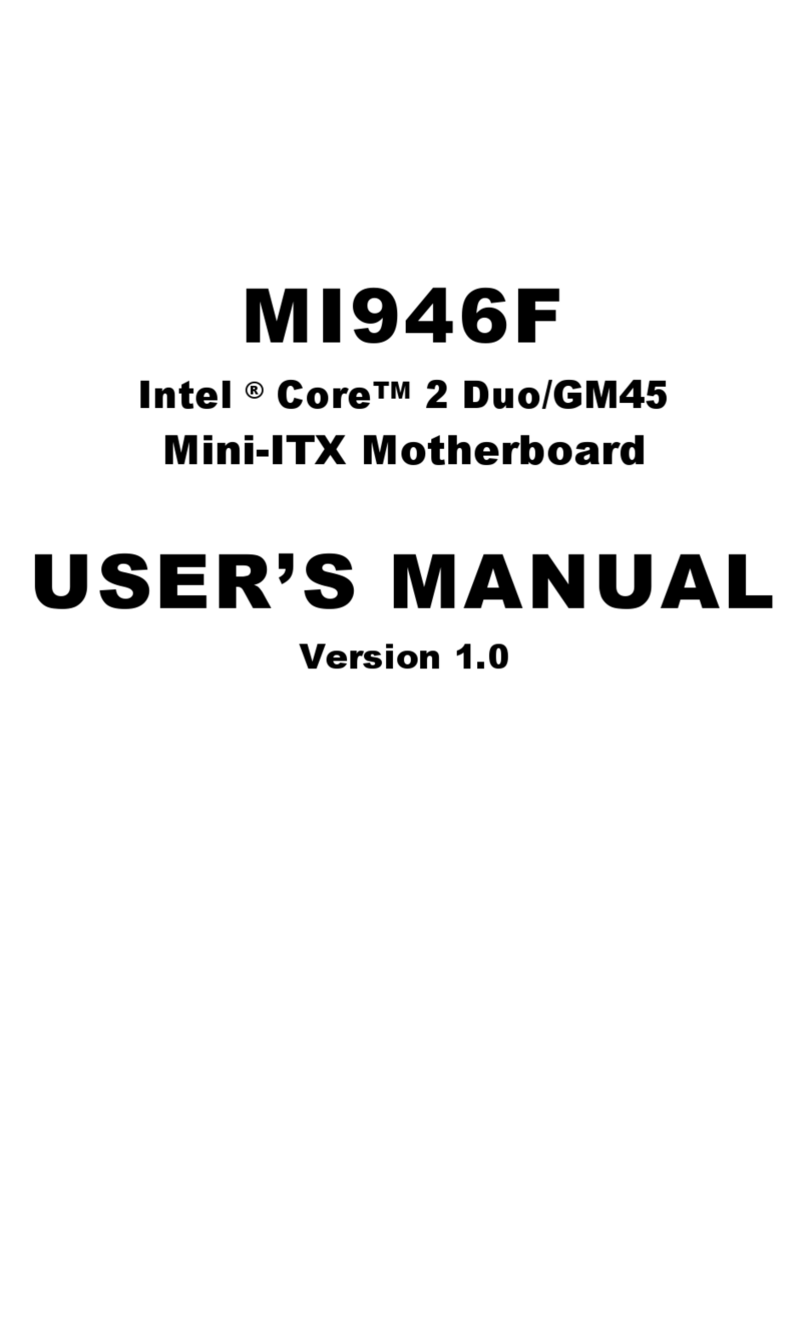

2.2.2 Data Memory

The two data memory configurations are configured by jumper JP12. Configured in the

1-2 position the external RAM is enabled from 0x8000-0xffff. Loading the GREG

register will disable all or part the external memory, depending on the value, and allow

devices connected to the expansion bus to be accessed.

When JP12 is configured in the 2-3 position and jumper JP9 is also configured in the

2-3 position then the setting of the GREG register is used to remap the unused 32K of

RAM into the memory map. In this mode BR- is used to invert address A15. In other

words if BR- is inactive address 0x8000 would map to address 0x8000 in the RAM. If

BR- was active then address 0x8000 would be mapped to 0x0000 in the data RAM.

Hex Data Space

0000

005F

0060

007F

0080

00FF

0100

01FF

0200

02FF

0300

03FF

0400

04FF

0500

07FF

0800

6FFF

7000

73FF

7400

743F

7440

77FF

7800

7FFF

8000

FFFF

Memory-Mapped

Register and

Reserved

Reserved

Reserved

Reserved

Illegal

Illegal

External RAM

Peripheral Memory-

On-Chip

DARAM B2

On-Chip DARAM

B0 (CNF = 0)

Reserved (CNF = 1)

On-Chip DARAM

B0’ (CNF = 0)

Reserved (CNF = 1)

On-Chip

DARAM B1

On-Chip

DARAM B1’

Mapped Registers

(System, ADC, SCI,

SPI, I/O, Interrupts)

Peripheral Memory-

Mapped Registers

(Event Manager)

Spectrum Digital, Inc

2-9

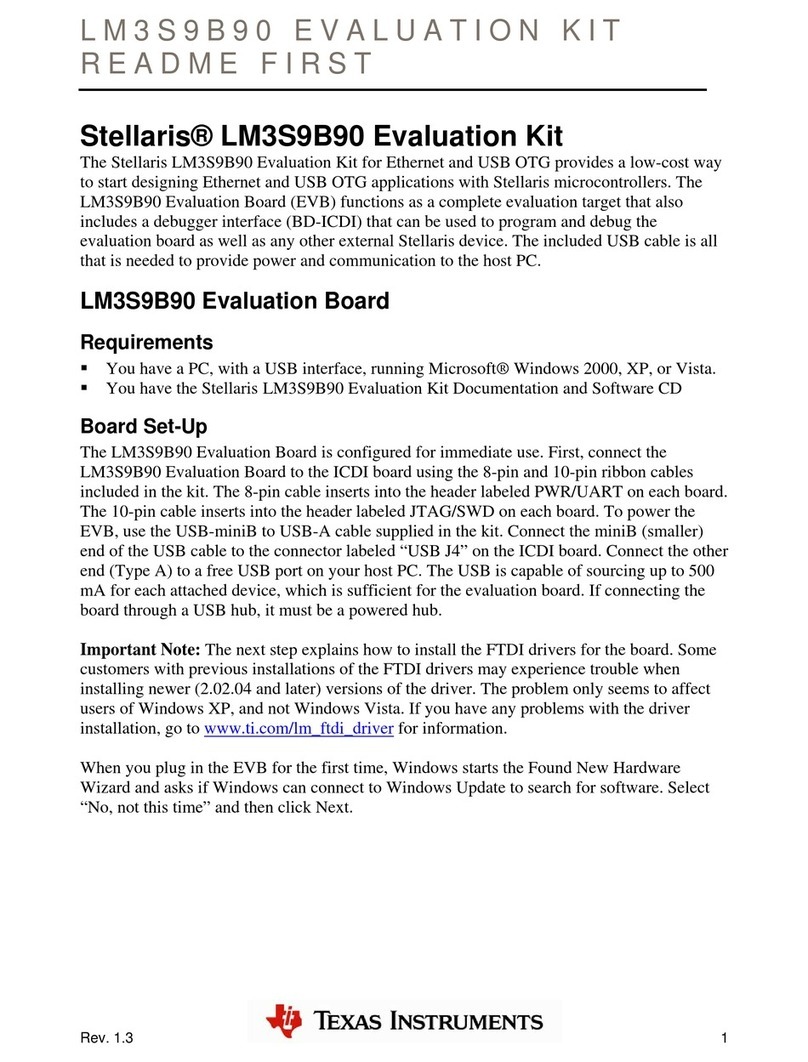

2.2.3 I/O Space

The I/O map for the TMS320F240 EVM is shown below:

2.3 Onboard UART

The TMS320F240 EVM has a TL16C550 UART mapped into the I/O space of the F240

at locations 0x0010 - 0x0018. The UART allows users to use this resource for data

logging, code debugging or other application features. Appendix C contains the

programming information for the TL16C550 device.

2.4 Oscillator Selection

The TMS320F240 EVM is equipped with a 10 Megahertz oscillator. When the

processor resets the PLL Clock Module defaults to CLKIN/2 yielding a 5 Mhz clkout.

The user should refer to the “PLL Clock Module” section in the TMS320F240 User’s

guide for valid clock configurations.

Hex

0000

0004

0005

000F

0010

0018

0019

FEFF

I/O Space

D/A Converter

Reserved

Off-Chip UART

External

Reserved

FF00

FFFF

Spectrum Digital, Inc

2-10

TMS320F240 Evaluation Module Technical Reference

2.5 Digital to Analog Converter

The TMS320F240 EVM provides four(4) 12-bit D/A channels. The output is from 0 to 5

volts DC. The converter is mapped into I/O address space 0x0000 to 0x0004. Locations

0x0000 through 0x0003 are used for the data holding registers for channels 1-4

respectively. I/O address 0x0004 is used to transfer values in the holding registers to

the converters. For instance you can write to the 4 holding registers and transfer all 4 to

the converters at the same time. Information about programming this converter can be

found in appendix D.

2.6 Expansion Bus

The TMS320F240 EVM has an expansion bus which brings out all of the signals from

the DSP. This expansion bus allows the user to design custom circuitry to be used with

his application without having to design a CPU card. In addition this interface is used by

Spectrum Digital for all of its add-on modules.

2.6.1 TMS320F240 EVM Expansion Connector

Expansion boards interface to the TMS320F240 EVM via an expansion bus.

This expansion bus is divided into 4 double row header connectors. This section

contains the signal definitions and pin numbers for each of the connectors.

Table 2: DAC I/O Addresses

I/O Address Channel #

0x0000 1

0x0001 2

0x0002 3

0x0003 4

0x0004 Transfer

Table of contents

Other Spectrum Digital Motherboard manuals

Spectrum Digital

Spectrum Digital eZdsp F2804 Series Use and care manual

Spectrum Digital

Spectrum Digital eZdsp R2812 USB Use and care manual

Spectrum Digital

Spectrum Digital TMS320LF2407 Use and care manual

Spectrum Digital

Spectrum Digital TMS320DM6437 Use and care manual

Spectrum Digital

Spectrum Digital TMS320C5517 Use and care manual

Spectrum Digital

Spectrum Digital TMS320DM6467 Use and care manual

Spectrum Digital

Spectrum Digital TMS320VC5505 Use and care manual

Spectrum Digital

Spectrum Digital XDS560v2 Use and care manual

Spectrum Digital

Spectrum Digital TMS320VC5509A EVM PLUS Use and care manual

Spectrum Digital

Spectrum Digital eZdsp F28 Series Instruction Manual