TCP460 User Manual Issue 1.1 Page 2 of 32

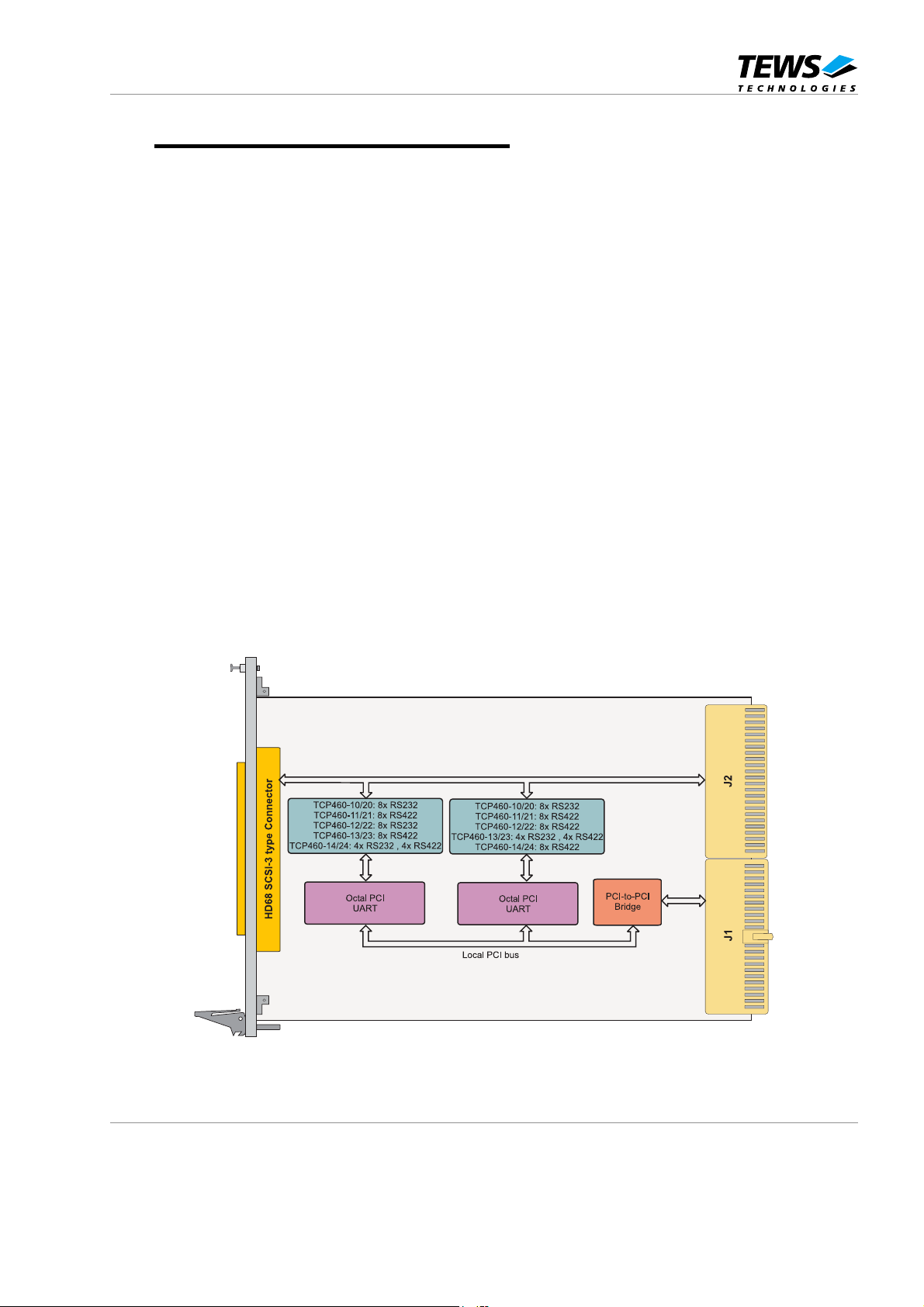

TCP460-10

16 channel RS232 asynchronous serial interface,

front panel I/O

TCP460-11

16 channel RS422 asynchronous serial interface,

front panel I/O

TCP460-12

8 channel RS232, 8 channel RS422

asynchronous serial interface, front panel I/O

TCP460-13

12 channel RS232, 4 channel RS422

asynchronous serial interface, front panel I/O

TCP460-14

4 channel RS232, 12 channel RS422

asynchronous serial interface, front panel I/O

TCP460-20

16 channel RS232 asynchronous serial interface,

front panel and J2 I/O

TCP460-21

16 channel RS422 asynchronous serial interface,

front panel and J2 I/O

TCP460-22

8 channel RS232, 8 channel RS422

asynchronous serial interface, front panel and

J2 I/O

TCP460-23

12 channel RS232, 4 channel RS422

asynchronous serial interface, front panel and

J2 I/O

TCP460-24

4 channel RS232, 12 channel RS422

asynchronous serial interface, front panel and

J2 I/O

This document contains information, which is

proprietary to TEWS TECHNOLOGIES GmbH. Any

reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any

effort to ensure that this manual is accurate and

complete. However TEWS TECHNOLOGIES GmbH

reserves the right to change the product described

in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any

damage arising out of the application or use of the

device described herein.

Style Conventions

Hexadecimal characters are specified with prefix 0x,

i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ‚Active Low’ is

represented by the signal name with # following, i.e.

IP_RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

2005 by TEWS TECHNOLOGIES GmbH

Issue Description Date

1.0 First Issue June 2005

1.1 Configuration EEPROM data & Pinout clarification October 2005