7

TAS5733L

www.ti.com

SLASE77A –MARCH 2016–REVISED MARCH 2016

Product Folder Links: TAS5733L

Submit Documentation FeedbackCopyright © 2016, Texas Instruments Incorporated

(1) This does not include bond-wire or pin resistance.

6.6 Speaker Amplifier Characteristics

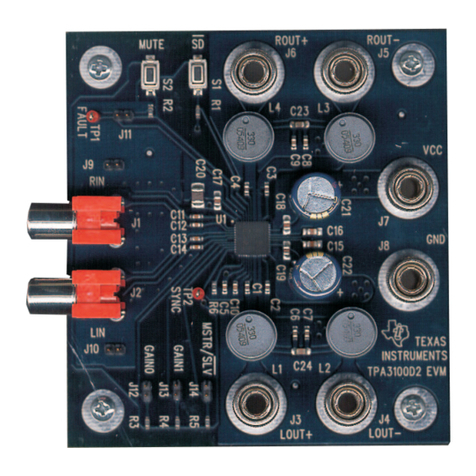

PVDD = 12 V, BTL BD mode, AVDD = DVDD = 3.3 V, fS= 48 KHz, RL= 8 Ω, audio frequency = 1 kHz, AES17 filter, fPWM =

384 kHz, TA= 25°C (unless otherwise specified). All performance is in accordance with recommended operating conditions

and as tested on the TAS5733L EVM.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

POPower output per channel

PVDD = 12 V, 10% THD, 1-kHz input signal 10

W

PVDD = 12 V, 7% THD, 1-kHz input signal 9

PVDD = 12 V, 1% THD, 1-kHz input signal 7.5

PVDD = 13.2 V, 10% THD, 1-kHz input signal 12

PVDD = 13.2 V, 7% THD, 1-kHz input signal 11

PVDD = 13.2 V, 1% THD, 1-kHz input signal 9

THD+N Total harmonic distortion +

noise PVDD = 12 V, PO= 1 W 0.25 %

PVDD = 13.2 V, PO= 1 W 0.3

VnOutput integrated noise (rms) A-weighted 30 μV

Crosstalk PO= 1 W, f = 1 kHz (BD Mode), PVDD = 12 V –79 dB

PO=1 W, f = 1 kHz (AD Mode), PVDD = 12 V –62 dB

Output switching frequency 11.025, 22.05, 44.1-kHz data rate ±2% 288 kHz

48, 24, 12, 8, 16, 32-kHz data rate ±2% 384

IPVDD Supply current No load (PVDD) Normal mode 16 25 mA

Reset (RST = low, PDN = high) 3 8

rDS(on)(1)

Drain-to-source resistance,

low side TJ= 25°C, includes metallization resistance 120 mΩ

Drain-to-source resistance,

high side TJ= 25°C, includes metallization resistance 120

RPD Internal pulldown resistor at

the output of each half-bridge Connected when drivers are in the high-impedance

state to provide bootstrap capacitor charge. 3 kΩ

6.7 Protection Characteristics

TA= 25°, PVDD_x = 12 V, DVDD = AVDD = 3.3 V, RL= 8 Ω, BTL BD mode, fS= 48 kHz (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Vuvp(fall) Undervoltage protection limit PVDD falling 5.4 V

Vuvp(rise) Undervoltage protection limit PVDD rising 5.8 V

OTE Overtemperature error 150 °C

IOC Overcurrent limit protection 4 A

IOCT Overcurrent response time 150 ns

(1) For clocks related to the serial audio port, please see Serial Audio Port Timing Requirements.

6.8 Master Clock Characteristics(1)

PVDD = 12 V, BTL BD mode, AVDD = DVDD = 3.3 V, fS= 48 kHz, RL= 8 Ω, audio frequency = 1 kHz, AES17 filter, fPWM =

384 kHz, TA= 25°C (unless otherwise specified). All performance is in accordance with recommended operating conditions

(unless otherwise specified).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

PLL INPUT PARAMETERS

fMCLKI MCLK frequency 2.8224 24.576 MHz

MCLK duty cycle 40% 50% 60%

tr/ tf(MCLK) Rise/fall time for MCLK 5 ns