Application Note

AM263x Hardware Design Guide

ABSTRACT

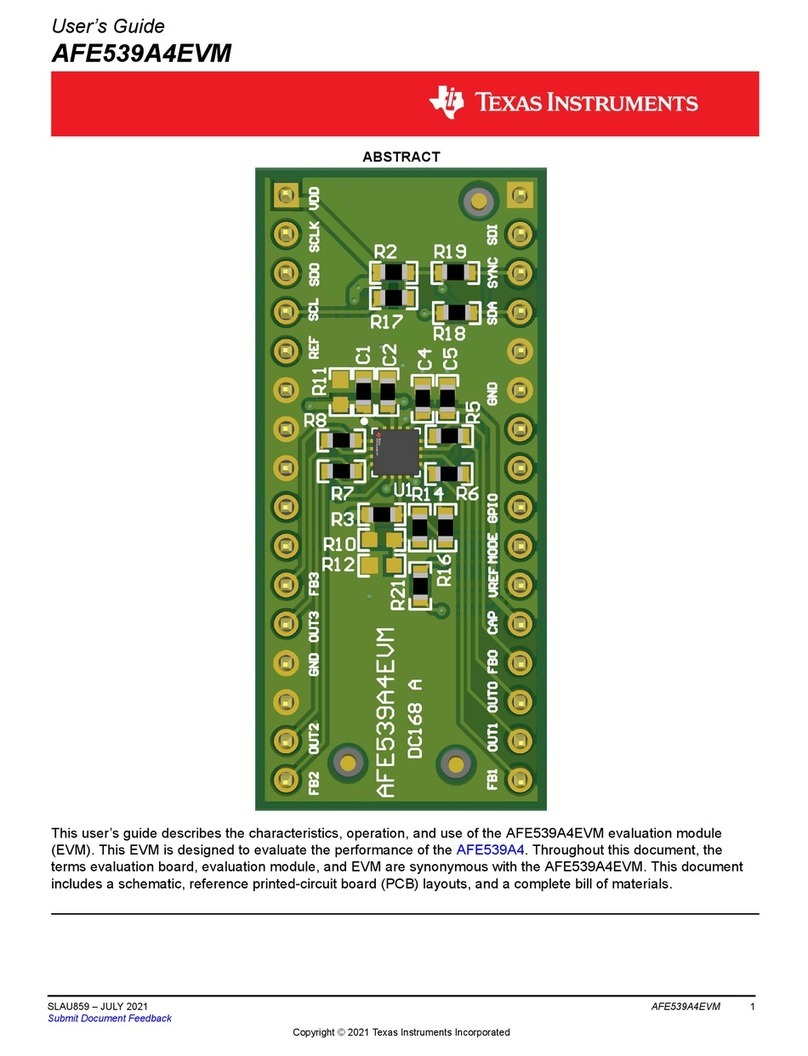

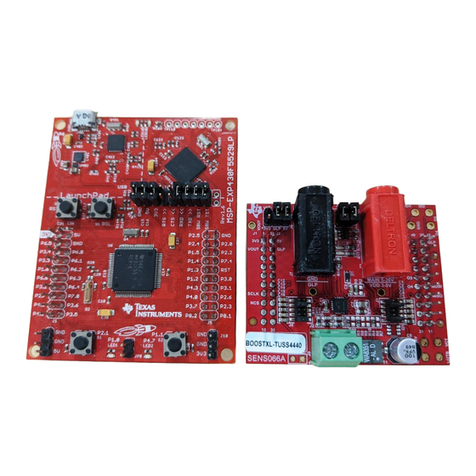

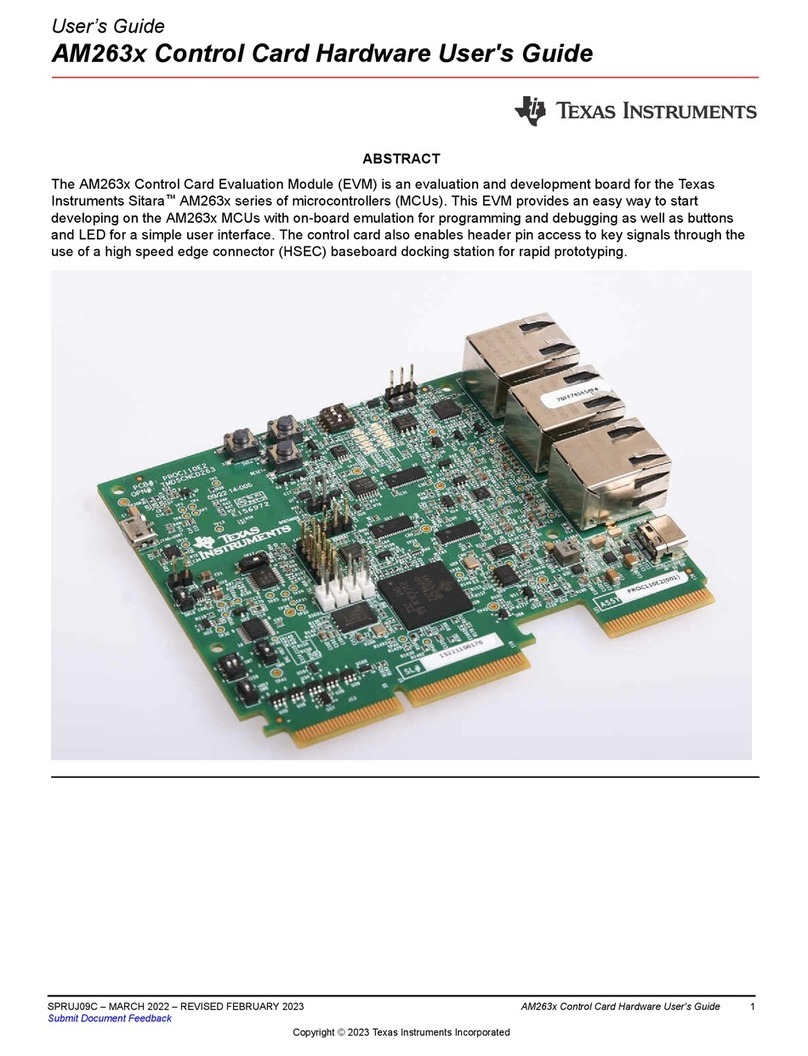

This document intends to serve as a guide for hardware designers creating PCB systems based on the

AM263x family of MCU devices. This document serves to integrate device-specific schematic and PCB layout

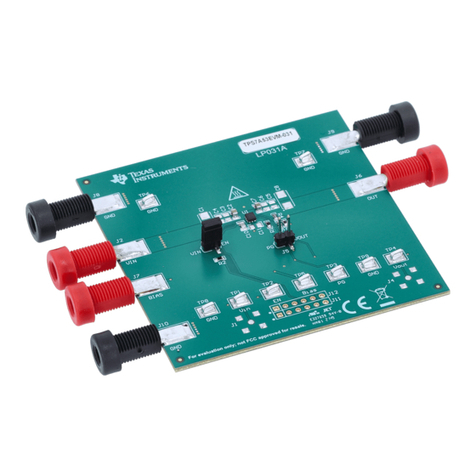

recommendations and examples from the various AM263x evaluation modules (EVM) such as the LP-AM263

Launchpad™ and TMDSCNCD263 controlCard, with the AM263x Sitara™ Microcontroller Data Sheet, AM263x

Sitara™ Microcontroller Technical Reference Manual and other collateral documents and tools, as shown in

Section 12.

Table of Contents

1 Introduction.............................................................................................................................................................................2

1.1 Acronyms........................................................................................................................................................................... 3

2 Power....................................................................................................................................................................................... 3

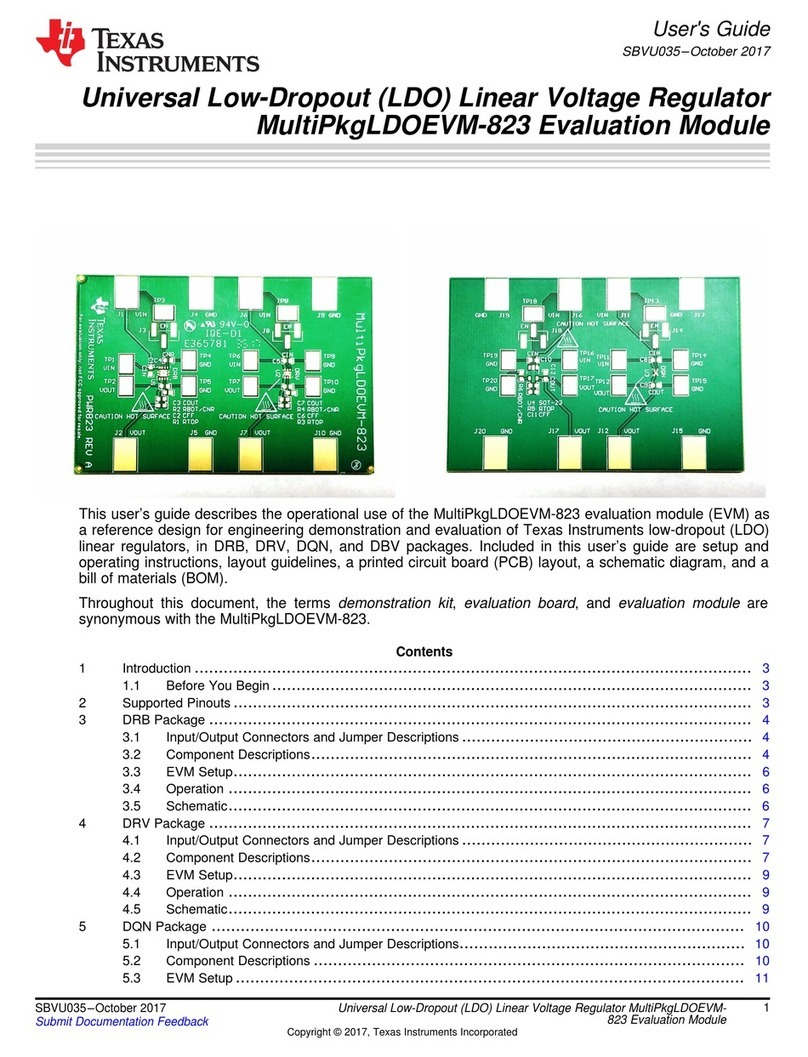

2.1 Discrete DC-DC Power Solution........................................................................................................................................ 3

2.2 Integrated PMIC Power Solution........................................................................................................................................5

2.3 Power Decoupling and Filtering ........................................................................................................................................ 5

2.4 Power Consumption...........................................................................................................................................................9

2.5 Power Distribution Network................................................................................................................................................9

2.6 e-Fuse Power...................................................................................................................................................................15

3 Clocking.................................................................................................................................................................................16

3.1 Crystal and Oscillator Input Options.................................................................................................................................16

3.2 Output Clock Generation..................................................................................................................................................17

3.3 Crystal Selection and Shunt Capacitance........................................................................................................................17

3.4 Crystal Placement and Routing........................................................................................................................................18

4 Resets.................................................................................................................................................................................... 18

5 Bootstrapping....................................................................................................................................................................... 20

5.1 SOP Signal Implementation............................................................................................................................................. 20

5.2 QSPI Memory Controller Implementation........................................................................................................................ 21

5.3 ROM QSPI Boot Requirements....................................................................................................................................... 24

6 JTAG Emulators and Trace.................................................................................................................................................. 24

7 Multiplexed Peripherals....................................................................................................................................................... 25

8 Digital Peripherals................................................................................................................................................................ 26

8.1 General Digital Peripheral Routing Guidelines.................................................................................................................26

9 Layer Stackup....................................................................................................................................................................... 26

9.1 Key Stackup Features......................................................................................................................................................27

10 Vias.......................................................................................................................................................................................28

11 BGA Power Fan-Out and Decoupling Placement.............................................................................................................28

11.1 Ground Return................................................................................................................................................................28

11.2 1.2 V Core Digital Power................................................................................................................................................ 29

11.3 3.3 V Digital and Analog Power......................................................................................................................................31

11.4 1.8 V Digital and Analog Power......................................................................................................................................34

12 References.......................................................................................................................................................................... 37

Trademarks

Launchpad™ and Sitara™ are trademarks of Texas Instruments.

Arm® and Cortex® are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

All trademarks are the property of their respective owners.

www.ti.com Table of Contents

SPRABJ8 – SEPTEMBER 2022

Submit Document Feedback

AM263x Hardware Design Guide 1

Copyright © 2022 Texas Instruments Incorporated