EPM-19 Programmer’s Reference Manual iv

Contents

Introduction ...................................................................................................................1

Related Documents.............................................................................................................1

System Resources and Maps.......................................................................................2

Memory Map ......................................................................................................................2

IRQ Map.............................................................................................................................2

I/O Map...............................................................................................................................3

FPGA Registers.............................................................................................................4

Accessing the FPGA...........................................................................................................4

FPGA I/O Space .................................................................................................................4

FPGA Register Map ...........................................................................................................5

FPGA Register Descriptions...............................................................................................6

Product Information Registers...............................................................................6

Status/Control Register.......................................................................................... 7

SPI Control Registers ............................................................................................8

SPI Data Registers...............................................................................................10

SPI Debug Control Register ................................................................................11

Miscellaneous FPGA Registers...........................................................................12

GPIO Registers....................................................................................................13

COM Port Register..............................................................................................19

FPGA Interrupt Interface..................................................................................................20

Programming Information for Hardware Interfaces..................................................21

PC/104 Expansion Bus.....................................................................................................21

PCI Express Ports (PCIe)..................................................................................................22

Processor WAKE# Capabilities........................................................................................22

GPIO Configuration

..........................................................................................................23

Industrial I/O Functions and SPI Interface.......................................................................25

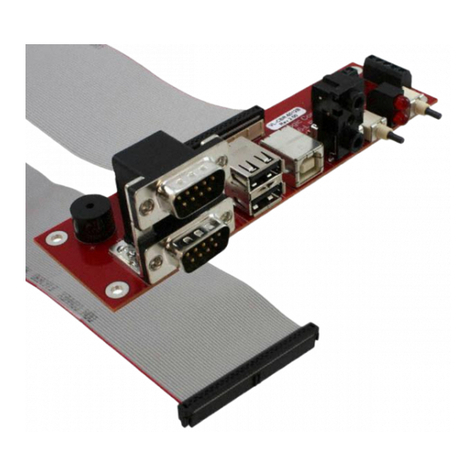

Serial Ports........................................................................................................................26

COM3/COM4 Hardware Configuration..............................................................26

COM3/COM4 Software Configuration...............................................................26

Serial Port Assignment........................................................................................27

COM Ports (FIFO UARTs) .................................................................................28

COM Port Baud Rate Support.............................................................................28

Programmable LED..........................................................................................................30

Appendix A – References............................................................................................31

Tables

Table 1: Memory Map ........................................................................................................ 2