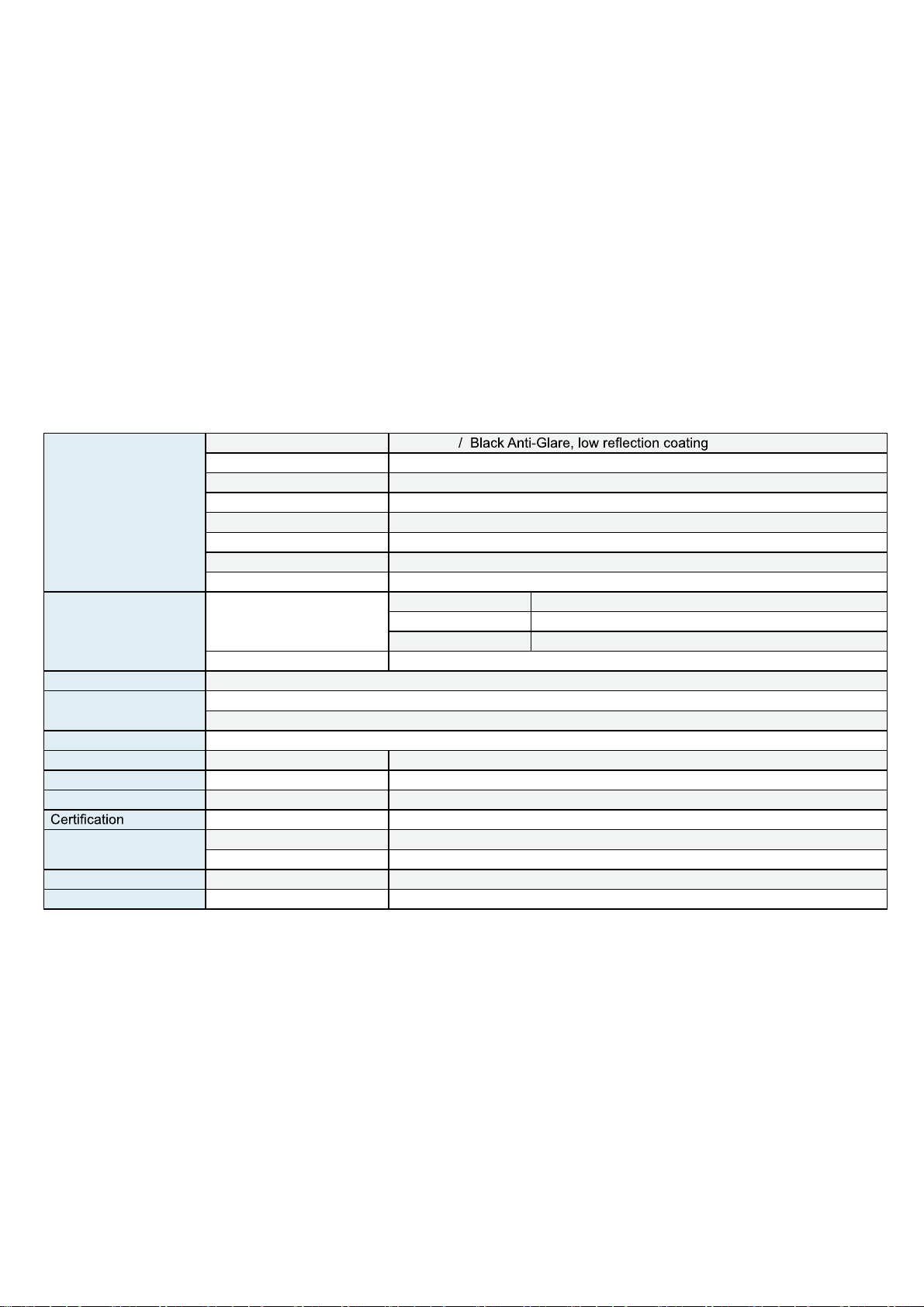

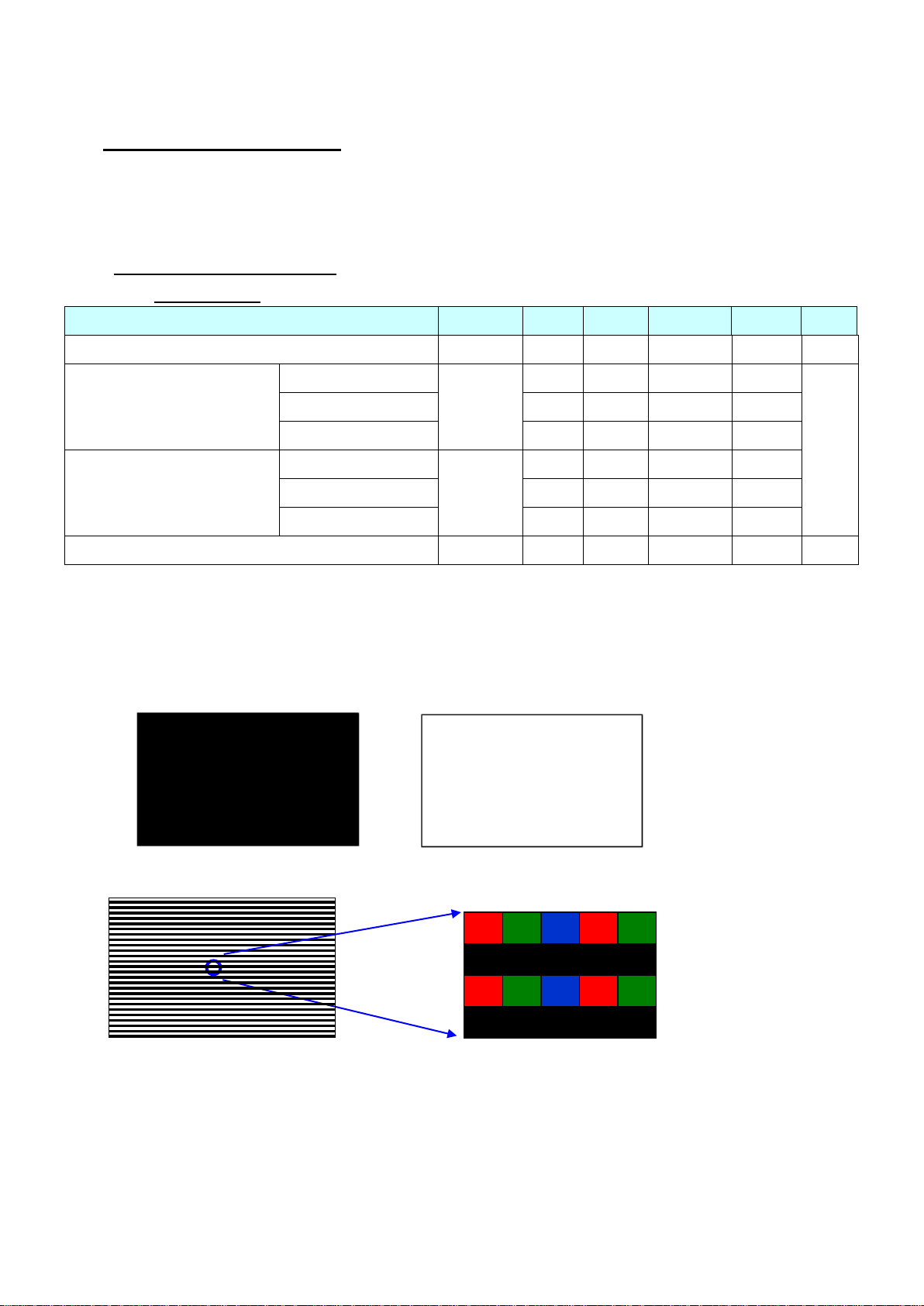

Panel Cell Type / Glass Surface TFT LCD

Aspect Ratio / Size Wide / 65" viewable diagonal area

Active Area / Pixel Pitch 1428.48(H) x 803.52(V) mm / 0.248(H) x 0.744(V) mm

Native Resolution / Colors 3840(H) x 2160(V) / 1.073B

Brightness / Contrast

Response Time

Viewing Angle (typical)

Light Source

Input Sources PC System Signal Analog RGB (0.7/1.0 Vp-p, 75 ohms)

Sync Separate Sync, Composite Sync, Sync On Green

Frequency Fh: 30 - 82Khz , Fv: 50 -75Hz

Audio System 2W speaker x 2

Input Terminals 1 x VGA , 5 x HDMI,1 x DVI,1 x DP , 1 x PC Audio (Stereo Headphone Jack) , 1 x DC Power Plug

Convenient Features Auto Calibration , Back Light Adjustment , Plug&Play (VESA DDC/CI, DDC 2B)

OSD Multi-Languages , Wall Mount Ready (VESA Dimension - please refer to Drawing)

Power Internal power supply with universal / Auto-Sensing, AC90 to 260V, 50/60 Hz

Power Consumption Operation / Power Saving

Operating Condition Temperature / Humidity

Storage Condition Temperature / Humidity

FCC , CE

Dimensions Physical Please refer to Drawing

Carton W x H x D = TBD

Weight N.W. / G.W. 65 Kgs / 69 Kgs

Container Loaded 20ft / 40ft / 40ft HQ TBD (Sets , By pallet)

350 cd/m2(typ) / 5000 : 1

H.176o(- 88o~ + 88o) , V. 176o(- 88o~ + 88o)

LED backlight, Long life, 35,000 hrs (typ)

0oC ~ 50oC (32oF ~ 122oF) , 10% ~ 90% (no condensation)

- 20oC ~ 60oC (- 4oF ~ 140oF) , 10% ~ 90% (no condensation)

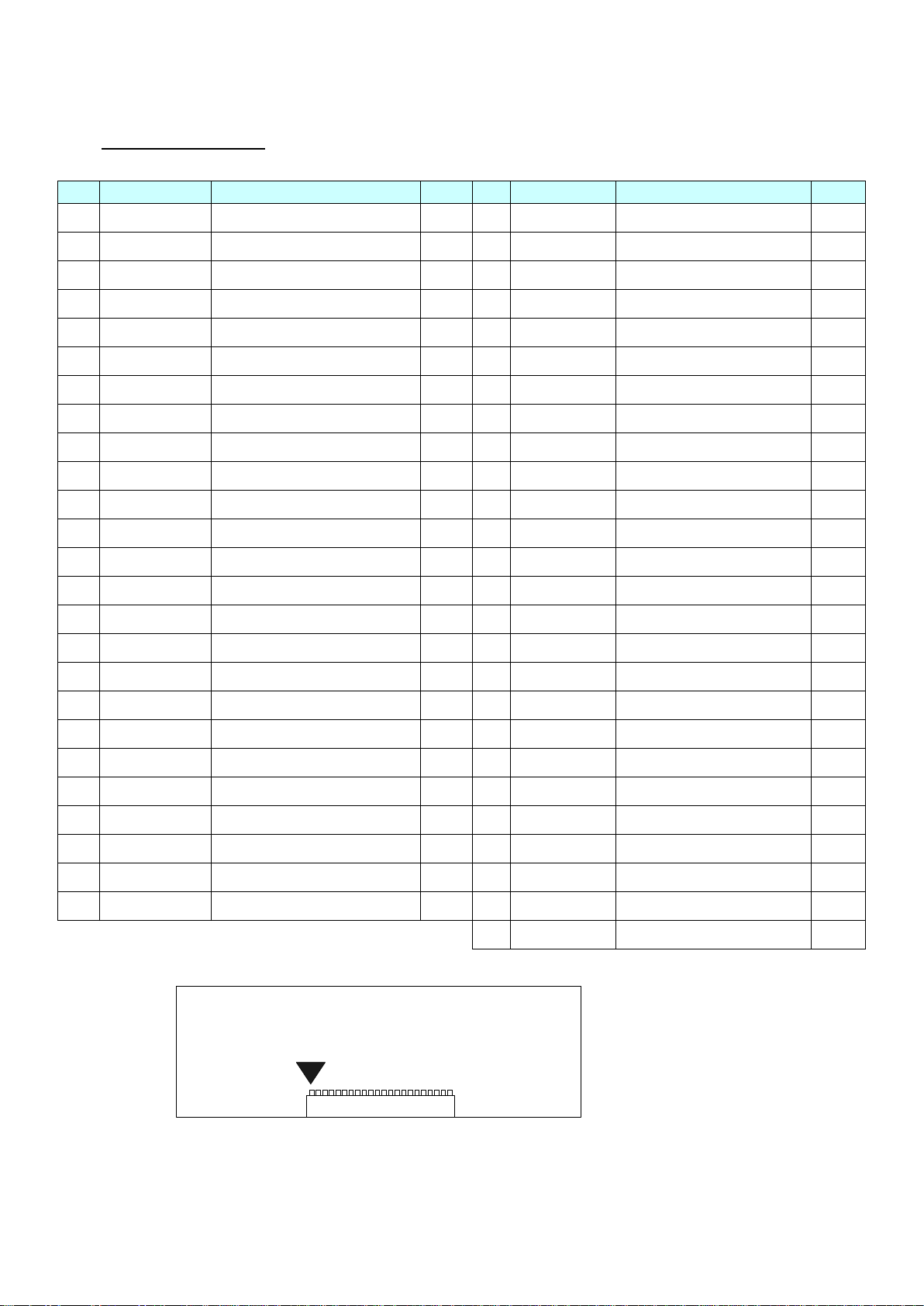

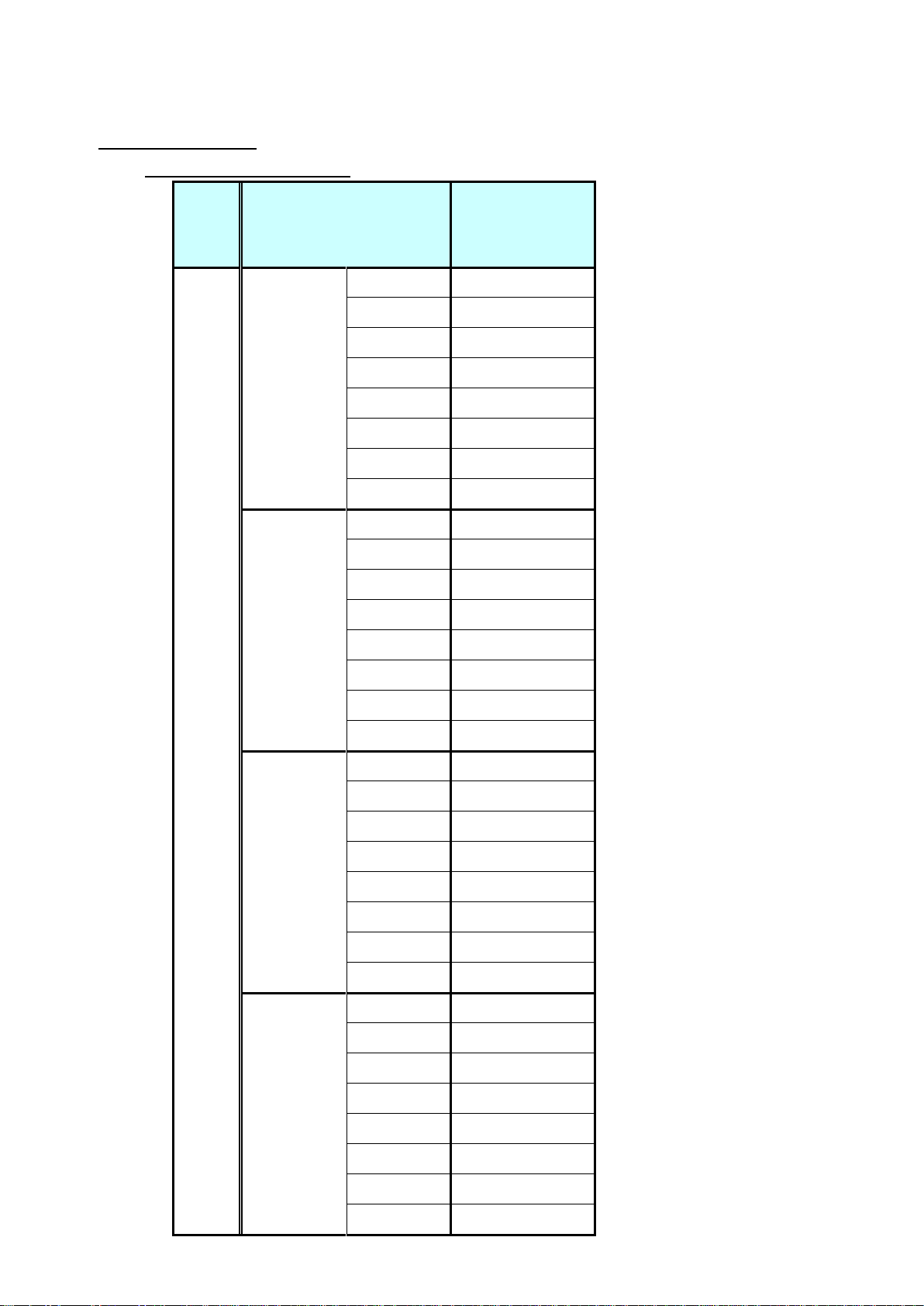

2 General Description

This specification applies to the 65 inch Color TFT-LCD Module P650QVF03.0. This LCD module has a

TFT active matrix type liquid crystal panel 3840x2160 pixels. This module supports 3840x2160 mode.

Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arranged in vertical stripes.

Gray scale or the brightness of the sub-pixel color is determined with a 10-bit gray scale signal for each

dot.

260 watt , < 1 watt (Support DPMS)

≤ 6.5 ms (G-to-G)