Section I discusses Z-80 hardware. The architecture, interface sig-

nals, and timing are discussed in the first two chapters. Addressing

modes and instructions are covered in the next two chapters; both

addressing and instruction repertoire are fairly easily grouped and

explained, although they may appear confusing at first glance. The

effect of arithmetic operations and other operations on CPU flags is

presented in Chapter 6. The powerful interrupt sequences of the

Z-80 are discussed in the next chapter. Chapter 8 describes interfac-

ing examples of I/O and memory devices.

Section II describes Z-80 software. A representative Z-80 assembler

program is introduced in the first chapter of the section. An assem-

bler is almost a necessity with a microprocessor having such a large

instruction set, but machine language aspects are also covered.

Chapters 10 through 15 present the common programming opera-

tions of moving data, arithmetic operations, shifting and bit opera-

tions, list and table procedures, subroutine use, and I/O functions in

relation to instruction set groups. Many examples of each kind of

operation are provided. The last chapter of the section details some

commonly used subroutines written in Z-80 assembly language.

The third section discusses microcomputers built around the Z-80.

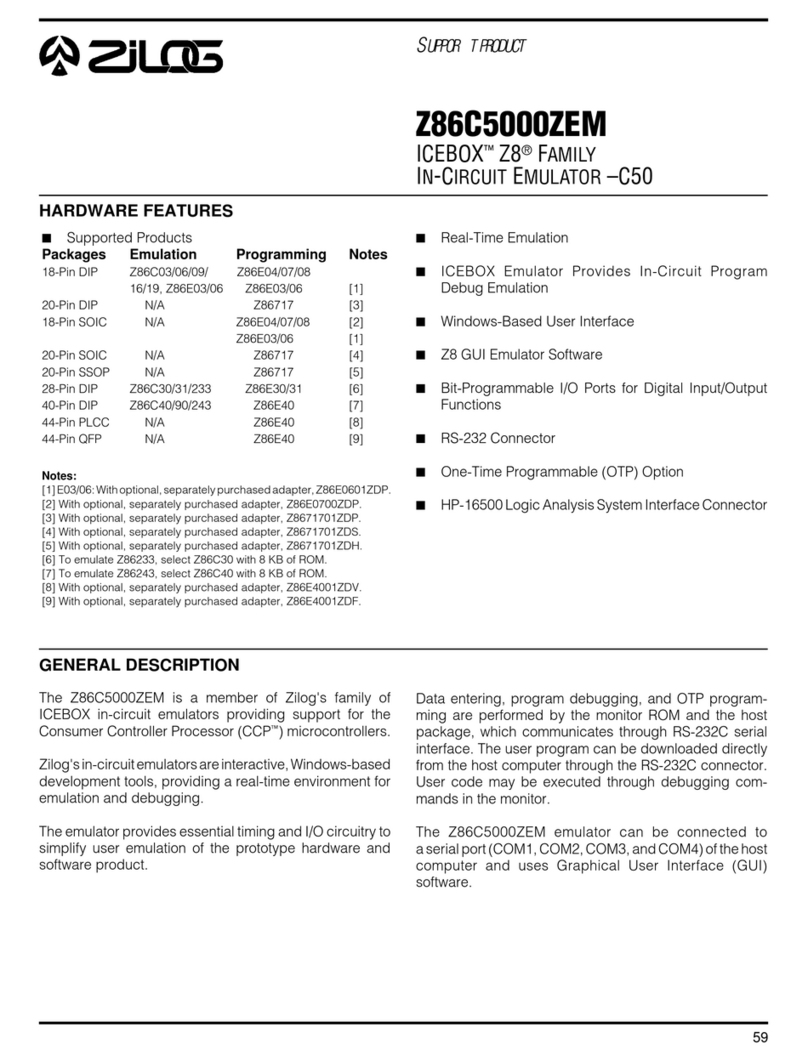

Chapter 17 covers Zilog products including the microcomputer

board products in the Z-80 family and development systems. Four

other Z-80 microcomputer manufacturers are described in the last

chapter. Technical Design Labs, Inc., Cromemco, Inc., The Digital

Group, Inc., and Radio Shack. The hardware and software aspects

of all five manufacturers are presented.

The Z-80 will prove attractive to many users, not only as a succes-

sor to the 8080A, but as a powerful computer in its own right.

The Z-80 will soon have a successor, in this dynamic microcom-

puter development environment, but for the time being it represents

microcomputer "state-of-the-art." The author hopes that the reader

will derive a great deal of benefit from the book and that the Z-80

will solve a few hardware and software implementation problems.

Much credit for this book goes to my wife, Janet, who has solved

my major software implementation problems-manuscript prepara-

tion.

WILLIAM BARDEN, JR.

To Bill and Norma and

the Little Green Onions.