iv List of Figures

List of Figures

Figure 1-1: PXI-9816 Bandwidth Chart ........................................ 5

Figure 1-2: PXI-9826 Bandwidth Chart ........................................ 5

Figure 1-3: PXI-9846 Bandwidth Chart ........................................ 6

Figure 1-4: PXI-9816 FFT with ±0.2 V Input Range..................... 7

Figure 1-5: PXI-9816 FFT with ±1 V Input Range........................ 8

Figure 1-6: PXI-9826 FFT with ±0.2 V Input Range..................... 9

Figure 1-7: PXI-9826 FFT with ±1 V Input Range...................... 10

Figure 1-8: PXI-9846 FFT with ±0.2 V Input Range................... 11

Figure 1-9: PXI-9846 FFT with ±1 V Input Range...................... 12

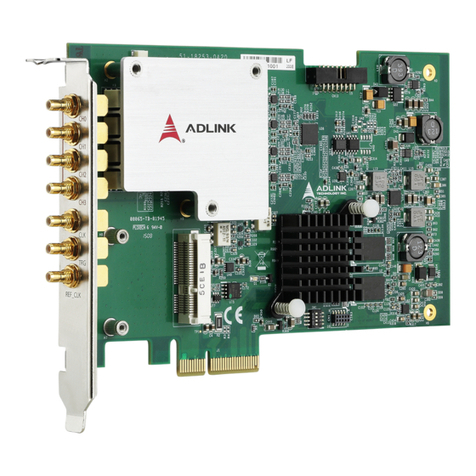

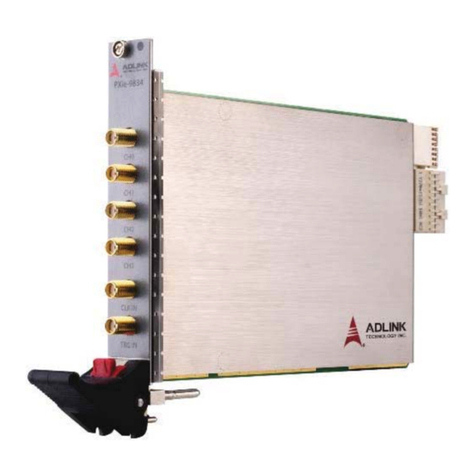

Figure 2-1: PXI-98x6 Mechanical Drawing................................. 19

Figure 2-2: DAQPilot Main Interface .......................................... 21

Figure 2-3: DAQMaster Device Manager................................... 22

Figure 2-4: Legacy Software Support Overview ........................ 23

Figure 3-1: PXI-98x6 Functional Block Diagram ........................ 25

Figure 3-2: Analog Input Signal Block Diagram ......................... 26

Figure 3-3: Basic Acquisition Timing Of Digitizer ....................... 28

Figure 3-4: PXI-98x6 Timebase Source and Architecture.......... 29

Figure 3-5: Configuring Different Sampling Rate of a Digitizer. . 31

Figure 3-6: PXI-98x6 Trigger Architecture ................................. 32

Figure 3-7: External Digital Trigger Polarity and

Pulse Width Requirement. ....................................... 33

Figure 3-8: Analog Trigger Conditions ....................................... 35

Figure 3-9: TRG IO Output Signal Timing.................................. 36

Figure 3-10: Post-trigger Acquisition............................................ 37

Figure 3-11: Pre-trigger Mode Operation ..................................... 38

Figure 3-12: Pre-trigger Mode Operation ..................................... 38

Figure 3-13: Middle-trigger Mode Operation ................................ 39

Figure 3-14: Delay-trigger Mode Operation ................................. 39

Figure 3-15: Re-trigger Mode Operation. ..................................... 40

Figure 3-16: Scatter-Gather DMA for Data Transfer .................... 41

Figure 3-17: SSI Architecture....................................................... 43

Figure 3-18: SSI_TRIG1 Input and Output Timing

Characteristics ......................................................... 44

Figure 3-19: SSI_TRIG2 Output Timing....................................... 45

Figure 3-20: SSI_TRIG2 Input Timing Requirement .................... 45

Figure 3-21: SSI_START_OP Output and Input Timing

Characteristics ......................................................... 46