viii Table of Contents

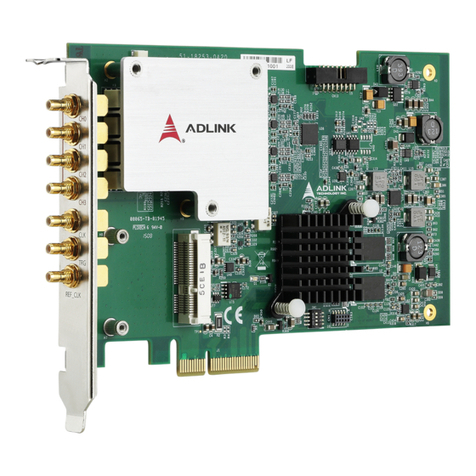

Leading EDGE COMPUTING

3.1 Functional Block Diagram .................................................. 23

3.2 Analog Input Channel ........................................................ 23

3.2.1 Analog Input Front-End Configuration ...................... 23

3.2.2 Input Range and Data Format .................................. 24

3.2.3 DMA Data Transfer...................................................26

3.3 Trigger Source ................................................................... 27

3.3.1 Software Trigger ....................................................... 28

3.3.2 External Digital Trigger ............................................. 28

3.3.3 Analog Trigger .......................................................... 29

3.3.4 PXI Trigger Bus ........................................................ 30

3.3.5 PXI Star .................................................................... 30

3.3.6 PXIe Differential Trigger ........................................... 30

3.4 Trigger Modes.................................................................... 31

3.4.1 Post Trigger Mode .................................................... 31

3.4.2 Delayed Trigger Mode .............................................. 32

3.4.3 Pre-Trigger Mode...................................................... 32

3.4.4 Middle Trigger Mode.................................................33

3.4.5 Acquisition with Re-Triggering .................................. 34

3.5 Timebase ........................................................................... 35

3.5.1 Internal Sampling Clock............................................35

3.5.3 External Reference Clock ......................................... 36

3.6 Acquisition Timing Control ................................................. 37

3.7 Synchronizing Multiple Modules ........................................ 39

3.7.1 Multi-module Synchronization Interfaces..................43

A Appendix: Calibration....................................................... 45

A.1 Calibration Constant .......................................................... 45

A.2 Auto-Calibration ................................................................. 46

Important Safety Instructions.............................................. 49

Getting Service ..................................................................... 53