[AK4675]

MS0963-E-00 2008/05

- 10 -

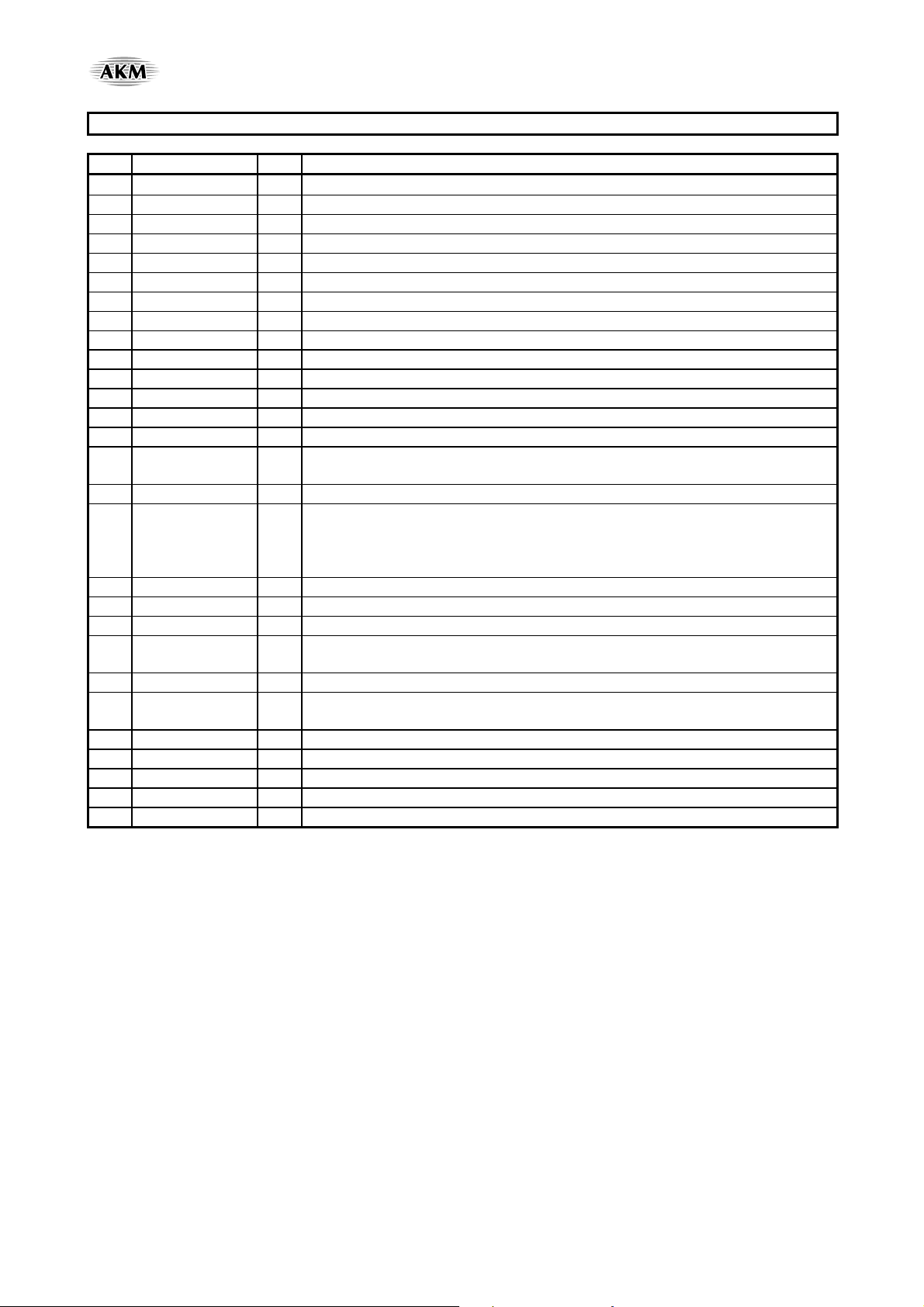

ABSOLUTE MAXIMUM RATINGS

(VSS1=VSS2=VSS3=VSS4=VSS1A=VSS2A=VSS3A=0V; Note 2, Note 3)

Parameter Symbol Min max Units

Power Supplies: CODEC Analog AVDD −0.3 4.0 V

(Note 4) PLLBT PVDD

−0.3 4.0 V

10bit SAR ADC SAVDD −0.3 4.0 V

CODEC Digital DVDD

−0.3 4.0 V

CODEC Digital I/O 2 TVDD2 −0.3 4.0 V

CODEC Digital I/O 3 TVDD3 −0.3 4.0 V

HP/SPK-Amp Analog AVDDA −0.3 6.0 V

HP/SPK-Amp Digital I/F TVDDA −0.3 6.0 V

Speaker-Amp & Headphone-Amp SVDDA −0.3 6.0 V

Charge Pump PVDDA

−0.3 4.0 V

Input Current, Any Pin Except Supplies IIN - ±10 mA

Analog Input Voltage 1 (Note 5)VINA1 −0.3 AVDD+0.3 V

Analog Input Voltage 2 (Note 6)VINA2 −0.3 SAVDD+0.3 V

Analog Input Voltage 3 (Note 7)VINA3 −0.3 (AVDDA+0.3) or 6.0 V

Analog Input Voltage 4 (Note 8)VINA4 −0.3 6.0 V

Digital Input Voltage 1 (Note 9) VIND1

−0.3 DVDD+0.3 V

Digital Input Voltage 2 (Note 10) VIND2

−0.3 TVDD2+0.3 V

Digital Input Voltage 3 (Note 11) VIND3

−0.3 TVDD3+0.3 V

Digital Input Voltage 4 (Note 12) VIND4

−0.3 (TVDDA+0.3) or 6.0 V

Ambient Temperature (powered applied) Ta −30 85 °C

Storage Temperature Tstg −65 150 °C

Ta=85ºC (Note 14) Pd1 - 0.91 WMaximum Power Dissipation

(Note 13) Ta=70ºC (Note 15) Pd2 - 1.18 W

Note 2. All voltages with respect to ground.

Note 3. VSS1, VSS2, VSS3, VSS4, VSS1A, VSS2A and VSS3A must be connected to the same analog

ground plane.

Note 4. TVDDA should be connected to DVDD.

Note 5. RIN4/IN4−, LIN4/IN4+, RIN3/IN3−, LIN3/IN3+, RIN2/IN2−, LIN2/IN2+, RIN1/IN1−, LIN1/IN1+ pins

Note 6. SAIN1, SAIN2, SAIN3 pins

Note 7. LIN1A, RIN1A, SPIN pins. The maximum value is smaller value between (AVDDA+0.3)V and 6.0V.

Note 8. VBATIN pin

Note 9. PDN, SCL, SDA, SDTI, LRCK, BICK, MCKI pins

Pull-up resistors at SDA and SCL pins should be connected to (DVDD+0.3)V or less voltage.

Note 10. BICKA, SYNCA, SDTIA pins

Note 11. BICKB, SYNCB, SDTIB pins

Note 12. PDNA, MCKIA pins. The maximum value is smaller value between (AVDDA+0.3)V and 6.0V.

Note 13. In case that the PCB wiring density is 300%. This power is the AK4675 internal dissipation that does not include

power of externally connected speaker and headphone.

Note 14. When Ta=85°C, the HP-Amp power must be under 30mW@16Ωand SPK-Amp power must be 1.0W@8Ω.

Note 15. When Ta=70°C, the HP-Amp power must be under 30mW@16Ωand SPK-Amp power must be 1.6W@8Ω.

WARNING: Operation at or beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.