3

dc2692af

DEMO MANUAL DC2692A

Using External Precision Resistor to Adjust

Full‑ScaleOutput Current

The DC2692 has an unstuffed resistor (R4) that can be

used to set and adjust the full-scale output current. Move

the jumper named FS ADJ (JP2) from INT to EXT. It is

recommended to use a resistor with better than 2ppm/°C

temperature coefficient to take advantage of the LTC2662

low temperature coefficient. Values between 19k and 50k

can be used for the precision resistor.

Using External Supplies for VDDx

The DC2692 can be configured to connect different sup-

plies than V+. Move the jumper labeled VDDx from V+to

EXT and connect the low noise supply to the correspond-

ing VDDx turret.

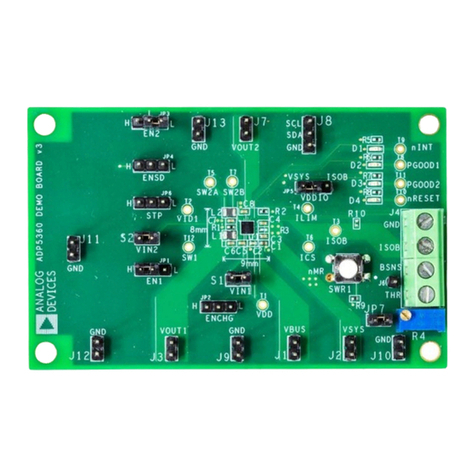

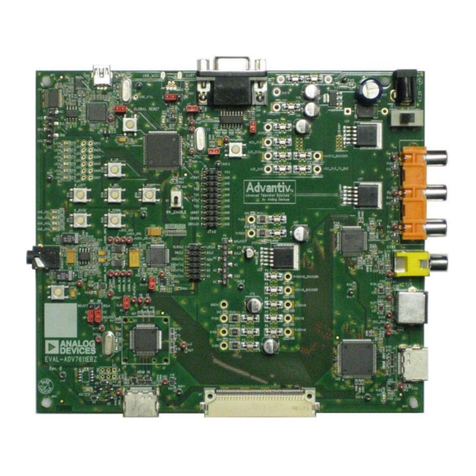

Connectors and Turrets

J1:Interface connector to DC590 controller or Lin-

duinoprovides IOVCC power, SPI interface, and board

identification.

V

–

, GND, V

+

:Analog supplies, connected to the LTC2662

V+and V–pins. Nominally positive supply should be 7V

to 33V and negative supply should be 0V to –15V. Refer

to the data sheet for other supply configurations.

GND: Additional ground posts and exposed ground plane

around the board edge allow solid connection to prototype

circuitry and measurement equipment.

VCC:Analog supply voltage. Normally supplied by an

onboard LT3042 regulator set to 5V that is powered from

the V+supply. For single supply applications, VCC may be

tied directly to V+and supplied with 2.85V to 5.5V.

VDD0 to VDD4:Output supply voltage. A jumper is used to

connect the output supply to V

+

. Placing the jumper in the

EXT position allows the output supply voltage channel to

be connected externally to this point.

REF:Connection to the REF pin. In internal reference

mode, the reference voltage may be monitored at this

point. Placing REF SEL jumper in EXT position allows an

external low noise reference to be connected to this point.

Refer to the data sheet for compatible voltages.

MUX:Monitor Mux output. Allows surveying the DACout-

puts under software control. Must be measured with a high

impedance meter (output impedance is nominally10kΩ).

OUT0 – OUT4: DAC outputs.

CLR:Asynchronous clear input (pulled high to IOVCC with

a 5k resistor). Pull to the ground to reset the DAC to the

power-on reset value.

TGP:Toggle input (pulled high to IOVCC with a 5k resis-

tor). A high level on this pin enables software toggling.

See data sheet for a complete description of toggle

operation.

LDAC:Asynchronous DAC update. If CS/LD is high at the

falling edge of LDAC, DAC outputs will be updated with

the contents of the input registers. If CS/LD is low when

LDAC goes low, the DAC registers are updated after CS/

LD returns high.

FAULT:Fault detection pin (pulled high to IOVCC with a

5k resistor). The LTC2662 pulls this pin low if a fault is

detected. It is released on the next rising edge of CS/LD.

Jumpers

REF SEL (JP1): Selects internal or external reference

mode.

FS ADJ (JP2): Sets the full-scale current for the DACs.

Ensure FS ADJ is set to EXT position when using an exter-

nal precision resistor.

V

DD0

, V

DD1

, V

DD2

, V

DD3

, V

DD4

(J3, J4, J5, J6, J7): Select

the output supply voltages for the DACs to be either V+or

external via the turret.

LEDs

FAULT:Lights when FAULT pin asserts, indicating a fault

has occurred. (Note that LED will light if positive analog

supply is present and IOVCC is not. IOVCC is normally

supplied by the controller.)

Test Points

The SPI bus is available on a row of through-hole test

points next to J1 that may be used to monitor the bus or

drive the bus with an external controller.

EEGND, WP: For factory use only.

QUICK START PROCEDURE