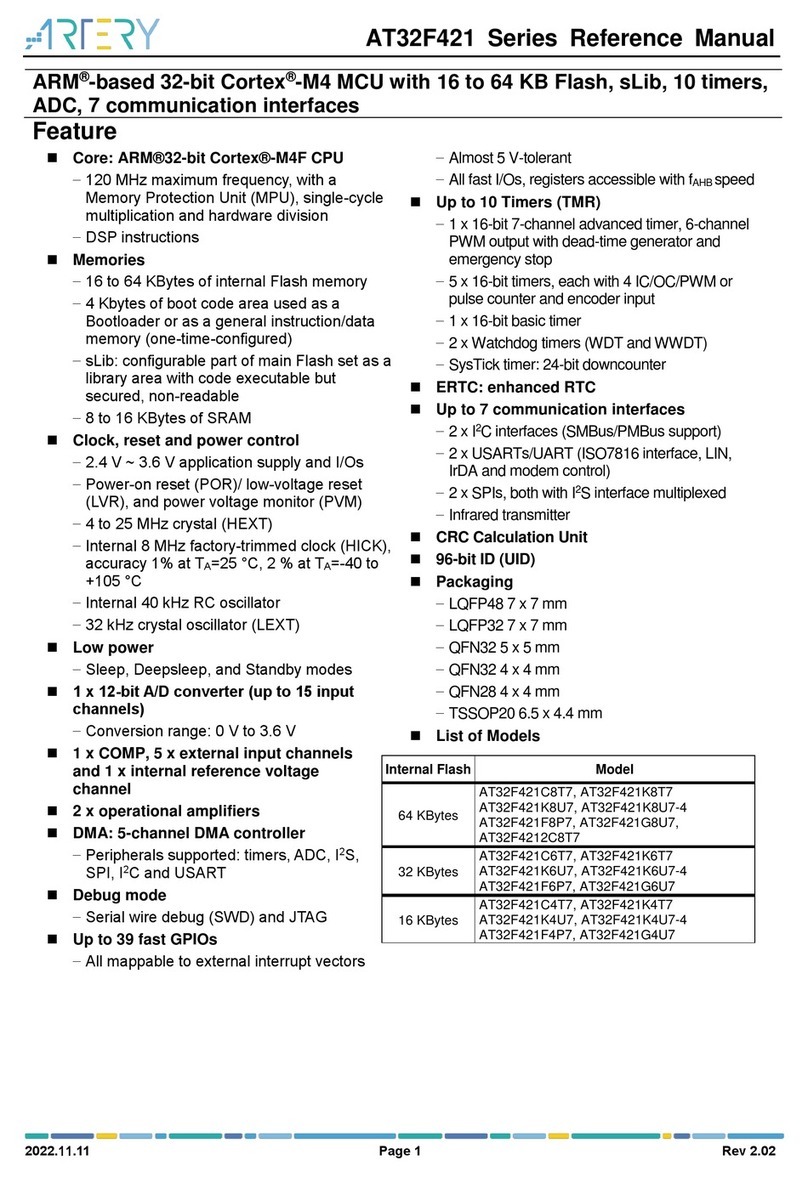

AT32F415 Series Reference Manual

2020.06.28 Page 1 Version 1.02

ARM®-based32-bit Cortex®-M4 MCU, with 64 Kbyte ~ 256 Kbyte Internal Flash,

sLib, USB-OTG, 11 Timers, 2 COMPs,1 ADC, 12 Communication Interfaces

Function

Core: ARM®32-bit Cortex®-M4 CPU

−Operating rate up to 150 MHz, with

Memory Protection Unit (MPU),

embedded single cycle multiplication

and hardware division

−DSP instruction set provided

Memory

−From 64 Kbyte to 256 Kbyte internal

Flash program/data memory

−18 Kbytes of system memory used as a

Bootloader or as a general

instruction/data memory (one-time-

configured)

−Up to 32 Kbyte SRAM

−sLib: configurable part of main Flash set

as a library area with code excutable but

secured, non-readable

Clock, Reset, and Power Management

−2.6 V ~ 3.6 V and I/O pins

−Power-on/Power-down Reset (POR/PDR),

Programmable Voltage Detector (PVD)

−4 to 25 MHz crystal oscillator

−Internal48 MHz RC factory-trimmed RC

(accuracy 1% at TA=25 °C, 2.5% at TA= -

40 to 105°C )

−Internal 40 kHz RC with calibration

−32 kHz oscillator with calibration

Low Power Consumption

−Sleep, Stop, and Standby mode

−VBAT support for RTC and twenty 32-bit

backup registers

One 12-bit, 0.5 μs A/D converter (Up to 16

input channels)

−Conversion range: 0 V ~ 3.6 V

−One sample –and- hold capability

−Temparature sensor

Two analog comparators

DMA: 14-channel DMA controller

−Peripherals supported: Timer, ADC,

SDIO, I2Ss, SPIs, I2Cs and USARTs

Debug Mode

−Serial Wire Debug (SWD) and JTAG interface

Up to 55 Fast I/Os

−27/39/55/multi-functional bidirectional

I/Os, all mappable to 16 external

interrupt vectors and almost 5 V-tolerant

Up to 11 Timers

−Up to 5 16-bit timers + 2 32-bit timers;

each with 4 IC/OC/PWM or pulse counter

and incremental encoder input.

−1 16-bit motor control PWM and

advanced timers with dead-time

generator and emergency stop

−2 Watchdog timers (independent and

window)

−SysTick timer: a 24-bit downcounter

ERTC: enhanced RTC with subsecond

accuracy and hardware calendar

Up to 12 Communication Interfaces

−2 x I2C interfaces (SMBus/PMBus)

−Up to 5 USARTs (ISO7816 interface, LIN,

IrDA capability, and modem control)

−2 x SPIs (50 Mbit/s), both with I2S interfaces

multiplexed

−CAN interface (2.0B active) with

dedicated 256 bytes SRAM

−USB2.0 full-speed device/host/OTG

controller with dedicated 1280 bytes

SRAM, device mode supporting cystal-

less

−SDIO interface

CRC Calculation Unit

96-bit unique ID (UID)

Packaging

−LQFP64 10x10 mm

−LQFP64 7x7 mm

−LQFP48 7x 7 mm

−LQFP48 6 x 6 mm

−QFN32 4 x 4 mm

List of Models

Table 1. Device summary

AT32F415RCT7, AT32F415RCT7-7,

AT32F415CCT7, AT32F415CCU7,

AT32F415KCU7-4

AT32F415RBT7, AT32F415RBT7-7,

AT32F415CBT7, AT32F415CBU7,

AT32F415KBU7-4

AT32F415R8T7, AT32F415R8T7-7,

AT32F415C8T7, AT32F415K8U7-4