5

9524B–AT42–04/09

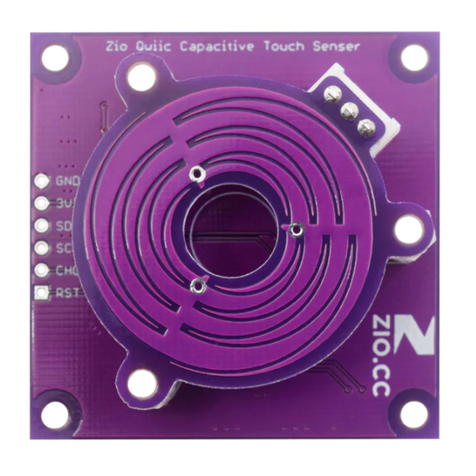

AT42QT1040

The use of AKS is selected by connecting a 1 Mresisitor between Vdd and the SNSK0 pin

(see Section 4.1 on page 8 for more information). When AKS is disabled, any combinations of

keys can enter detect.

2.2.5 Auto Drift Compensation

Signal drift can occur because of changes in Cx and Cs over time. It is crucial that drift be

compensated for, otherwise false detections, non-detections, and sensitivity shifts will follow.

Drift compensation is performed by making the reference level track the raw signal at a slow

rate, but only while there is no detection in effect. The rate of adjustment must be performed

slowly otherwise legitimate detections could be ignored.

Once an object is sensed and a key is in detect, the drift compensation mechanism ceases,

since the signal is legitimately high and should not therefore cause the reference level to

change.

The QT1040's drift compensation is “asymmetric”: the reference level drift-compensates in one

direction faster than it does in the other. Specifically, it compensates faster for decreasing

(towards touch) signals than for increasing (away from touch) signals. The reason for this

difference in compensation rates is that increasing signals should not be compensated for

quickly, since a nearby finger could be compensated for partially or entirely before even

approaching the sense electrode. However, decreasing signals need to be compensated for

more quickly. For example, an obstruction over the sense pad (for which the sensor has already

made full allowance) could suddenly be removed, leaving the sensor with an artificially elevated

reference level and thus become insensitive to touch. In this latter case, the sensor will

compensate for the object's removal very quickly, usually in only a few seconds.

Negative drift (that is, towards touch) occurs at a rate of ~3 seconds, while positive drift occurs at

a rate of ~1 second.

Drifting only occurs when no keys are in detect state.

2.2.6 Response Time

The QT1040's response time is highly dependent on run mode and burst length, which in turn is

dependent on Cs and Cx. With increasing Cs, response time slows, while increasing levels of Cx

reduce response time. The response time will also be slower in slow mode due to a longer time

between burst measurements. This mode offers an increased detection latency in favor of

reduced average current consumption.

2.2.7 Spread Spectrum

The QT1040 modulates its internal oscillator by ±7.5 percent during the measurement burst.

This spreads the generated noise over a wider band reducing emission levels. This also reduces

susceptibility since there is no longer a single fundamental burst frequency.

2.2.8 Max On-duration

If an object or material obstructs the sense pad, the signal may rise enough to create a

detection, preventing further operation. To prevent this, the sensor includes a timer known as

the Max On-duration feature which monitors detections. If a detection exceeds the timer setting,

the sensor performs an automatic recalibration. Max On-duration is set to ~30s.

Downloaded From Oneyac.com