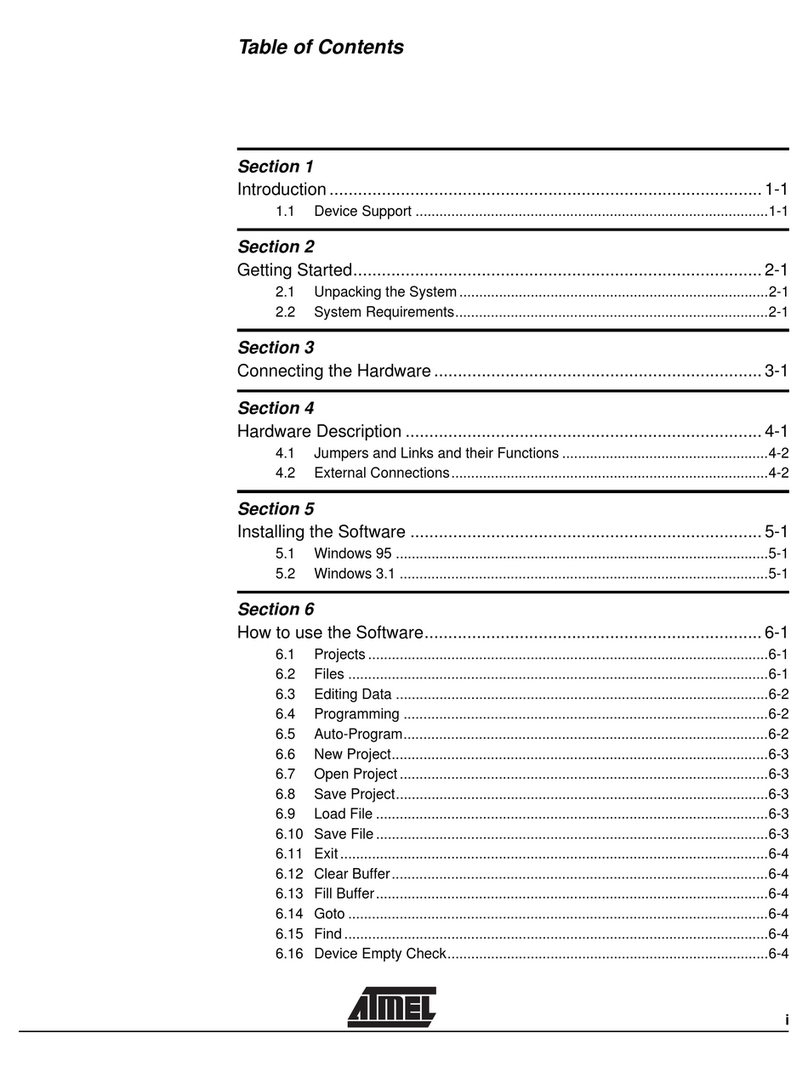

Atmel AVR AT90S2323 User manual

Other Atmel Microcontroller manuals

Atmel

Atmel STK200 User manual

Atmel

Atmel AT32UC3 Series Installation and operating instructions

Atmel

Atmel AVR128 Installation and operating instructions

Atmel

Atmel AVR943 User manual

Atmel

Atmel STK520 User manual

Atmel

Atmel AVR XMEGA E Installation and operating instructions

Atmel

Atmel AVR1921 Installation and operating instructions

Atmel

Atmel AT91CAP9A-DK User manual

Atmel

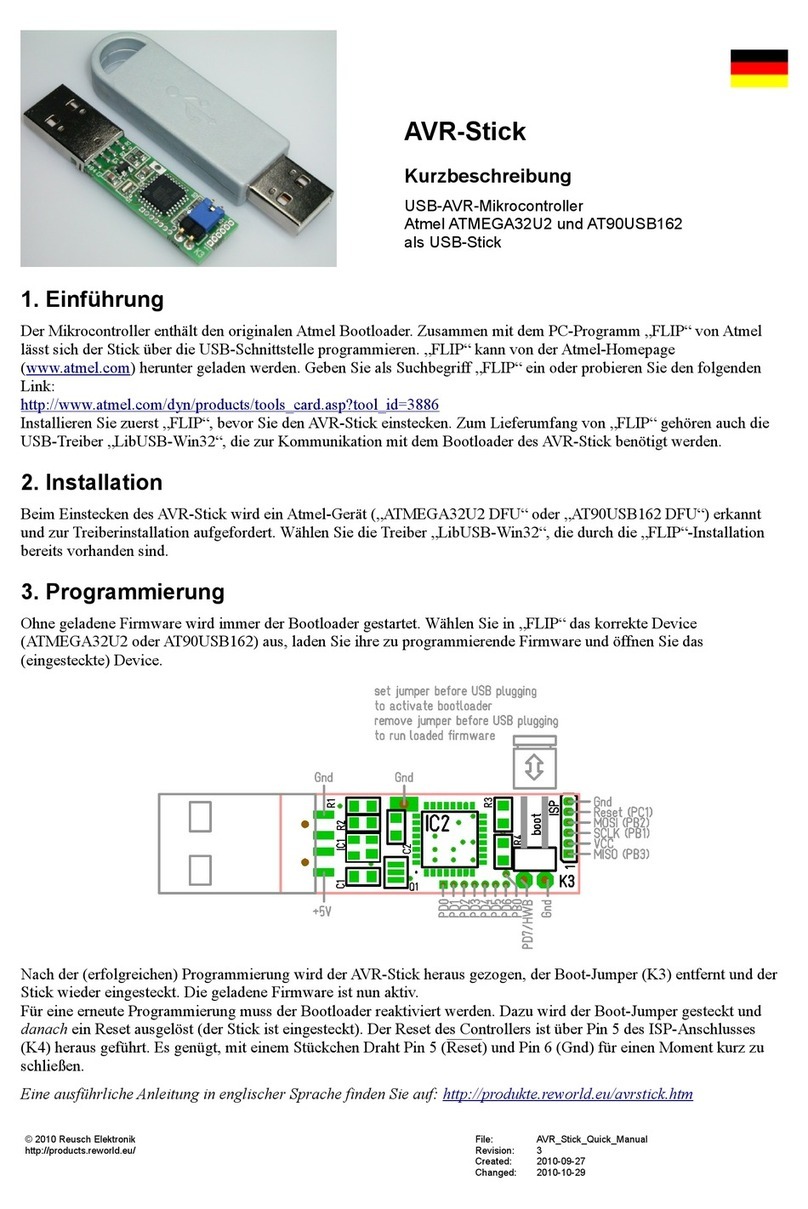

Atmel AT90USB162 User manual

Atmel

Atmel AT32UC3A3256S User manual

Atmel

Atmel AVR User manual

Atmel

Atmel AT32UC3L064 User manual

Atmel

Atmel AT90S8515-8PI User manual

Atmel

Atmel AVR AVR350 Installation and operating instructions

Atmel

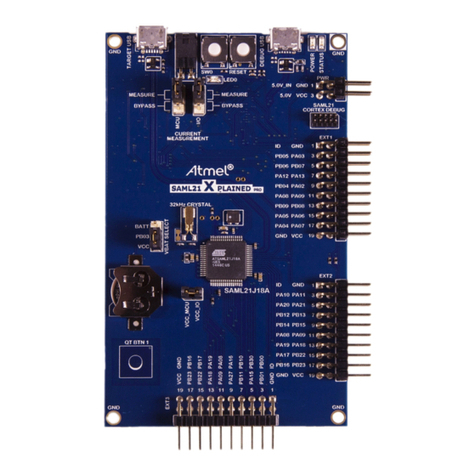

Atmel SAM L21 Xplained Pro User manual

Atmel

Atmel SAM4L Xplained Pro User manual

Atmel

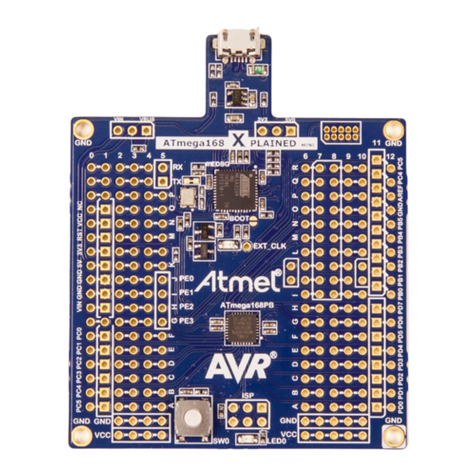

Atmel ATmega168PB Xplained Mini User manual

Atmel

Atmel AVR ATmega103 User manual

Atmel

Atmel AVR180 Installation and operating instructions

Atmel

Atmel ATmega128A-STK600 Installation and operating instructions

Popular Microcontroller manuals by other brands

DIGITAL-LOGIC

DIGITAL-LOGIC MICROSPACE manual

Texas Instruments

Texas Instruments TMS320F2837 D Series Workshop Guide and Lab Manual

CYPRES

CYPRES CY14NVSRAMKIT-001 user guide

Espressif Systems

Espressif Systems ESP8266EX Programming guide

Abov

Abov AC33M8128L user manual

Silicon Laboratories

Silicon Laboratories C8051F800 user guide