1.1 GENERAL GUIDELINES

1. When servicing, observe the original lead dress. if a short circuit is found, replace all parts which have

been overheated or damaged by the short circuit.

2. After servicing, see to it that all the protective devices such as insulation barrier, insulation papers

shields are properly installed.

3. After servicing, make the following leakage current checks to prevent the customer from being exposed

to shock hazards.

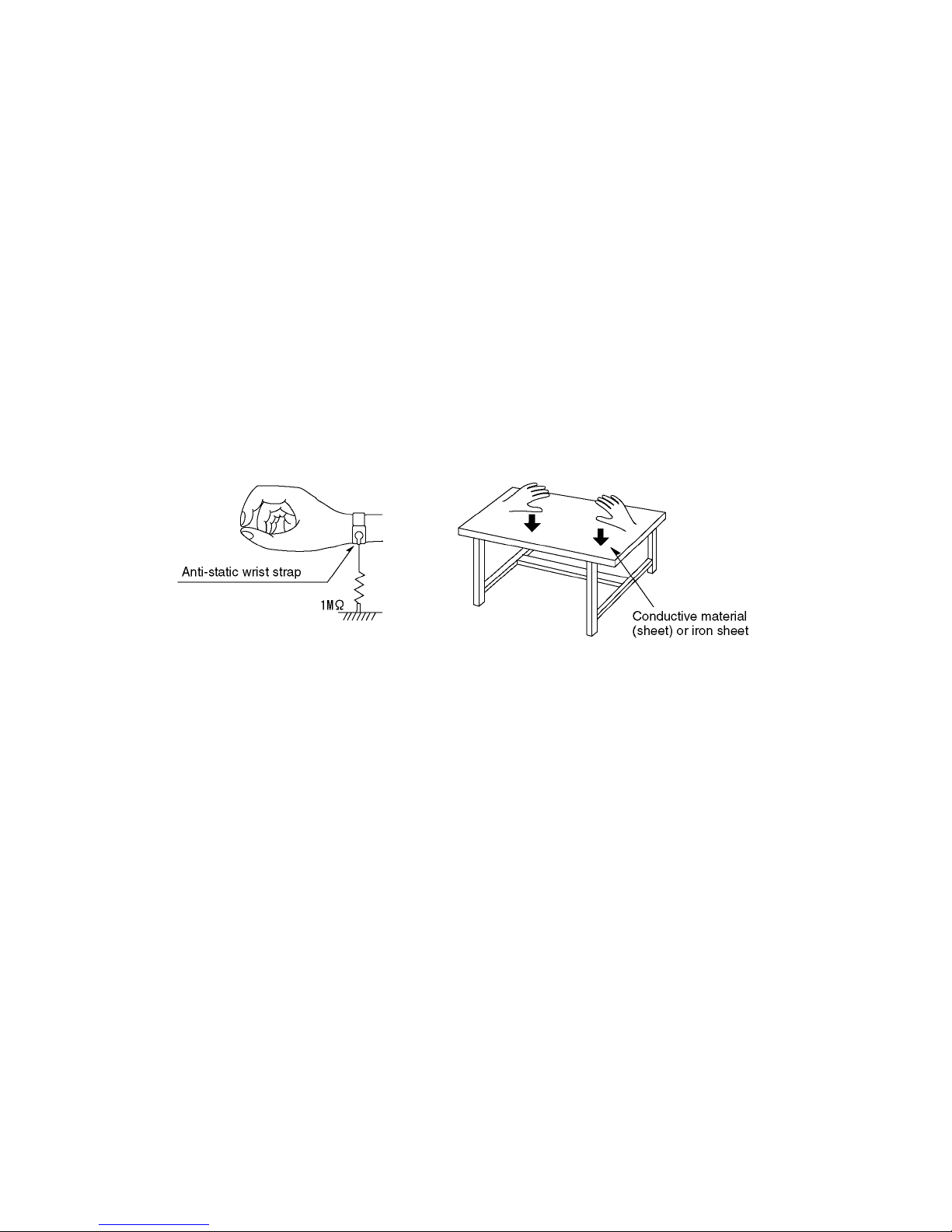

Some semiconductor(solid state)devices can be damaged easily by static electricity. Such components

commonly are called Electrostatically Sensitive(ES)Devices. Examples of typical ES devices are integrated

circuits and some field-effect transistors and semiconductor chip components. The following techniques

should be used to help reduce the incidence of component damage caused by electro static discharge(ESD).

1. Immediately before handling any semiconductor component or semiconductor-equipped assembly, drain

off any ESD on your body by touching a known earth ground. Alternatively, obtain and wear a commercially

availabel discharging ESD wrist strap, which should be removed for potential shock reasons prior to

applying power to the unit under test.

2. After removing an electrical assembly equipped with ES devices,place the assembly on a conductive

surface such as alminum foil, to prevent electrostatic charge buildup or exposure of the assembly.

3. Use only a grounded-tip soldering iron to solder or unsolder ES devices.

4. Use only an anti-static solder removal device. Some solder removal devices not classified as anti-static

(ESD protected)can generate electrical charge sufficient to damage ES devices.

5. Do not use freon-propelled chemicals. These can generate electrical charges sufficient to damage ES

devices.

6. Do not remove a replacement ES device from its protective package until immediately before you are

ready to install it.(Most replacement ES devices are packaged with leads electrically shorted together by

conductive foam, alminum foil or comparable conductive material).

7. Immediately before removing the protective material from the leads of a replacement ES device, touch

the protective material to the chassis or circuit assembly into which the device will be installed.

Caution

Be sure no power is applied to the chassis or circuit, and observe all other safety precautions.

8. Minimize bodily motions when handling unpackaged replacement ES devices. (Otherwise harmless motion

such as the brushing together of your clothes fabric or the lifting of your foot from a carpeted floor can

generate static electricity(ESD).

notice (1885x323x2 tiff)