2.13.26. Display Data High register ............................................................................................................33

2.13.27. Display Control Left register.........................................................................................................33

2.13.28. Display Control Right register.......................................................................................................33

2.13.29. Location Monitor Address Low register........................................................................................34

2.13.30. Location Monitor Address High register.......................................................................................34

2.13.31. Location Monitor Control register.................................................................................................34

2.13.32. BA Rotary Switches Status register...............................................................................................34

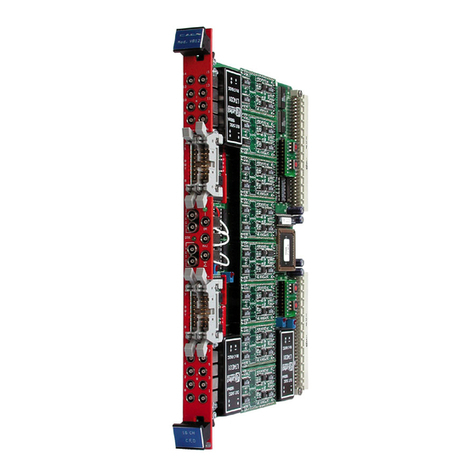

3. TECHNICAL SPECIFICATIONS................................................................................................................35

3.1. PACKAGING............................................................................................................................................35

3.2. POWER REQUIREMENTS..........................................................................................................................35

3.3. FRONT PANEL.........................................................................................................................................36

3.4. V2718 AND A2818/A3818 EXTERNAL COMPONENTS.............................................................................37

3.4.1. V2718 connectors..........................................................................................................................37

3.4.2. V2718 buttons ...............................................................................................................................37

3.4.3. A2818 connectors..........................................................................................................................37

3.4.4. A3818 connectors..........................................................................................................................37

3.5. V2718 INTERNAL HARDWARE COMPONENTS..........................................................................................38

3.5.1. Switches.........................................................................................................................................38

3.5.2. Internal jumpers.............................................................................................................................40

3.6. PROGRAMMABLE INPUT/OUTPUT...........................................................................................................41

3.6.1. Timer & Pulse Generator...............................................................................................................41

3.6.2. Scaler.............................................................................................................................................42

3.6.3. Coincidence...................................................................................................................................42

3.6.4. Input/Output Register ....................................................................................................................42

3.7. I/O INTERNAL CONNECTIONS..................................................................................................................43

3.8. VME DATAWAY DISPLAY......................................................................................................................44

3.9. FIRMWARE UPGRADE..............................................................................................................................46

3.10. V2718 TECHNICAL SPECIFICATIONS TABLE ............................................................................................49

4. SOFTWARE OVERVIEW ...........................................................................................................................50

4.1. SOFTWARE USER INTERFACE .................................................................................................................50

4.1.1. Software User Interface: Installation .............................................................................................50

4.1.2. Hardware Installation ....................................................................................................................51

4.1.3. CAENVME Demo: The Main Menu.............................................................................................52

4.1.4. Software User Interface: I/O Setting Menu –VME Settings.........................................................53

4.1.5. Software User Interface: I/O Setting Menu –Pulser .....................................................................53

4.1.6. Software User Interface: I/O Setting Menu –Scaler .....................................................................54

4.1.7. Software User Interface: I/O Setting Menu –Location Monitor...................................................54

4.1.8. Software User Interface: I/O Setting Menu –Input.......................................................................55

4.1.9. Software User Interface: I/O Setting Menu –Output ....................................................................55

4.1.10. Software User Interface: I/O Setting Menu –Display...................................................................55

4.1.11. Software User Interface: I/O Setting Menu –About .....................................................................56

4.2. CAENVMELIB INTRODUCTION.............................................................................................................56

4.3. CAENVMELIB 1.X DESCRIPTION ..........................................................................................................56

4.3.1. CAENVME_SWRelease...............................................................................................................56

4.3.2. CAENVME_Init............................................................................................................................57

4.3.3. CAENVME_BoardFWRelease .....................................................................................................57

4.3.4. CAENVME_End...........................................................................................................................57

4.3.5. CAENVME_ReadCycle................................................................................................................58

4.3.6. CAENVME_MultiRead ................................................................................................................58

4.3.7. CAENVME_RMWCycle ..............................................................................................................59

4.3.8. CAENVME_WriteCycle...............................................................................................................59

4.3.9. CAENVME_MultiWrite ...............................................................................................................60